PCI-SIG Finalizes PCIe 6.0 Specification

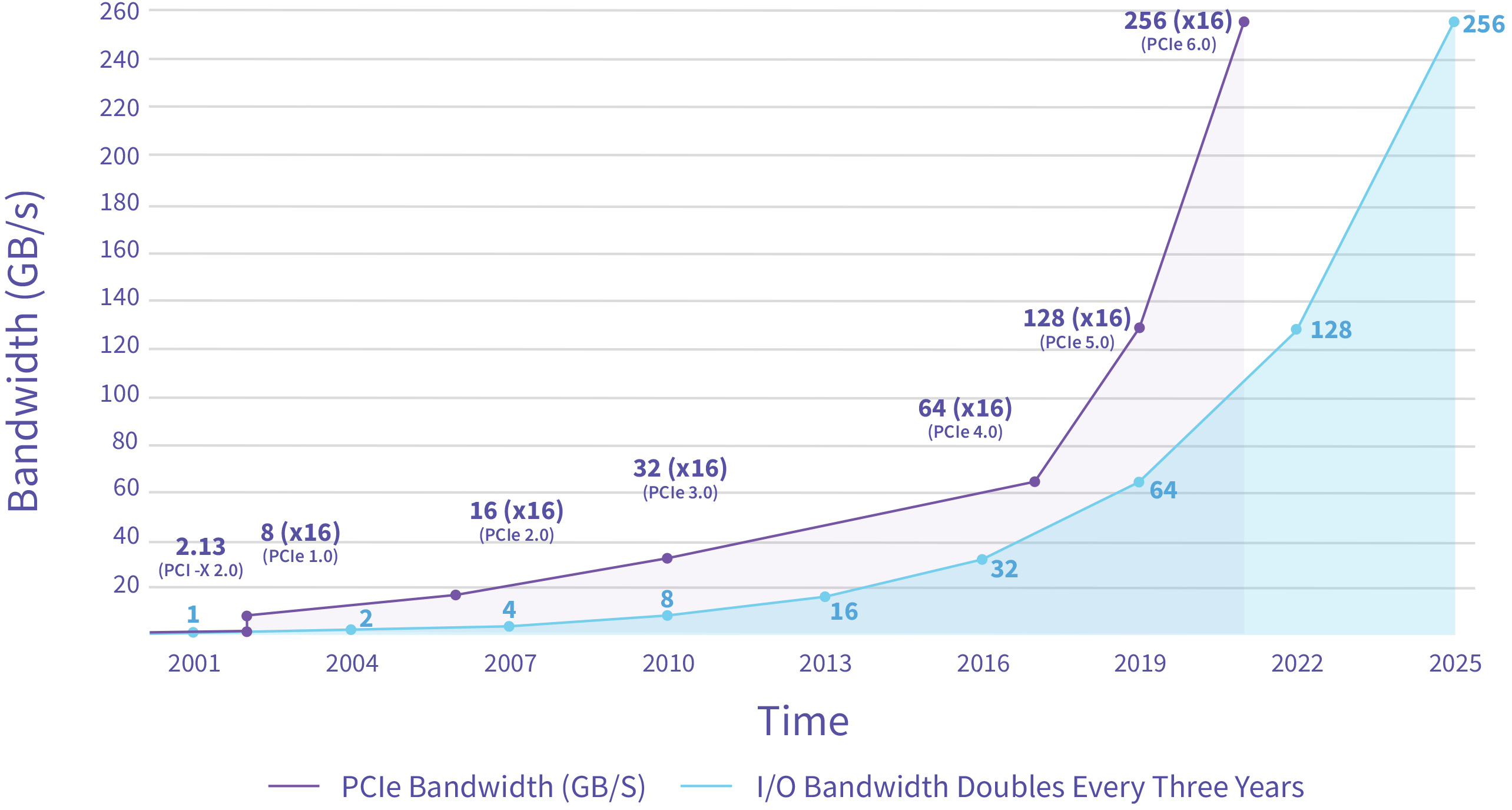

PCIe 6.0: 64 GT/s per Lane, 256 GB/s with 16 Lanes

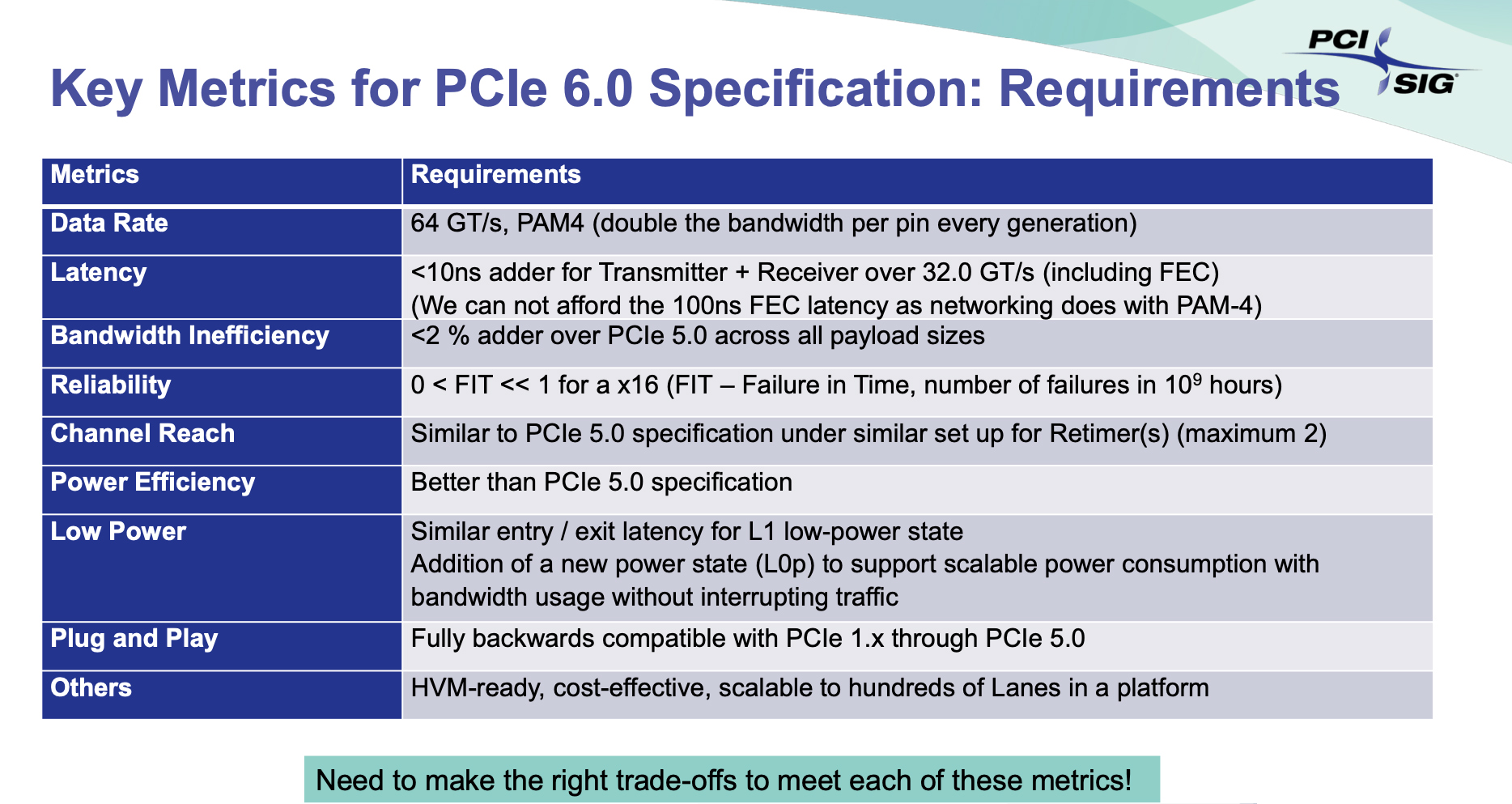

PCI-SIG has published the final specification of the PCIe Gen6 standard, an update that boosts the data transfer rate of the interface to 64 GT/s per lane. To hit such high speeds, as well as maintain reliability and efficiency, PCIe 6.0 adopts pulse amplitude modulation with four levels (PAM-4) of signalling forward error correction (FEC). Given all the complexities of PCIe Gen6, it will initially be used for applications insensitive to costs, such as high-performance computing and data centers.

PCIe 6.0 is a significant departure from PCIe 5.0. Not only because of its higher transfer rate (which provides a total bandwidth of 256 GB/s over 16 lanes in both directions) but mainly because it brings features such as PAM-4 signalling previously used mainly for high-end networking technologies, and introduces Flit (flow control unit) based encoding for PAM-4, FEC, Cyclic Redundancy Check (CRC), and L0p power states.

Maintaining signal integrity at 64 GT/s with PAM-4 is rather hard, since this method of encoding is more prone to errors than the binary non-return-to-zero (NRZ) encoding traditionally used by PCIe. Since PCIe is an interface for internal connectivity, it not only has to be fast, but low latency too. To that end, PCIe 6.0's FEC method, further enhanced with CRC, has to ensure low latency while being robust enough to fix the inevitable bit errors that happen at such high speeds when using PAM-4.

While PCIe 6.0 is the most significant revamp of the PCI Express standard since 3.0 in 2010, PCIe 6.0-supporting hosts will retain backwards compatibility with existing cards.

The introduction of PAM-4 (and everything it requires) will inevitably increase the cost of PCIe 6.0 implementation, and will make PCIe 6.0 controllers and other physical layers more power hungry than PCIe 5.0. The good news is that the overall power efficiency of the new technology promises to be higher than that of PCIe 5.0, so it will make sense for many applications to move over to PCIe 6.0, especially in cases where the number of lanes can be reduced.

But the implementation of PCIe 6.0 in silicon is only one part of the challenge. Signal transmission over its printed circuit boards (PCBs) will have to be optimized for crosstalk, loss, reflections, and signal integrity. In many cases retimers will have to be used for PCIe 6.0 applications, but only two retimers are allowed by the standard.

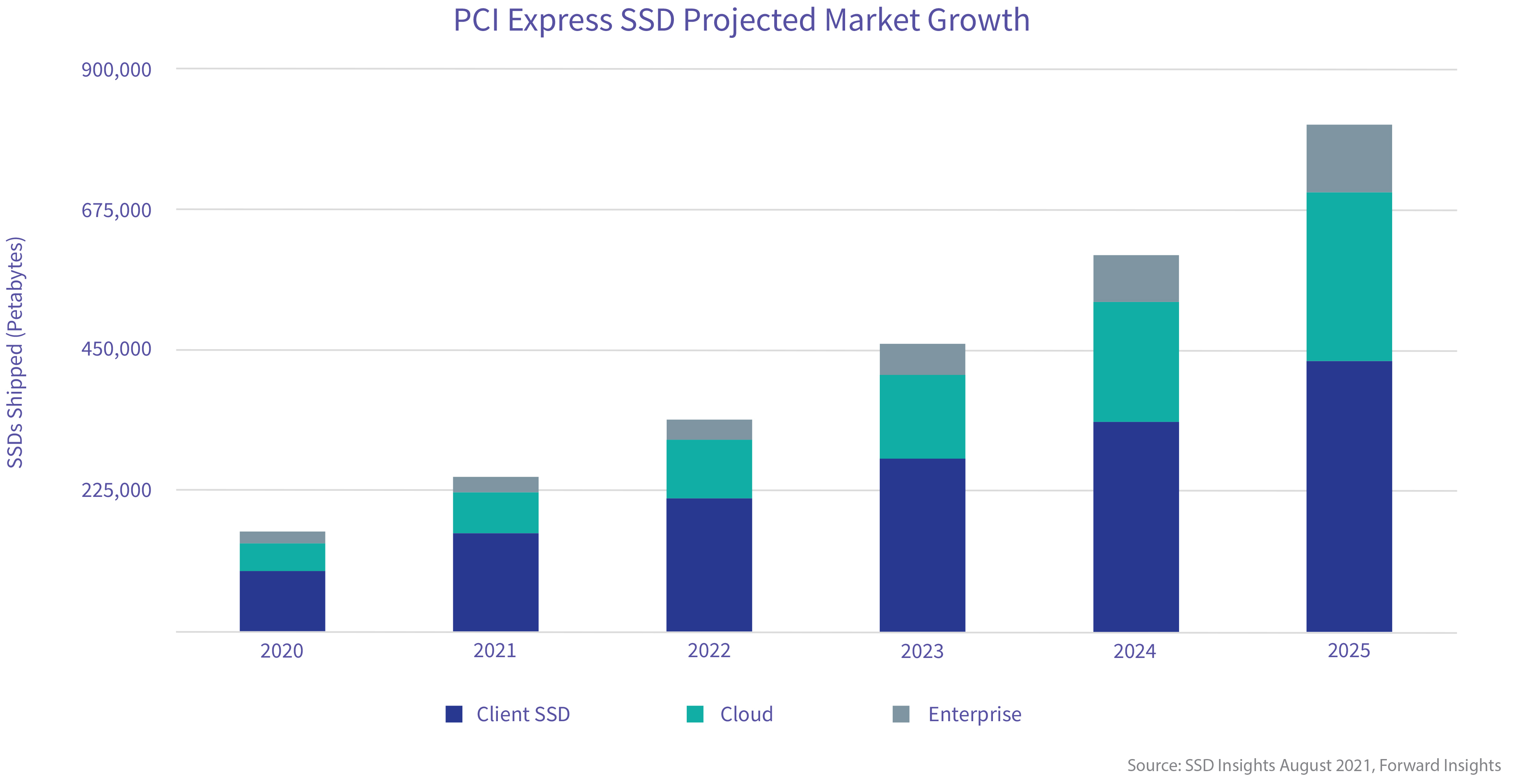

In general, because of implementation complexities, PCIe 6.0 will initially only be used for applications that can benefit the most from it, which includes AI and machine learning as well as HPC accelerators, datacenter applications like high-end SSDs, automotive, IoT, and aerospace/military applications that can benefit from low lane count and maximum bandwidth.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

"With the PCI Express SSD market forecasted to grow at a CAGR of 40% to over 800 exabytes by 2025, PCI-SIG continues to meet the future needs of storage applications," said Greg Wong, Founder and Principal Analyst at Forward Insights. "With the storage industry transitioning to PCIe 4.0 technology and on the cusp of introducing PCIe 5.0 technology, companies will begin adopting PCIe 6.0 technology in their roadmaps to future-proof their products and take advantage of the high bandwidth and low latency that PCI Express technology offers."

Companies such as Cadence and Synopsys have been offering preliminary implementations of PCIe 6.0 for several quarters now, so there are probably companies who are already developing PCIe Gen6-supporting chips. We doubt that these products will be launched this year, as 2022's server and client platforms only support PCIe Gen 5. However, it is possible that PCIe Gen 6 devices will make it to the market in 2023 or 2024.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.