PCIe 6.0 Ready for Chip Designs: Synopsys Unveils Complete PCI Express 6.0 Solution

PCIe 6.0 at 64 GT/s with PAM4 encoding on-track for 2021 finalization

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

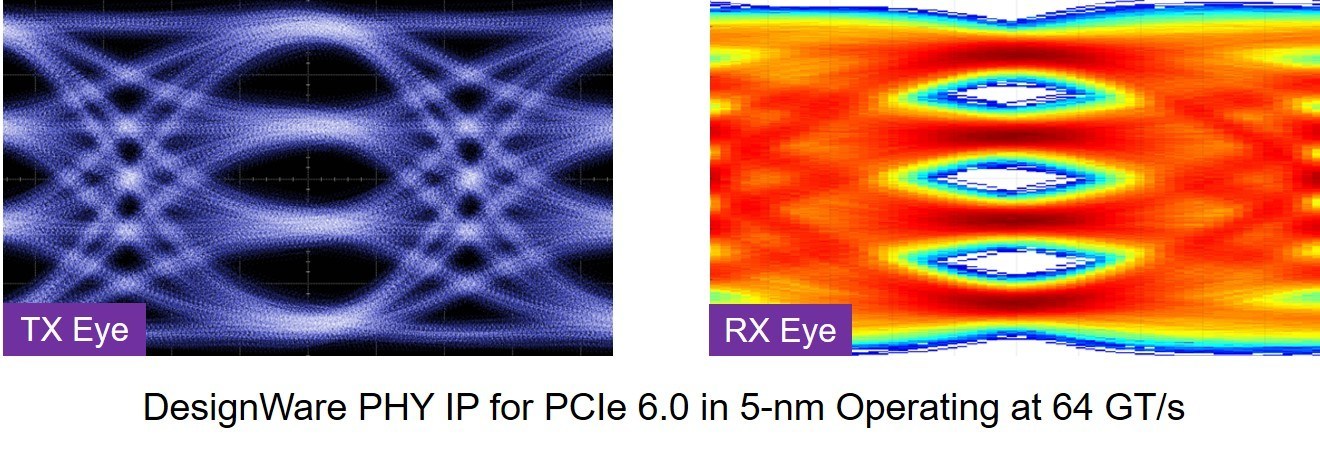

The final PCIe 6.0 specification is still months away, but the complete draft released about five months ago allows chip designers and IP developers to start implementing the new technology into their products as no new features will be added or modified. This week Synopsys introduced the industry's first complete PCIe 6.0 IP solution that allows chip creators to integrate the new interface into their designs to be made using a 5-nm fabrication process.

Synopsys' DesignWare IP package for PCIe 6.0 includes a controller (with a Synopsys interface or optional Arm's AMBA 5/4/3 AXI interfaces), physical interface (PHY), and verification IP. The solution that Synopsys offers allows chip designers to throw the controller IP and physical interface into their 5-nm design and then verify that everything works correctly using the verification IP provided. For example, designers of ASICs for AI as well as HPC applications, GPUs, SSD controllers, and other bandwidth-sensitive applications that require the high bandwidth that a PCIe 6.0 interface can provide.

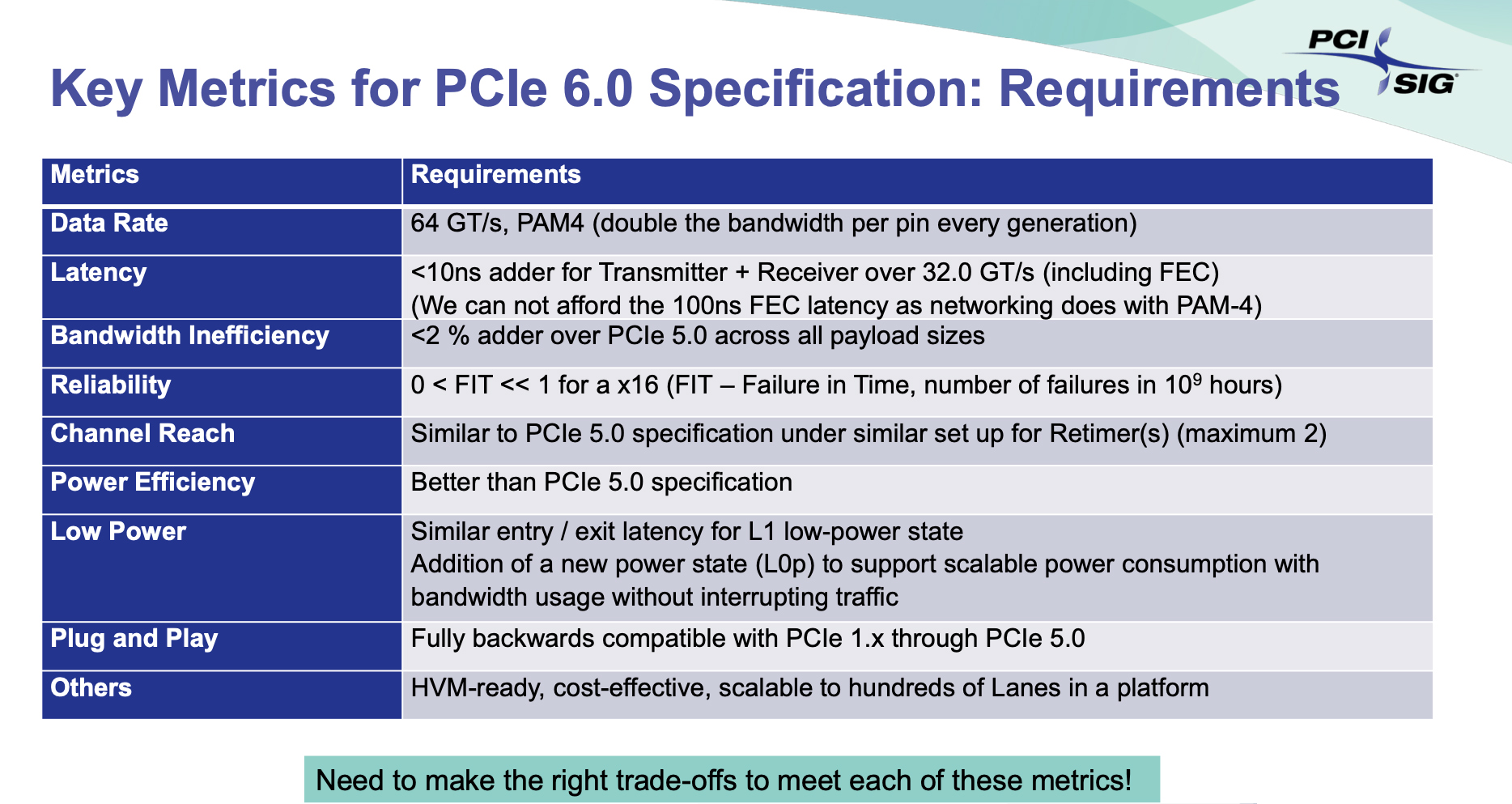

How much bandwidth? Up to 128 GB/s over an x16 interface — in each direction. That means a PCIe 6.0 solution could potentially transfer up to 256 GB/s of data. Yes, please, we'll take two!

The controller fully supports a data transfer rate of up to 64 GT/s per pin, up from 32 GT/s in case of PCIe 5.0 and 16 GT/s in case of PCIe 4.0. It also supports pulse amplitude modulation with four levels (PAM4) signaling, low-latency forward error correction (FEC), FLIT mode, and L0p power state — all key new features of PCIe 6.0. On top of that, Synopsys' DesignWare PCIe 6.0 controller also supports Synopsys' own adaptive DSP algorithms that optimize analog and digital equalization to reduce power by 20% across chip-to-chip, riser card, and backplane interfaces.

Synopsys says that the architecture of its PCIe 6.0 controller and physical interface are placement-aware to minimize package crosstalk at high data transfer rates. Furthermore, the company claims that it uses an optimized datapath to ensure ultra-low latency.

"Advanced cloud computing, storage and machine learning applications are transferring significant amounts of data, requiring designers to incorporate the latest high-speed interfaces with minimal latency to meet the bandwidth demands of these systems," said John Koeter, senior vice president of marketing and strategy for IP at Synopsys. "With Synopsys' complete DesignWare IP solution for PCI Express 6.0, companies can get an early start on their PCIe 6.0-based designs and leverage Synopsys' proven expertise and established leadership in PCI Express to accelerate their path to silicon success."

It's only in the past 18 months that we've seen consumer hardware — GPUs and M.2 SSDs — supporting PCIe 4.0, with Nvidia adding support for Gen4 with Ampere starting last September. We've got some time before PCIe 5.0 starts to show up in the best graphics cards and best SSDs, not to mention motherboards, but PCI-SIG is already basically finished with the next iteration. How much will the increased bandwidth matter for storage and graphics workloads? For home users, probably not much at all. These high-speed interfaces primarily target data center and supercomputer workloads, and it will likely be many years before consumer hardware needs this much speed.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

Jim90 As always, most excellent to see progress!Reply

Would be equally excellent, though, to see the inevitable bottlenecks being tackled at the same time - everything else in that connected chain would keep up, in an ideal world. -

InvalidError Reply

Sure, skip to 6.0 when 4.0 is already considerably more power-hungry than 3.0 so we can have chipsets that require tower coolers and CPUs that require multiple VRM phases dedicated to bus power :)samopa said:So, can we just skip PCIE 5.0 entirely and directly implement PCIE 6.0 ?

I'm ok with waiting for that stuff to get cheaper and more power-efficient.