PCIe 6.0 Specification Hits Milestone: Complete Draft Is Ready

PCIe 6.0 at 64 GT/s & PAM4 encoding on-track for 2021 finalization

The PCIe 6.0 technology this week achieved an important milestone as PCI-SIG released version 0.7 of the specification. The release of the new 'complete draft' specification indicates that the technology has been defined and its electrical specifications have been validated using test chips. Essentially, it means that PCIe 6.0 is ready and functional, so it is only a matter of time before it is finalized sometime in 2021.

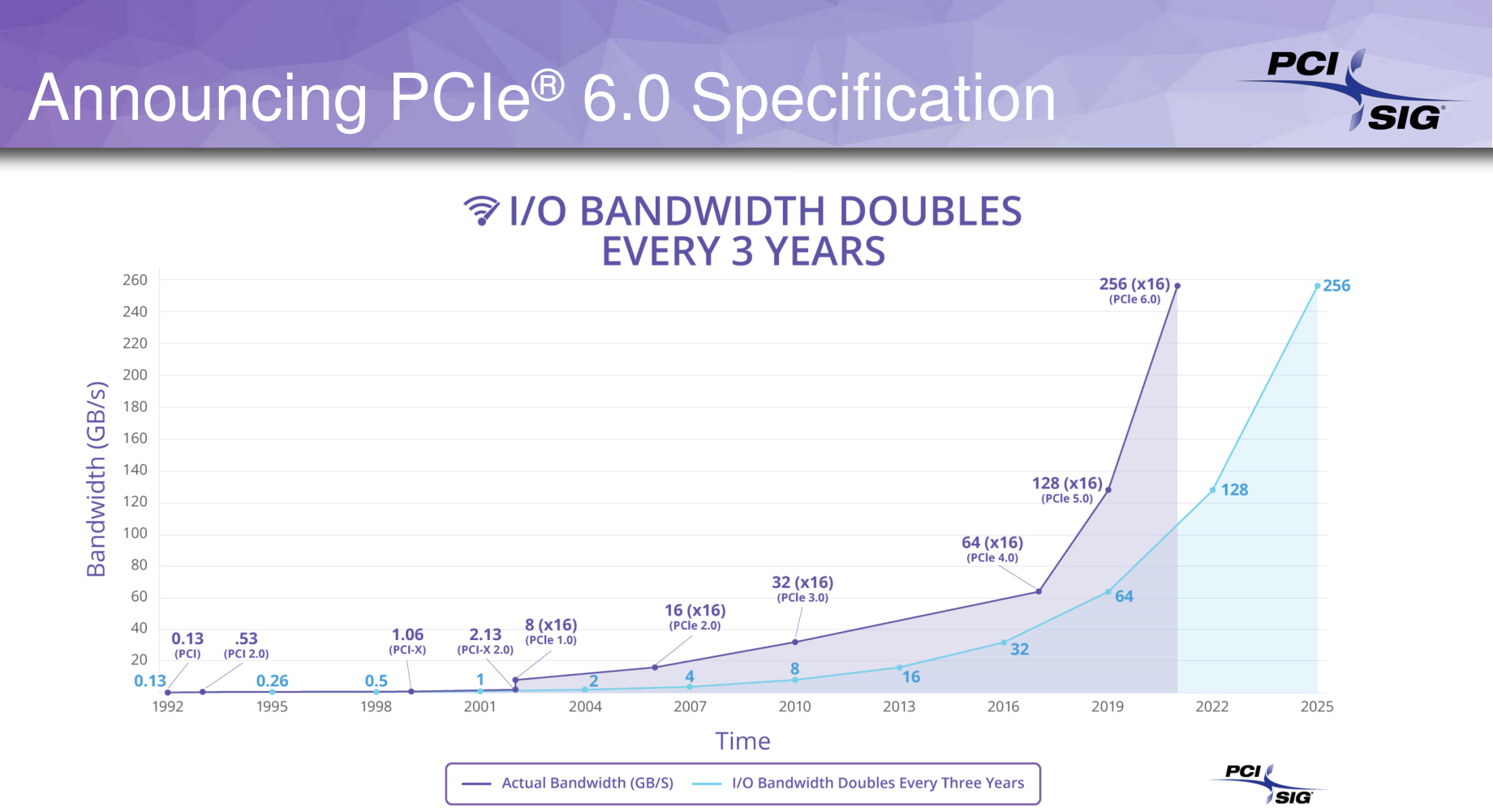

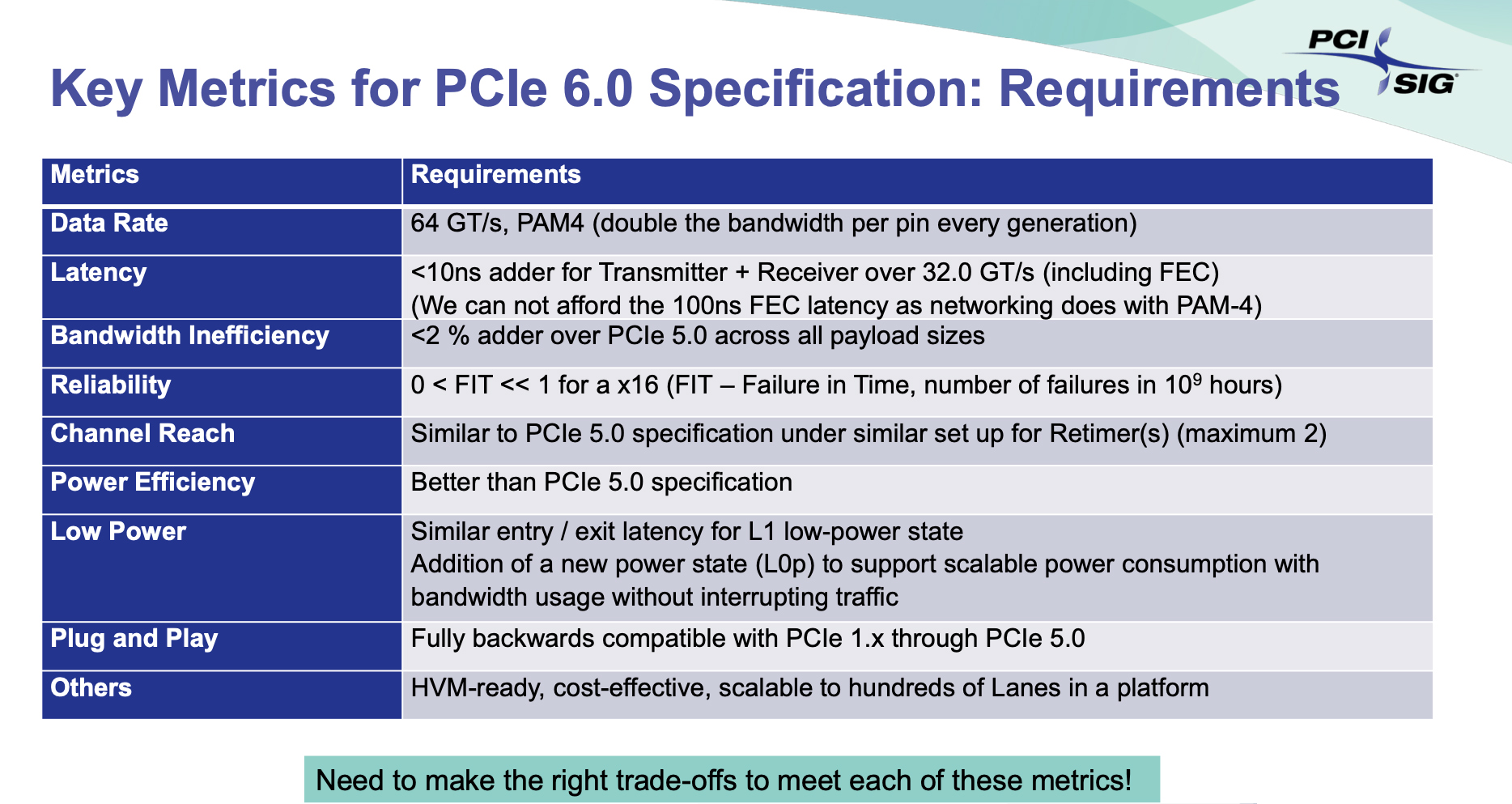

PCIe 6.0 will increase data transfer rate to 64 GT/s per pin, up from 32 GT/s in case of PCIe 5.0 and 16 GT/s in case of PCIe 4.0. In a bid to increase data transfer rate and bandwidth, the new interface adopted pulse amplitude modulation with four levels (PAM4) signaling, which is also used for high-end networking technologies like InfiniBand as well as GDDR6X memory. In addition, PCIe 6.0 uses low-latency forward error correction (FEC) to ensure high efficiency. In general, PCIe 6.0 is a major step forward for the interface and since it introduces a number of innovations, in a bid to bring it to the market on time a very disciplined execution on the standard development is required.

The release of the PCIe 6.0 spec version 0.7 is a particularly important one since after this release no new features can be added and electrical specifications of the technology have been validated using test chips. In fact, at this stage, various companies may have actual implementations of the new bus ready (but not necessarily announced).

Each PCI Express specification (just like any other spec designed by PCI-SIG) features five primary checkpoints:

- Version 0.3: Concept. This draft describes general goals and approaches that will be used to achieve them. As far as PCIe 6.0 is concerned, these general things are 64 GT/s data transfer rate, PAM4 signaling, and FEC.

- Version 0.5: the First Draft. This release must fully address the goals set in the draft 0.3, it also includes all architectural aspects and requirements. Furthermore, it contains feedback from various interested parties and at this point members of PCI-SIG can add capabilities to the specification being developed.

- Version 0.7: the Complete Draft. This version must have a complete set of functional requirements and methods defined because no new features can be added after this release. Furthermore, electrical specifications must have been validated using test chips. At this point, it is possible for PCI-SIG members to propose different implementations of a new interface.

- Version 0.9: the Final Draft. At this point PCI-SIG members are performing internal reviews of the technology for their intellectual property and patents. Meanwhile, no functional changes are permitted.

- Version 1.0: the Final release. Starting from this version, all changes and enhancements have to go through errata documentation and engineering change notices (ECNs).

PCI-SIG released version 0.5 of the PCIe 6.0 specification in late February, around eight months ago. If everything goes as planned, the new technology will be finalized sometime in the second half of 2021. Do not expect the new interface to hit the market any time soon. PCI-SIG published the final version of PCIe 5.0 in late May 2019, but the first platforms from companies like AMD and Intel that will support the technology will arrive only in late 2021. That said, if PCI-SIG finalizes the PCIe 6.0 technology in the second half of 2021 (a year from now sounds more likely, but we are speculating), expect supporting platforms to arrive sometime in late 2023 or in 2024.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

Makaveli I don't think we will see PCie 6.0 in the time frame they are suggesting on desktops maybe in the server space.Reply -

hotaru251 pcie 5.0 was delayed by a long time iirc.Reply

and it was assumed to be a very short lived one due to that. -

InvalidError Reply

PCIe 4.0 is already stretching the limits of what affordable PCBs can manage, so I wouldn't be surprised if even 5.0 was slow to gain traction in the mainstream due to the overhead cost of either putting retimers everywhere (4.0 can still avoid retimers for the nearest slot) or using much more expensive PCB materials.Makaveli said:I don't think we will see PCie 6.0 in the time frame they are suggesting on desktops maybe in the server space.

I wouldn't be surprised if PCIe went optical before 6.0 gets to mainstream.