PCI-SIG Releases Final PCIe 5.0 Specification

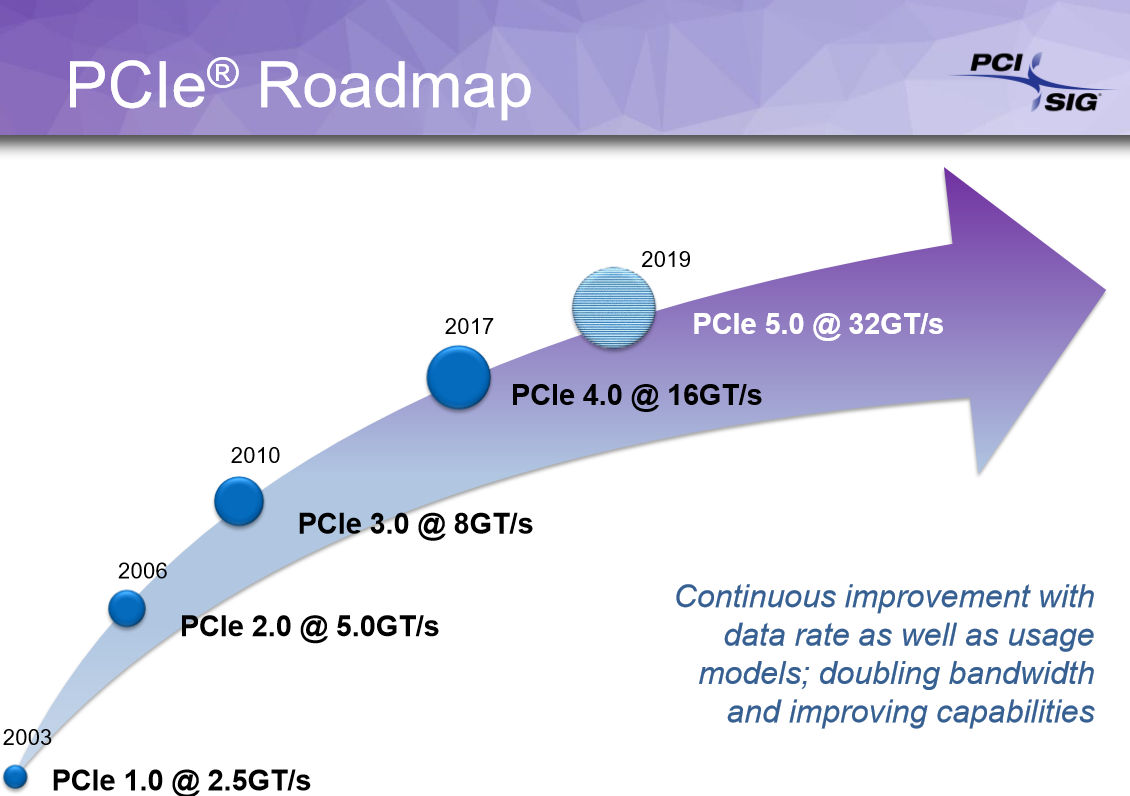

The PCI-SIG organization today released the final PCI Express 5.0 specification. The new interconnect standard doubles the bandwidth to 32 GT/s per lane less than two years after PCIe 4.0 debuted. PCI-SIG members can download the full specification from the organization's website.

PCI-SIG Chairman and President Al Yanes said the standard was completed in 18 months. "New data-intensive applications are driving demand for unprecedented levels of performance," Yanes said in the announcement. "The PCIe architecture will continue to stand as the [de facto] standard for high performance I/O for the foreseeable future."

Via an x16 configuration, PCIe 5.0 allows up to 128 GB/s bandwidth, twice that of PCIe 4.0. The PCIe 5.0 architecture also implements electrical changes to improve signal integrity and mechanical performance of connectors. Like prior versions, the standard maintains backwards compatibility with earlier PCIe versions, meaning earlier versions will continue to work over PCIe 5.0 interfaces, although they won’t be able to leverage the higher speed. Lastly, it includes a new backwards compatible CEM connector targeted for add-in cards.

Article continues belowThe first meaningful PCIe 4.0 products for consumers are only being released this year, most notably the CPUs and GPUs from AMD, which most likely means that PCIe 5.0 will be a relatively fast follow-up. Intel has already announced that its Agilex FPGA will support PCIe 5.0, and its cache-coherent Compute Express Link (CXL) relies on PCIe 5.0. The company plans to release CXL products, which could be the first to support PCIe 5.0, in 2021.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.