Rambus Demonstrates HBM2E Running at 4 Gbps: 512 GB/s per HBM2E Stack

Rambus advances HBM2E performance beyond what is officially possible

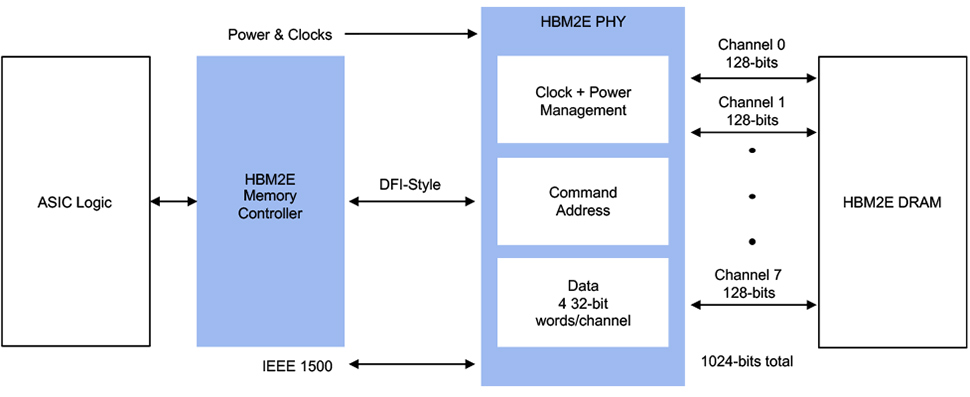

Rambus has demonstrated that its HBM2E solution, which consists of a memory controller and a verified 1024-bit PHY, can operate at a whopping 4.0 Gbps data transfer rate per pin. The demonstration is meant to prove potential clients that the HBM2E solution can scale and offer a 25% higher peak bandwidth than is officially defined by JEDEC’s HBM2E standard.

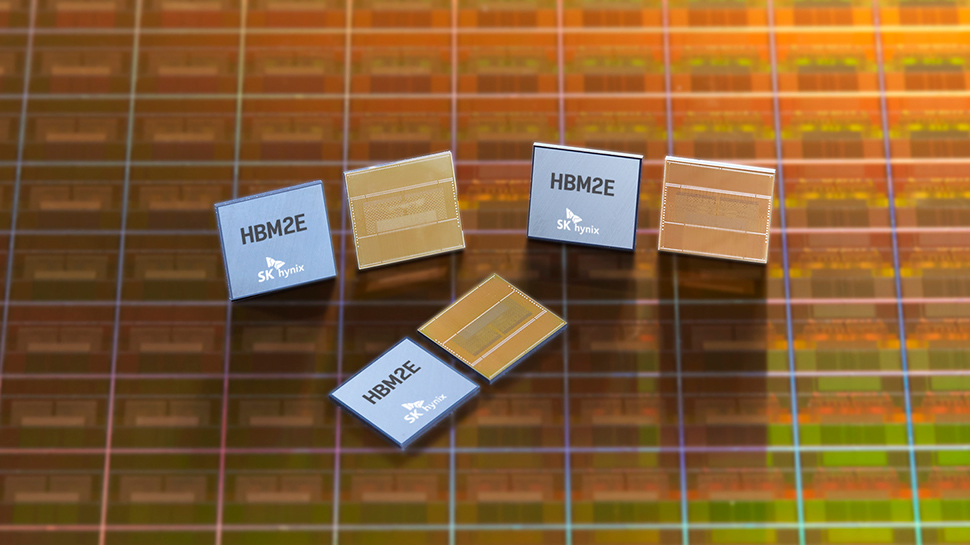

Formally, JEDEC’s HBM2E specification tops at a 3.2 Gbps per-pin data transfer rate, but SK Hynix recently started to mass-produce 16 GB 1024-pin known-good stacked dies (KGSDs) rated for a 3.6 Gbps operation. To take advantage of such stacks, designers of ASICs need a controller and a verified physical interface that can support such a high data rate without PHY voltage overdrive.

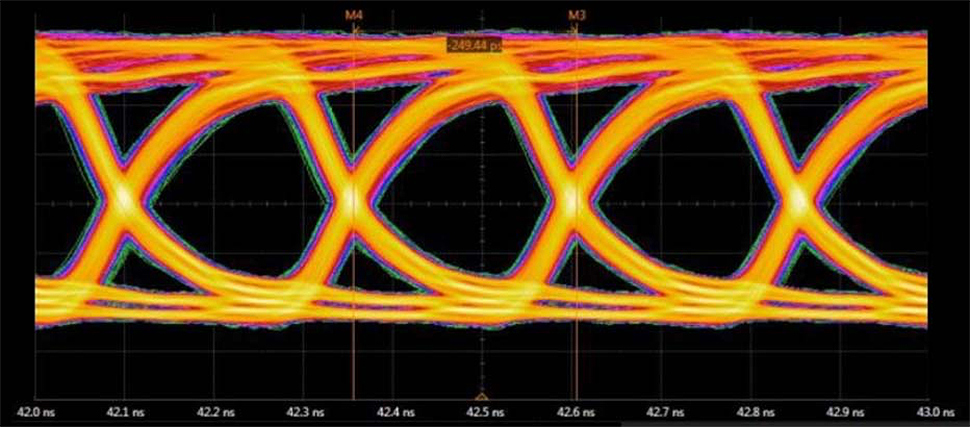

To demonstrate capabilities of its HBM2E solution, Rambus asked Alchip, a contract developer of ASICs, to implement its HBM2E controller and PHY using TSMC’s N7 process technology and 2.5D CoWoS (Chip-on-Wafer-on-Substrate) advanced packaging method. The result has exceeded expectations. According to a transmit eye screenshot published by Rambus, the subsystem (featuring a test chip and SK Hynix’s HBM2E stacks) worked fine and the signals were clean even at 4.0 Gbps. Rambus says that the memory subsystem ran at 4 Gbps without PHY voltage increase.

Article continues belowAt 3.2 Gbps, a 1024-pin HBM2E KGSD provides a peak bandwidth of 410 GB/s (which translates to 2.46 TB/s for a six-piece HBM2E subsystem), but at 4.0 Gbps it delivers a whopping 512 GB/s bandwidth per stack.

At present, only SK Hynix offers 3.6 Gbps HBM2E KGSDs and it is unclear if and when DRAM makers intend to increase data rates of their HBM2E stacks to 4.0 Gbps. But Rambus says that for designers of upcoming bandwidth-hungry ASICs for artificial intelligence (AI) or high-performance computing (HPC) applications it is important to know how well a particular type of memory scales.

The Rambus HBM2E controller core is DFI 3.1 compatible and supports AXI, OCP, and proprietary interfaces to connect to ASIC logic. The controller can work with channel densities of up to 24 Gb and 12-Hi KGSDs, thus supporting memory stacks of up to 36 GB. In theory, chip designers can build a 2.5D ASIC with 144 GB of HBM2E memory (using six HBM2E stacks) featuring a peak bandwidth of 3 TB/s.

“Rambus guarantees HBM2E performance to 3.6 Gbps, but you’ve got design headroom because we’ve silicon demonstrated performance up to 4.0 Gbps,” said Frank Ferro, senior director of product marketing, IP Cores at Rambus

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

Jerry_W14 Reply

I completely agree with you. I was willing to give AMD $1K for Big Navi with HBM2E, Very reluctant too now. GDDR6 is a poor replacement for graphics memory in my book. I love my Vega 64 I regularly use High bandwidth cache playing games. I get to use 16Gb w/Vega. I've tuned it to my power and performance liking. I do have Navi now but it doesn't tweak the same.nofanneeded said:I just wish HBM2E be cheaper to compete against GDDR6X in the GPU market. -

spongiemaster Reply

16GB of HBM2 did wonders for the Radeon VII. Made it almost as fast as the 2 year old 11GB GDDR5X 1080Ti in gaming.Jerry_W14 said:I completely agree with you. I was willing to give AMD $1K for Big Navi with HBM2E, Very reluctant too now. GDDR6 is a poor replacement for graphics memory in my book. I love my Vega 64 I regularly use High bandwidth cache playing games. I get to use 16Gb w/Vega. I've tuned it to my power and performance liking. I do have Navi now but it doesn't tweak the same. -

Homer J. Reply

Yeah, that must be why AMD calmly removed Radeon VII from the market. In case you are unaware, the Radeon VII has been gone from the market for over 6 months. It sold so "incredibly" well.spongiemaster said:16GB of HBM2 did wonders for the Radeon VII. Made it almost as fast as the 2 year old 11GB GDDR5X 1080Ti in gaming.