Renesas Launches First PCIe 6.0 Chips for Next-Gen Devices

Renesas introduces first PCIe Gen6 clock buffers and multiplexers.

Renesas has introduced the industry's first lineup of clock buffers and multiplexers that meet strict PCIe 6.0 specifications. The new devices will let companies build motherboards and other devices that should comply with PCIe 6.0 requirements when it comes to performance and signal integrity, but are also compatible with PCIe 5.0 applications.

Renesas is adding 11 new RC190xx clock buffers and four new RC192xx multiplexers that have an additive jitter of only 4fs RMS, which is virtually noiseless, a feature that's extremely important for PCIe Gen6 applications. Also, the new clock buffers feature a 1.4 ns in-out delay, 35ps out-out skew, and -80dB power supply rejection ratio (PSRR) at 100kHz. The new chips complement Renesas's low-jitter 9SQ440, 9FGV1002 and 9FGV1006 clock generators and enable the company to offer a complete PCIe 6.0 timing solution.

A 256 GBps bi-directional bandwidth over a 16-lane interface or a 64 GBps bi-directional bandwidth over a 4-lane interface will hardly be required by consumer graphics cards or solid-state drives any time soon. But in the data center, bandwidth is everything. Meanwhile, ultra-complex PCIe Gen 6 circuit design and tests will take time, so the earlier hardware developers start building new products, the better. This could enable developers of next-generation server platforms to start designing motherboards, accelerators, network cards and SSDs.

"By delivering the first discrete timing solution for PCIe Gen 6, Renesas is enabling customers to develop the next-generation of high-performance systems," said Rich Wawrzyniak, principal analyst for Semico Research in a statement from Renesas. "It will be interesting to see the innovative implementations that result from this new capability, especially when considering how solutions for the emerging chiplet market are starting to evolve, with the need for increasing speed and bandwidth as an underlying constant."

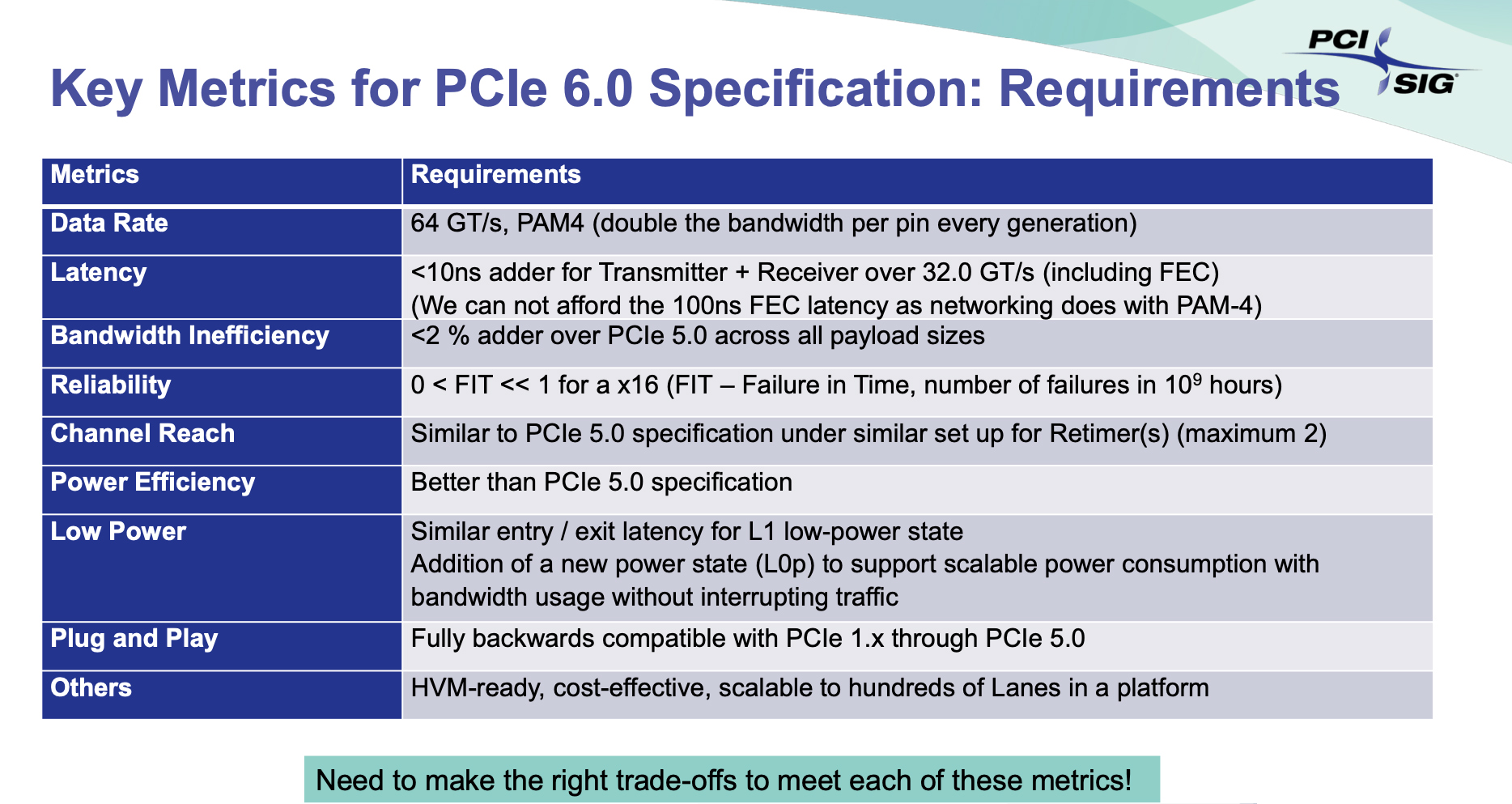

To boost a total bandwidth of a 16-lane PCIe slot to 256 GBps in both directions, the PCIe Gen 6 specification increases data transfer rate to 64 GTps and adopts pulse amplitude modulation with four levels (PAM-4) of signaling as well as forward error correction (FEC). A very high data transfer rate and a new signal encoding method not only require new logical enhancements to the specification (e.g., FEC further enhanced with CRC), but also increase requirements for quality of clock signals —clock jitter performance of a PCIe Gen 6 subsystem should be less than 100fs RMS. This is where the all-new clock buffers (also called clock drivers) and multiplexers come into play.

The operation of a circuit has to be synchronized, but sometimes the same-sourced clock signal arrives at different registers at different times due different path lengths between two clock paths, or because of gated or rippled clocks. This phenomenon is called clock skew, or timing skew, and can cause hold time violation errors. Clock buffers allow for distributing clocks synchronously and efficiently by preserving clock properties of the input signal, and minimization of the additive jitter noise is particularly important for PCIe 6.0 subsystems.

A multiplexer is essentially a multiple-input and single-output switch that is used for signal distribution. Since we are dealing with a 64 GTps data transfer rate, MUXes have to handle this signal rate and ensure clean signals, which is why brand-new multiplexers for PCIe Gen 6 applications are required.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

"PCIe Gen6 timing will be at the heart of new equipment in data centers, high-speed networking and other applications, "said Zaher Baidas, Vice President of the Timing Products Division at Renesas. "As we have done for preceding generations, Renesas is providing customers with the first timing solution to enable these new, higher-performance systems. Our customers know that we have the technical expertise and market knowledge to ensure that their products will be able to meet future requirements as well."

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

spentshells well, it's nice to see tech moving along, I can not figure out why power requirements keep going up. while pcie 3 bandwidth is still just being surpassed.Reply

tell your mom I saw her in 4k using pcie 3 @ 16 X -

hotaru251 Reply

the rule they decided on was 2x prior pcie speeds.spentshells said:I can not figure out why power requirements keep going up.

those speeds need more pwr. -

InvalidError Reply

Maybe in the consumer space. In the enterprise space, once SSDs became economically viable. PCIe went from 3.0 being vastly sufficient to 4.0 being too little too late, hence the rush to 5.0 and accelerated time table to 6.0.spentshells said:well, it's nice to see tech moving along, I can not figure out why power requirements keep going up. while pcie 3 bandwidth is still just being surpassed.

In the consumer space, we're mostly seeing the PCIe bandwidth crunch on lower-end GPUs that need to rely more heavily on system memory. In the not-so-distant-future, we may also see it with DirectStorage titles needing more PCIe bandwidth to cache more higher-definition assets in system memory. -

hotaru.hino Reply

Transistors dissipate power when they're switching states. The more times it switches, the more power it dissipates. See https://semiengineering.com/knowledge_centers/low-power/low-power-design/power-consumption/spentshells said:well, it's nice to see tech moving along, I can not figure out why power requirements keep going up. while pcie 3 bandwidth is still just being surpassed.

tell your mom I saw her in 4k using pcie 3 @ 16 X -

InvalidError Reply

Thankfully, power goes down as operating and signalling voltages and parasitic capacitances go down. Give this stuff two or three product generations to mature on all fronts, then we'll probably get 6.0 performance squeezed in the same power budgets as 4.0 today. First-gen 4.0 products were power hogs too.hotaru.hino said:Transistors dissipate power when they're switching states. The more times it switches, the more power it dissipates. -

spentshells Reply

thank you Ill check that outhotaru.hino said:Transistors dissipate power when they're switching states. The more times it switches, the more power it dissipates. See https://semiengineering.com/knowledge_centers/low-power/low-power-design/power-consumption/