Seagate Develops Own RISC-V Cores for Storage Controllers

The path to 50TB HDDs: Seagate to use own RISC-V cores for custom SoCs.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

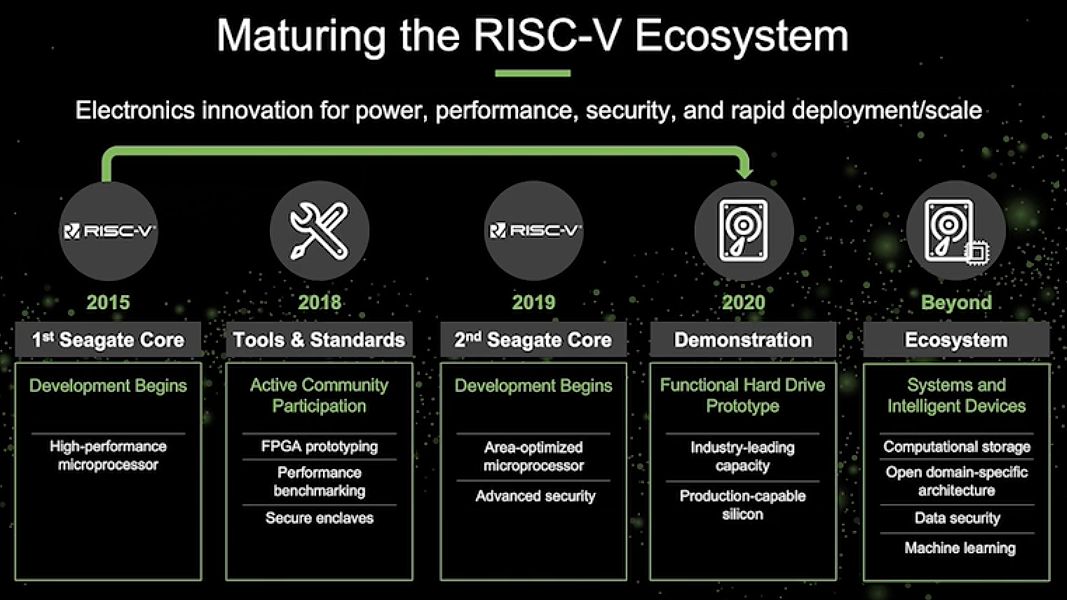

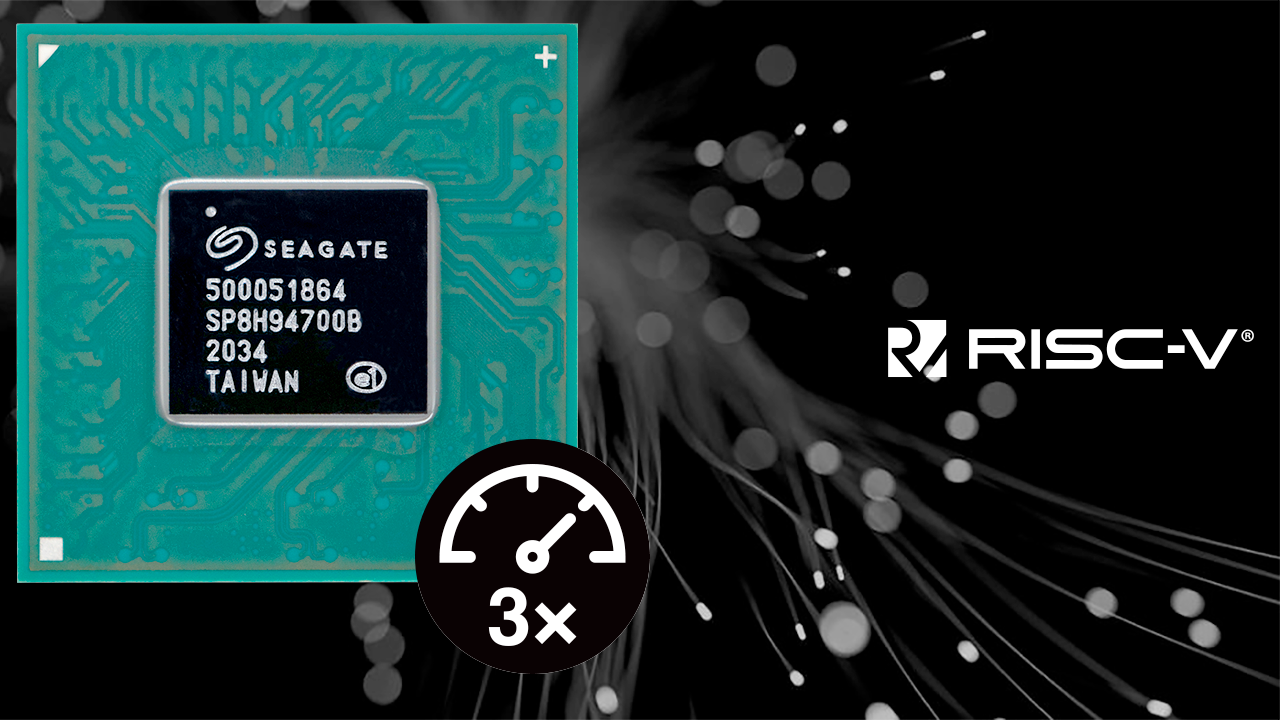

Seagate this week announced that it had developed two RISC-V general-purpose cores that will be used for a wide variety of applications, including the company's upcoming controllers for its storage devices as well as to accelerate real-time analysis in the data center and at the edge. One of the cores is designed to offer high performance, another is area and power-optimized.

Storage Gets Compute Intensive

One of the important things about modern storage is that it is extremely compute intensive.

Controllers for hard disk drives (HDDs) and solid-state drives (SSDs) usually pack multiple general-purpose cores capable of real-time processing to decode signals, process ECC algorithms or execute motion control algorithms. As 3D NAND gains density as a result of architectural (more bits per cell) and/or incremental (more layers) changes and HDD platters increase their track density, SSD and HDD controllers have to process more data in real time, which is why their demands for compute resources are growing. Going forward, with the rise of in-storage processing, SoCs powering storage devices will need even more compute horsepower.

Article continues belowSeagate says that it shipped close to a billion processor cores last year and given the current trends it is likely that the number will only increase in the future. While Seagate does not elaborate which cores it uses today, we can speculate that these were off-the-shelf Arm cores. These cores offer enough performance and capabilities for today's needs and there are next-generation cores that will be able to handle in-storage processing workloads. But Seagate and Western Digital (which is also an adopter of RISC-V) have opted to develop their own cores, perhaps, for three reasons.

Firstly, they want their cores and system-on-chips (SoCs) to be tailored for their particular needs in a bid to differentiate their offerings and implement new features faster. Secondly, they want a better control of their product roadmap and since silicon gets more important these days, it is natural to bring its development in house. Thirdly, a billion cores a year is a large enough number to justify development of in-house cores financially.

Seagate's RISC-V Portfolio

Today, Seagate's RISC-V portfolio includes two cores — a high-performance one and an area/power optimized one — aimed at different workloads and applications.

- Seagate's high-performance RISC-V core is said to offer three times more performance for real-time, critical HDD workloads when compared to currently used controllers. In addition, the core supports all RISC-V security capabilities. Seagate says that this core will be instrumental for its next-generation HDDs with a very high track density that will require finer actuator/head positioning enabled by advanced servo (motion control) algorithms.

In addition, the core could be used for real-time data analysis and similar workloads. It took Seagate about five years to develop the core, which has already been implemented in silicon. - Seagate's area and power-optimized core is designed primarily to run auxiliary and background tasks as well as to execute security-sensitive edge computational operations (including post-quantum cryptography). The core can be configured in terms of feature set, so it can either get smaller and less power hungry, or may gain certain capabilities. The core is about to tape out.

Seagate has not yet disclosed exact performance figures for its cores or process technologies used (or set to use) to implement them. What we do know is that these cores are agnostic to types of applications they power, so they can be used both for HDD or SSD controllers, but not only for them.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Enabling 50TB+ HDDs, 5-Bit-per-Cell Flash & Next-Gen IoT

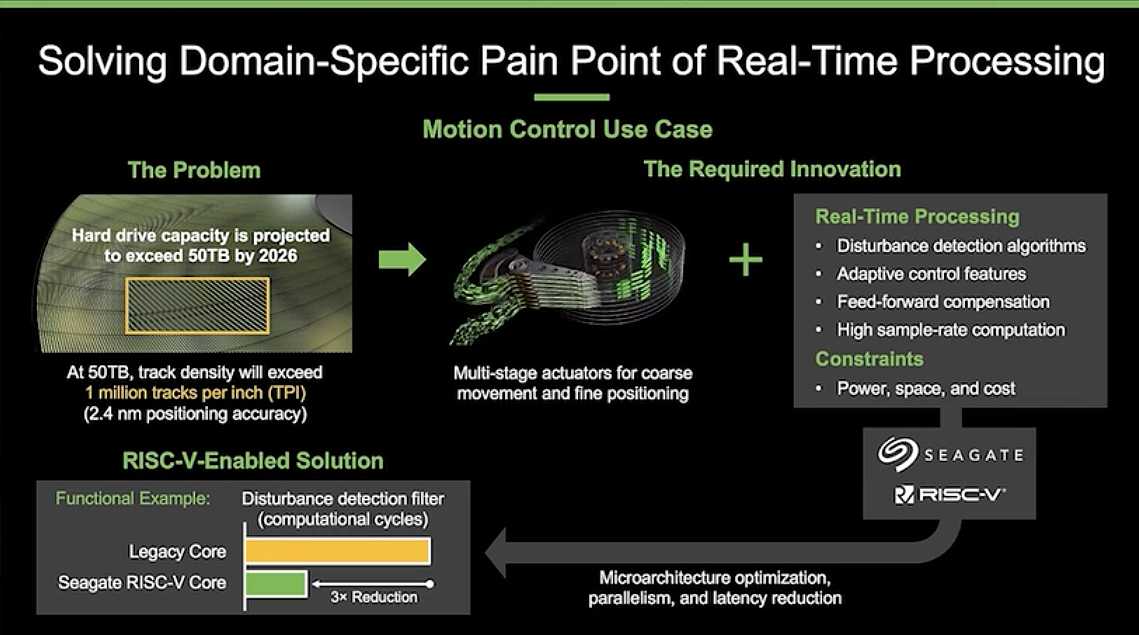

Seagate envisions emergence of 50TB hard drives based on heat-assisted magnetic recording (HAMR) technology by 2026.

These HDDs will feature a track density higher than one million tracks per inch (TPI). To make such TPI density viable, hard drives will require glass platters with a new coating material, new heads, new multi-stage actuators, and new servo mechanisms among other things. The platters and heads will be largely similar to Seagate's 20TB HAMR HDDs shipping today. Meanwhile, new actuators and motion controls will use new head positioning algorithms enabling a 2.4 nm positioning accuracy.

"This presents a significant challenge to the positioning technology used to access this capacity," said John Morris, Seagate’s Chief Technology Officer, at the virtual RISC-V Summit. "At 50TB, the read-write transducer will need to be able to move across the disk at 2.5 meters per second. While also being positioned with a radial tolerance of 2.4 nanometers and controlling head media, vertical spacing within angstrom(s). This challenge is made more significant, given the need to accommodate often uncontrolled, external, mechanical, and acoustic disturbances. To meet this challenge, innovation is required in both the mechanical design of multi-stage actuators, as well as servo technology enabled by real-time processors."

To make the task more challenging, these algorithms are exceptionally compute intensive and they have to be executed in real-time, which makes them a perfect application for Seagate's high-performance RISC-V cores. Meanwhile, HDD controllers have to be very power efficient since 3.5-inch HDD bays have power and TDP constraints, to Seagate's cores not only offer decent performance, but also have to be very power efficient (there are no exact numbers though).

"These servo algorithms are increasingly complex," said Morris. "Built on years of precision motion control expertise and pushing the limits of adaptive and predictive control, these computation needs to occur within tightly coupled timing requirements and within significant constraints of power, space and cost."

Nowadays Seagate uses third-party controllers for its SSDs and so far, it has not announced any in-house processors for such drives. Meanwhile, it is inevitable that emerging and upcoming 3D NAND types of memory, such as 4bpc/3D QLC and 5bpc 3D NAND, need controllers with more sophisticated ECC algorithms than those used today to enhance their reliability and longevity. Potentially, Seagate's RISC-V cores could also be used for SSD controllers.

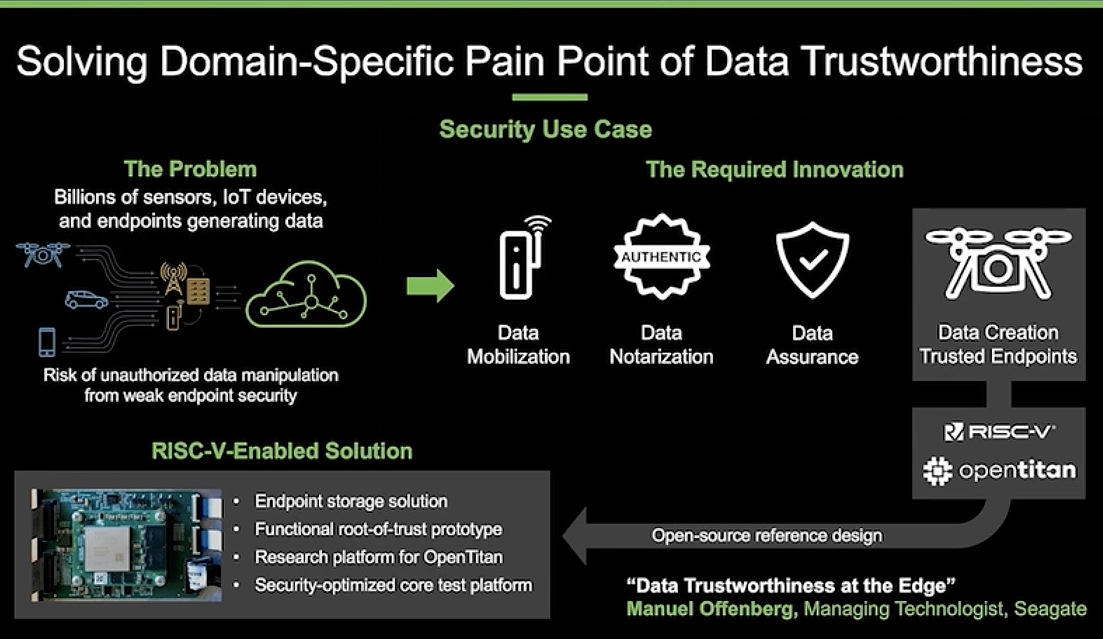

Accurate positioning of HDD heads and fetching data from NAND cells are not the only workloads performed by appropriate controllers today. As more data is generated automatically by various sensors and machines and more autonomous decision-making systems are deployed, security has to be enhanced as the risks of unauthorized data manipulation from weak endpoint security are rising. Seagate and Western Digital are members of the OpenTitan, the first open source project building a transparent reference design and integration guidelines for silicon root of trust (RoT) chips.

"We recognize the potential for open root of trust, designed to significantly improve the security of future data storage infrastructure," said Morris.

Security is evidently one of the applications that Seagate built its area and power-optimized core for, so expect this one to be used for various kind of storage devices supporting OpenTitan.

Seagate's RISC-V-Powered HDD

As part of its RISC-V unveiling, Seagate demonstrated a hard drive powered by a system-on- chip based on its high-performance RISC-V cores at the virtual RISC-V Summit 2020.

Seagate did not reveal many details about its RISC-V-enabled HDD, but said that it featured an 'industry-leading capacity' and ran a 'production-capable silicon,' which is a pretty vague description that could lead to multiple guesses. Meanwhile, the demonstration is an important testament both for Seagate and RISC-V.

In-Storage Processing & Real-Time Analysis

Today, there are not a lot of solid-state drives with in-storage processing (ISP or In-situ) capabilities, but the technology itself is extremely promising as it allows to offload some workloads from CPU thus saving processor cycles, reduce processing latency, and save I/O bandwidth.

Performance, latency, and power consumption are crucial for many emerging applications, such as real-time data analysis and machine learning. Some estimate that ISP can speed up data analysis by 1000 times, an enormous benefit for scientific computing.

Today, there are not a lot of solid-state drives with in-storage processing (ISP or In-situ) capabilities, but the technology itself is extremely promising as it allows to offload some workloads from CPU thus saving processor cycles, reduce processing latency, and save I/O bandwidth.

Performance, latency, and power consumption are crucial for many emerging applications, such as real-time data analysis and machine learning. Some estimate that ISP can speed up data analysis by 1000 times, an enormous benefit for scientific computing.

“At Los Alamos National Laboratory, using computational storage to move processing near data has begun to significantly alter the way we analyze data and perform scientific discovery,” said Brad Settlemyer, Sr. Research Scientist at Los Alamos National Laboratory. “By having compute integrated closely with storage we are able to create persistent data transformations that speed up data analysis by 1000-fold. This greatly relieves our primary compute tier from these tasks. We will be continuing our drive toward efficiency gains for our mission needs by partnering with vendors and actively participating in important industry initiatives like computational storage.”

Seagate says that its RISC-V cores could also be used for custom SoCs designed for computational storage devices, but does not elaborate about exact SoCs and upcoming products.

Bottom Line

Seagate has developed two RISC-V cores that demonstrate its plans to design a variety of custom SoCs for various storage applications. These SoCs are going to be particularly instrumental for the company's upcoming high-capacity HDDs, its next-generations of SSDs with or without in-storage processing capabilities, and secure storage devices supporting OpenTitan.

In house-designed RISC-V cores enable Seagate to tailor its processing capabilities for its needs and implement new features rapidly in a bid to design unique products that are not available from its rivals. Furthermore, since RISC-V is a royalty-free open-source architecture, Seagate will not have to pay royalties to Arm for its technology, which will save some cash.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.