SiFive Readies RISC-V Desktop PC For Devs, New CPUs with Vector Extensions

SiFive continues to advance RISC-V CPU architecture

Many leading analysts agree - Nvidia's recently-announced ARM acquisition will result in broader industry uptake of the open-source RISC-V CPU architecture, and SiFive, one of the major driving forces behind the RISC-V CPU architecture, made a timely announcement today.

SiFive disclosed plans to provide interested software designers with desktop PCs running a RISC-V chip to assist of software development or porting to the open-source CPU architecture. The announcement comes as the open-source RISC-V CPu architecture enjoys more interest in the wake of Nvidia's acquisition of ARM.

SiFive also said it would announce RISC-V processing cores that support the latest RISC-V vector (RVV) extensions and can run high-level operating systems in October. RVV will enable RISC-V CPUs to address performance-demanding applications.

Article continues belowHigh-level OS-Capable RISC-V CPUs with Vector Extensions

SiFive introduced its first RISC-V CPU cores back in 2016 targeting microcontrollers and simplistic SoCs for low-power devices. Last year, the company added U8-series out-of-order processor cores into its IP portfolio to address performance-demanding applications. At this year’s Linley Group Fall Processor Conference, SiFive plans to disclose additional details regarding its upcoming Linux-capable superscalar multi-core processor design that will feature the latest RISC-V Vector extensions.

Vector extensions, such as Intel’s AVX, are used to more efficiently process vectorized data sets and are commonly used by high-performance computing and multimedia applications. Introducing vector extensions to RISC-V will bring the architecture closer to Arm, PowerPC as well as x86 and will allow it to compete for modern performance-demanding applications, such as AI and ML.

SiFive Development PC Incoming: U7-Based Desktop

Having secured over 100 design wins to date, SiFive is interested in making the RISC-V architecture more widespread. To make this happen, it plans to provide RISC-V-based PCs to developers to enable them to create applications compatible with the instruction set.

The PCs will be based on the yet-to-be announced SiFive Freedom U740 SoC that features a heterogeneous core complex combined with modern PC interfaces and expansion capabilities. The desktop computer will come with a set of tools to develop bare-metal or Linux-based applications as well as to port existing programs to the new hardware platform.

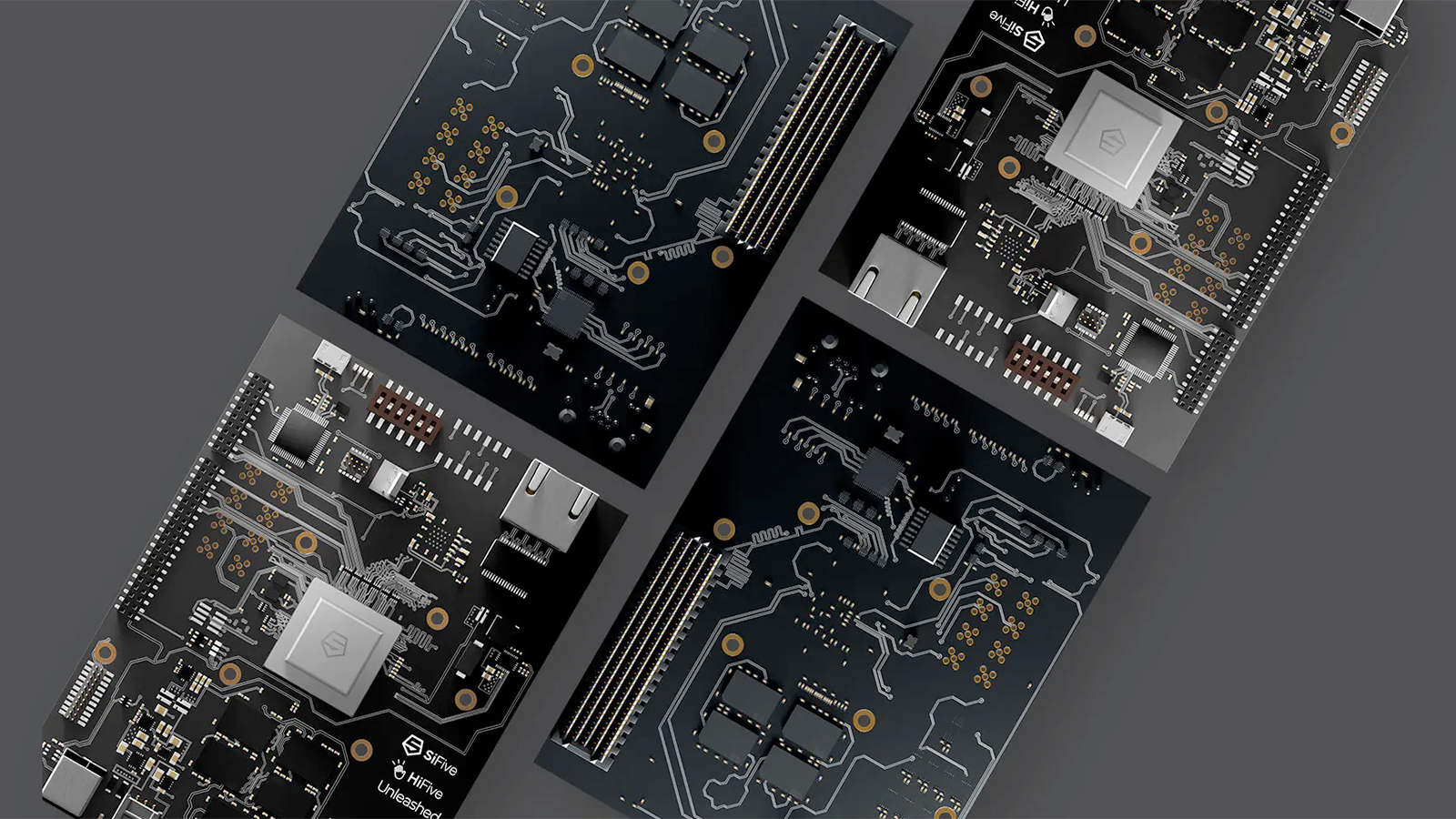

Source: SiFive

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

Math Geek other than being open source, what are the benefits of RISC vs x86/ARM/etc...Reply

i know in the past it was a better optimized instruction set, but i thought that was pretty much incorporated into x86.

can anyone enlighten me? -

samopa ReplyMath Geek said:other than being open source, what are the benefits of RISC vs x86/ARM/etc...

ARM is a RISC, not so long ago ARM = Accorn RISC Machine, but now it (patented) just ARM.

Now in the topic of RISC vs CISC, the R in RISC stands for Reduced (as opposite Complex in the CISC), meaning that the number of instruction that can be executed (called Instruction Set) of RISC are significanly lower compare to the CISC, and the instruction on the RISC is (usually) fixed length compare to variable length in CISC, this translate to significantly more simple to create circuitry (in term of number of transistor budget) to execute that Instruction Set, which result fewer trace, fewer power needed, more efficient, etc.

The chip needed to run RISC is significantly smaller (in term transistor budget) than CISC, and needed far less power to operate. The catch is, because number of Instruction is limited, to perform complex calculation it has to do more step (cycle) than the CISC. For example, if for particular computation the CISC only need 3 cycle, the same computation maybe need 15-25 cycle in RISC, because the RISC need to emulate that complex computation into several simple computation.

In general, if the load is 70:30 (simple:complex) computation, the the RISC machine with same clock speed is 30% slower than CISC machine, but need much less power to operate, this is why the RISC is widely adopted in portable/mobile device and devices that do not need complex computation. This of course is in assumption that everything else is being equal, no optimization, no specificc circuit, etc. -

GetSmart Yet to see any performance figures from these new (alternative) CPUs. Can they even compete with the current crop of CPUs, in terms of performance (to be useable)? Another issue is development and software ecosystem. :unsure:Reply -

Math Geek Replysamopa said:ARM is a RISC, not so long ago ARM = Accorn RISC Machine, but now it (patented) just ARM.

Now in the topic of RISC vs CISC, the R in RISC stands for Reduced (as opposite Complex in the CISC), meaning that the number of instruction that can be executed (called Instruction Set) of RISC are significanly lower compare to the CISC, and the instruction on the RISC is (usually) fixed length compare to variable length in CISC, this translate to significantly more simple to create circuitry (in term of number of transistor budget) to execute that Instruction Set, which result fewer trace, fewer power needed, more efficient, etc.

The chip needed to run RISC is significantly smaller (in term transistor budget) than CISC, and needed far less power to operate. The catch is, because number of Instruction is limited, to perform complex calculation it has to do more step (cycle) than the CISC. For example, if for particular computation the CISC only need 3 cycle, the same computation maybe need 15-25 cycle in RISC, because the RISC need to emulate that complex computation into several simple computation.

In general, if the load is 70:30 (simple:complex) computation, the the RISC machine with same clock speed is 30% slower than CISC machine, but need much less power to operate, this is why the RISC is widely adopted in portable/mobile device and devices that do not need complex computation. This of course is in assumption that everything else is being equal, no optimization, no specificc circuit, etc.

what type of workload would be considered simple vs complex? the article speaks of AVX type loads being added. wonder what else would be considered complex vs simple calculations.

seems like some sort of hybrid chip (which are starting to see the light of day) would be the eventual way to go. whatever load is present could be sent to the right cores for the job. with the non-optimized cores taking overload work if they are not already doing something else. but that's just a wild guess on my part. -

GetSmart The difference between CISC and RISC is actually the structure of the instruction itself. ;)Reply

Typically a single RISC instruction consists of several simple sub-instructions (micro operations) that the CPU core can execute directly. The efficiency of RISC is that one single "instruction" can do multiple integer and arithmetic operations together. That is why RISC can execute more operations than CISC per single instruction cycle or per clock cycle... 🤠

On the other hand, a single CISC instruction will be need to be translated into sub-instructions (micro operations) that can be executed within the CPU core. Usually one CISC instruction can only do a single integer or arithmethic operation. Addtion of much more complex (for multiple operations per instruction), SIMD-style and vector instructions helps alleviate some of these shortcomings. AVX2 and AVX512 are the latest additions... :geek:

AVX-style instructions are typically a CISC type, needs to be translated. :vip: -

bit_user Reply

RVV is hardly a first. ARM has had SVE for a while, even if it's still uncommon.kanewolf said:Seymour Cray would be proud. We are all the way back to Cray architecture. -

bit_user Reply

Careful - RISC and RISC-V are very different things.Math Geek said:other than being open source, what are the benefits of RISC vs x86/ARM/etc...

RISC is a CPU design approach first popularized in the 1980's, while RISC-V is a RISC-like CPU "instruction set architecture" (ISA) which was developed by an academic + industry consortium and introduced in 2010.

RISC-V is not open source, as misstated by the article. Rather, it is open and royalty-free (meaning anyone can design their own RISC-V CPU without any sort of license). By contrast, ARM is open and non-free (meaning anyone can implement it, but you have to pay ARM for the privilege), and x86 is proprietary (meaning Intel will not let any newcomers start making x86 CPUs).

The main advantage of RISC-V is simply that it's newer and better-matched to current semiconductor manufacturing capabilities and toolchains. x86 is a creature its day, and keeps getting pumped up with botox and plastic surgery to appear fun an exciting, but at a phenomenal cost in terms of engineering resources and power-efficiency. In the end, it's fighting a losing battle. -

kanewolf Reply

Cray did vector instruction in 1976 -- https://www.hpcwire.com/2016/09/26/vectors-old-became-new-supercomputing/bit_user said:RVV is hardly a first. ARM has had SVE for a while, even if it's still uncommon. -

bit_user Reply

I think you've got that backwards. The R in RISC is for "Reduced", while the "C" in CISC is for "Complex".GetSmart said:Typically a single RISC instruction consists of several simple sub-instructions (micro operations) that the CPU core can execute directly. The efficiency of RISC is that one single "instruction" can do multiple integer and arithmetic operations together. That is why RISC can execute more operations than CISC per single instruction cycle or per clock cycle... 🤠

On the other hand, a single CISC instruction will be need to be translated into sub-instructions (micro operations) that can be executed within the CPU core. Usually one CISC instruction can only do a single integer or arithmethic operation.

A typical example would be how a CISC instruction can combine the instruction's core function (let's say dividing one number by another) with address arithmetic and a load and/or store, in case a source or destination was in memory instead of a register.

Classical RISC instructions would operate register-to-register. If you wanted a load or store, that was a separate instruction. And if you needed to do any address arithmetic (such as adding a constant offset), that would be another instruction - just a normal addition instruction. The idea was that by making the instructions simpler, they could be implemented more efficiently and you saved silicon budget for optimizations like pipelining or superscalar execution. They would also tend to clock higher. The theory was that the net effect would be higher throughput, in spite of the need to execute more instructions to do the same work.