Synopsys Enables 5nm SoCs with HBM3

HBM3 memory ready for implementation.

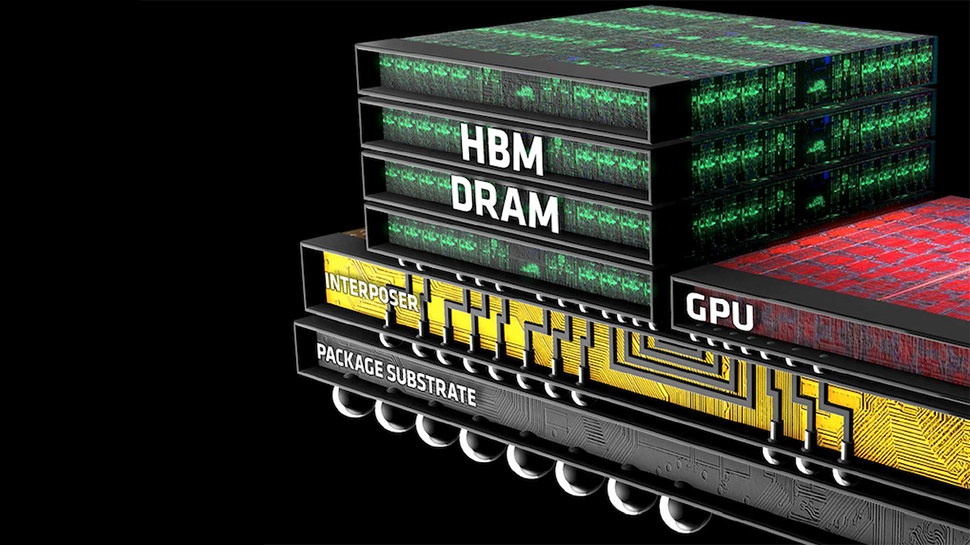

Synopsys this week unveiled its HBM3 solution that enables developers of system-on-chips (SoCs) to add support for next-generation HBM3 memory to 2.5D designs implemented using a 5nm fabrication process. The IP package supports HBM3 memory chips featuring an up to 64GB capacity, up to 7200 MT/s data transfer rate, and up to 921 GB/s bandwidth.

Leading memory makers Micron, Samsung, and SK Hynix have endorsed Synopsys' industry's first complete HBM3 solution and said they were committed to produce HBM3 memory. Synopsys' HBM3 solution includes a DesignWare HBM3 controller, physical interface (PHY), verification IP, and 3DIC compiler.

A Synopsys HBM3 controller supports up to 32 pseudo channels (i.e., 16 physical 64-bit channels or a 1024-bit interface) with 16 to 64 banks per pseudo channel as well as up to 32Gb channel density. In more down-to-earth terms, a controller with PHY supports an HBM3 memory stack with varying numbers of layers that has a capacity of up to 64 GB as well as a 1024-bit physical interface with an up to 7200 MT/s data transfer rate. Typical HBM-supporting SoCs feature two, four, or six controllers. Hence, Synopsys' HBM3 solution can enable memory bandwidth of up to 3.68 TB/s for SoCs equipped with four HBM3 stacks.

The controller also supports error correction code (ECC), refresh management, and parity, so it can be used for datacenter and high-performance computing (HPC) applications that require various RAS (reliability, availability, scalability) features.

Synopsys says that its HBM3 controller and PHY are largely based on the company's 5nm silicon-proven HBM2E IP, which means lowered risks. Meanwhile, Synopsys' HBM3 controller uses a proven DFI 5.0 interface to connect to its PHY and supports widely used Arm multiport AMBA 4 AXI host interfaces.

To further simplify implementation and reduce risks, the company offers 3DIC Compiler that features a complete HBM3 auto-routing solution for swift and robust design development.

"Synopsys continues to address the design and verification requirements of data-intensive SoCs with high-quality memory interface IP and verification solutions for the most advanced protocols like HBM3, DDR5 and LPDDR5," said John Koeter, senior vice president of marketing and strategy for IP at Synopsys. "The complete HBM3 IP and verification solutions enable designers to meet increasing bandwidth, latency and power requirements while accelerating verification closure, all from a single, trusted provider."

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.