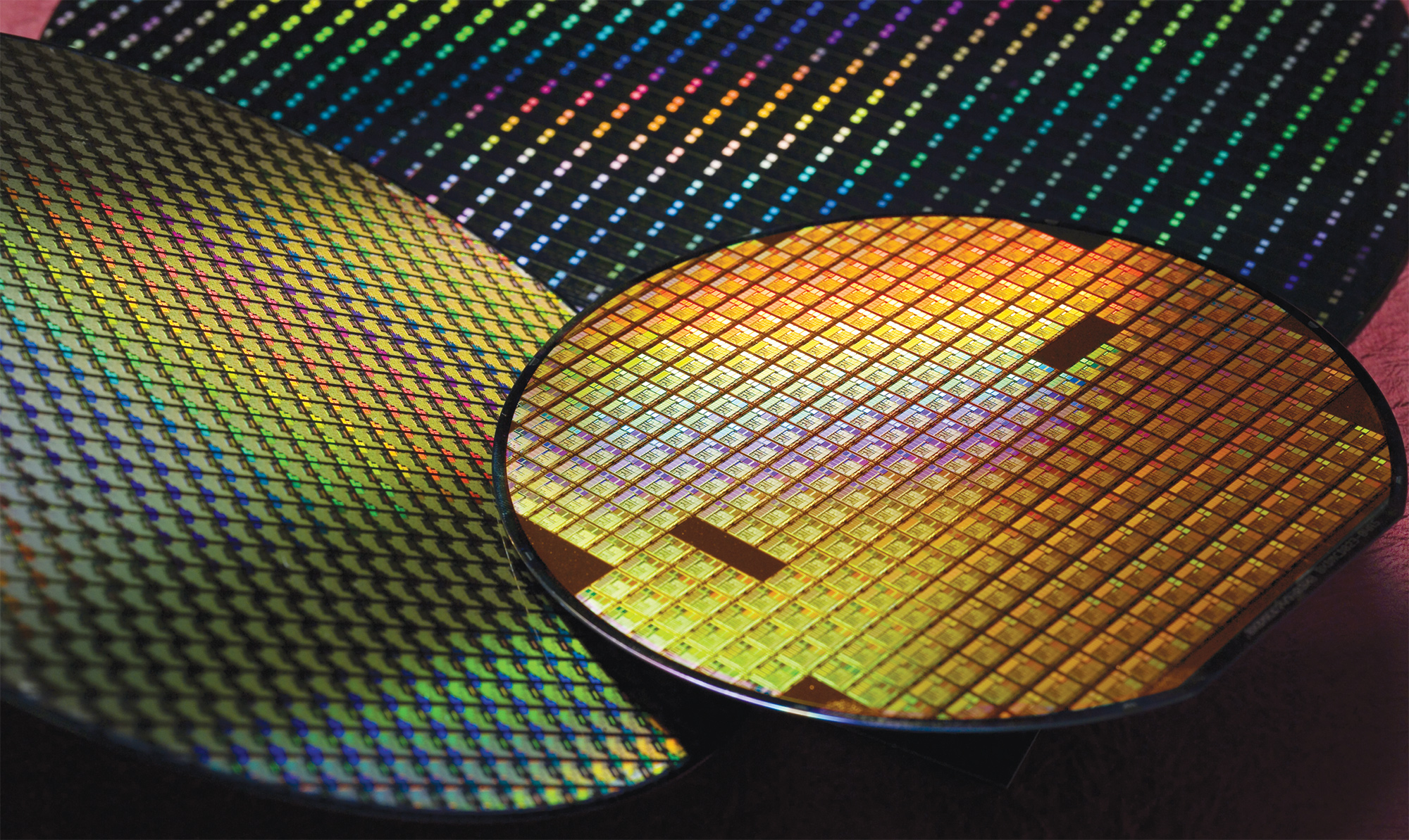

TSMC's wafer pricing now $18,000 for a 3nm wafer, increased over 3X in 10 years: Analyst

At advanced nodes, chips are not getting cheaper.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Apple's A-series smartphone processors have evolved significantly from the A7 (28nm) to the A18 Pro (3nm), gaining more cores, transistors, and features. With each new node, TSMC charged Apple more per wafer, so the price increased from $5,000 for a 28nm wafer with A7 processors to $18,000 for a 3nm-class wafer for A17 and A18-series processors, reports Ben Bajarin, the chief executive and principal analyst at Creative Strategies.

Bajarin notes that as Apple's A-series chips have evolved, their transistor count has consistently increased, starting at 1 billion in the A7 and reaching 20 billion in the A18 Pro. That makes sense because the number of cores and features has also increased: in 2013, the A7 featured two high-performance cores and a four-cluster GPU, whereas, in 2024, the A18 Pro features two high-performance cores, four energy-efficient cores, a 16-core NPU, and a six-cluster GPU.

Got a detailed price/die/density analysis of Apple A-silicon over time at TSMC. Some nuggets.From A7 to A18:- progression from 28nm to 3nm- Most dramatic shrinks occurred early (28nm → 20nm → 16nm/14nm)- Steady increase in transistor count from 1 billion (A7) to 20…December 18, 2024

A-series processors are aimed at smartphones, and Bajarin says their die sizes have remained relatively consistent, ranging between 80 and 125 square millimeters across generations. This was enabled by a steady increase in transistor densities facilitated by TSMC's latest process technologies.

Article continues belowThe most substantial transistor density increases occurred in the earlier nodes, such as transitions from 28nm to 20nm and then to 16nm/14nm. However, recent process technologies (N5, N4P, N3B, N3E) exhibit slower density improvements. The peak period for transistor density improvements occurred around the A11 (N10, 10nm-class) and A12 (N7, 7nm-class), with gains of 86% and 69%, respectively. Recent chips, including the A16 to A18 Pro, show a noticeable slowdown in density advancements, primarily due to slower SRAM scaling.

However, despite diminishing returns, Bajarin notes that production costs have risen sharply. Wafer prices climbed from $5,000 for the A7 to $18,000 for the A17 and A18 Pro, while the cost per square millimeter increased from $0.07 to $0.25.

Bajarin says his information comes from a third-party supply chain report, and the company that produced it has sources at TSMC. Bajarin has also triangulated certain factors through his own sources. In general, the listed TSMC pricing looks more or less consistent with previous reports, though we should always take non-official information with a grain of salt.

To make things even harder for Apple, performance increases have also slowed down with the latest generations of its processors (with A18 and M4-series being exceptions) as it got harder to extract higher instruction per cycle (IPC) throughput with the latest architectures. Nonetheless, Apple has managed to maintain performance-per-watt gains with each generation.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

"Given it is harder to pull out IPC gains, but getting efficiencies where they can even if its costs related to area increase, [is a viable] performance-per-watt [gain] strategy," Bajarin told Tom's Hardware.

According to well-cited industry reports, TSMC always sells its customers wafers with sellable and non-sellable dies, not just sellable dies. Therefore, the number of chips derived from a wafer depends on the manufacturing yield. Higher yields produce more chips per wafer, while lower yields result in fewer. This yield-based variability impacts the cost-effectiveness of the wafers for customers. However, there is one important part here: TSMC guarantees that it will try to achieve a certain yield target before production starts.

If the actual yield falls short by a substantial margin, such as 10% to 15%, TSMC may provide financial compensation or discounts to affected customers. These terms aim to reassure clients about TSMC's reliability and the value of their high-cost wafers.

Being an alpha customer for the latest process technologies, Apple has a chance to adjust manufacturing processes to lower defect density and increase its yields, so the company is in a better position from a cost perspective than other TSMC clients. Also, it's rumored that Apple is TSMC's only customer that pays TSMC on a per-chip, not per-wafer, basis. If true, this sets Apple further apart from other TSMC customers.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

hotaru251 do wonder what the "limit" is on price of electronics.Reply

most people are making less (as inflation makes stuff cost more so value isnt as high) yet goods go higher and a company can only sell stuff for a set price before too few ppl buy em and its losing $. -

Stevemeister Why is anyone surprised. The chips with 3nm node pack in way more transistors than 28 nm so you have a choice of making the chips smaller with the same processing power or the same size with a lot more processing power. Given the propensity of apps to add more features get increasingly complex the latter seems to be happening hence costs increase but with some new smartphones hitting $1500 there will be a point where people will stop paying.Reply -

Loadedaxe Reply

Not all people, I haven't updated my PCs or phone in many years and have no plans to at the moment.Amdlova said:people will pay... have market for it :) -

spongiemaster ReplyScott Davey said:Not completely blaming the article writer here but it seems a pretty serious oversight to go by wafer price and not even mention the cost per transistor over the same timeframe. At 28nm, transistor density is around 14M/mm2 while 3nm is at about 300M/mm2. In other words, all else being equal, you would get about 21x the number of chips on a 3nm wafer vs. a 28nm wafer (never mind order-of-magnitude better efficiency/clock scaling etc.)

Accounting for the 3x cost increase, an equally accurate headline could be:

TSMC reduces cost per transistor by 7x over 10 years

The math doesn't check out. Cost per transistor hasn't dropped in 15 years. It's been slowly going up over that time.

https://cdn.mos.cms.futurecdn.net/LmCtmoT57uZA8jqgWkz5Yo-1200-80.png -

Pierce2623 Reply

You do realize you can’t get 21x the number of chips just because you have 21x transistors because you can’t just infinitely shrink everything, right? SRAM uses like 30% of the transistor budget and doesn’t scale as nearly much as logic on modern nodes not to mention things like massively overbuilt modern branch predictors that can recognize patterns that are insanely complicated to prevent lost work killing your efficiency.Scott Davey said:Not completely blaming the article writer here but it seems a pretty serious oversight to go by wafer price and not even mention the cost per transistor over the same timeframe. At 28nm, transistor density is around 14M/mm2 while 3nm is at about 300M/mm2. In other words, all else being equal, you would get about 21x the number of chips on a 3nm wafer vs. a 28nm wafer (never mind order-of-magnitude better efficiency/clock scaling etc.)

Accounting for the 3x cost increase, an equally accurate headline could be:

TSMC reduces cost per transistor by 7x over 10 years -

spongiemaster According to Yahoo from last year:Reply

https://finance.yahoo.com/news/tsmc-may-increase-wafer-pricing-104033184.html

Negotiations with AI and HPC customers, such as Nvidia, suggest these clients can tolerate approximately 10% price hikes for 4nm-class wafers from around $18,000 per wafer to around $20,000 per wafer. As a result, the 4nm and 5nm nodes, primarily used by companies like AMD and Nvidia, are expected to see an 11% blended average selling price (ASP) hike. This means that prices of N4/N5 wafers may increase by approximately 25% since Q1 2021, at least for some customers.

4nm already costs $20k per wafer now. A 25% increase in cost for the same node since 2021. This is why Gelsinger was trying to get Intel into fabbing for external customers.

While wafer prices depend on actual agreement and volumes, some believe that a wafer produced on TSMC's N3 node costs around $20,000 or higher, but will increase next year. Morgan Stanley believes that companies should be room for companies to 'pass through the additional costs to end users.'

$18k per 3nm wafer seems like a really optimisitic estimate. Ironically, the link in the quote above points to an article on this site about 3nm wafers costing $20k. -

thestryker Reply

It could make sense as an Apple exclusive price given that they've bought first runs of TSMC's last few nodes entirely. I certainly agree that likely isn't the standard rate for the node.spongiemaster said:$18k per 3nm wafer seems like a really optimisitic estimate. Ironically, the link in the quote above points to an article on this site about 3nm wafers costing $20k. -

Pierce2623 This is quite a significants price drop from the original $25,000 first gen 3nm wafers Apple bought.Reply -

Pierce2623 Reply

I think it probably is now. The $20,000-$25000 Apple was paying was a first gen node with only one production line available. Now they have like 4 different 3nm sites with multiple production lines in each.thestryker said:It could make sense as an Apple exclusive price given that they've bought first runs of TSMC's last few nodes entirely. I certainly agree that likely isn't the standard rate for the node.