Compute Express Link Victory Lap as Synposys, ARM Foster Ecosystem

Synopsys has announced the industry’s first Compute Express Link (CXL) IP solution. The DesignWare CXL IP provides a complete solution for FInFET processes and is compliant with the CXL 1.1 specification. Meanwhile, in a victory lap for CXL, Arm has confirmed its commitment to the protocol, raising questions about the future it sees for CCIX.

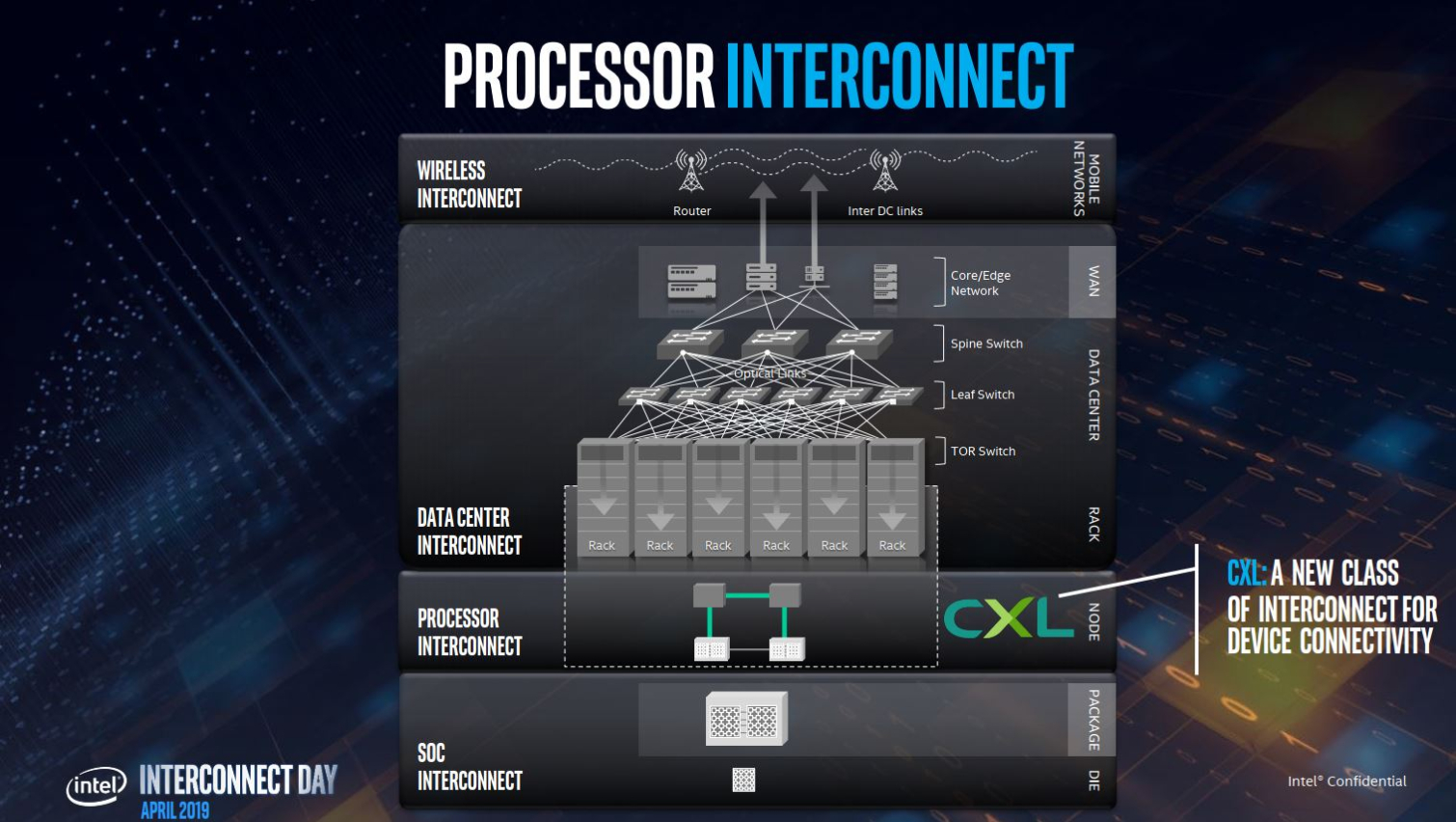

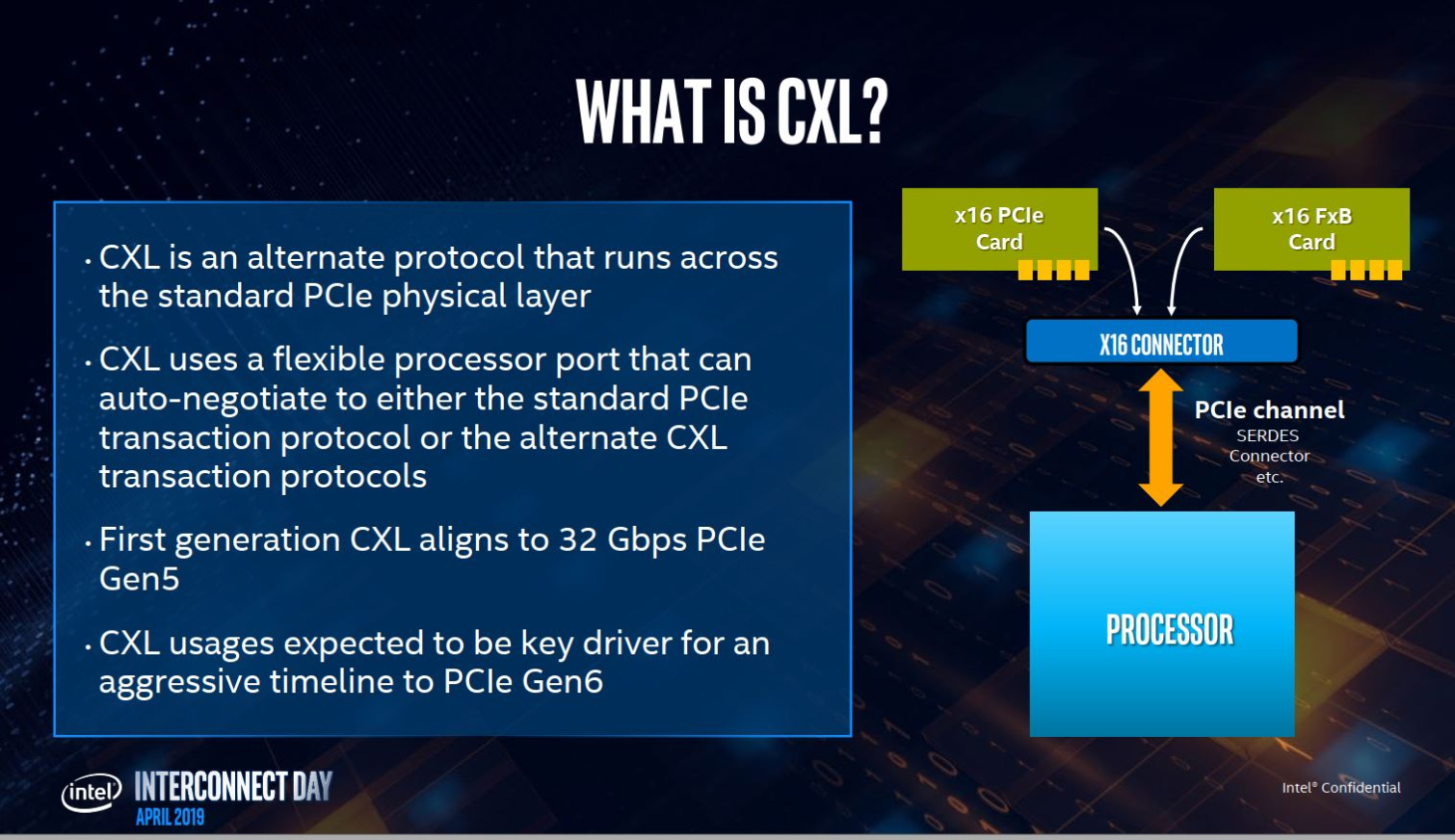

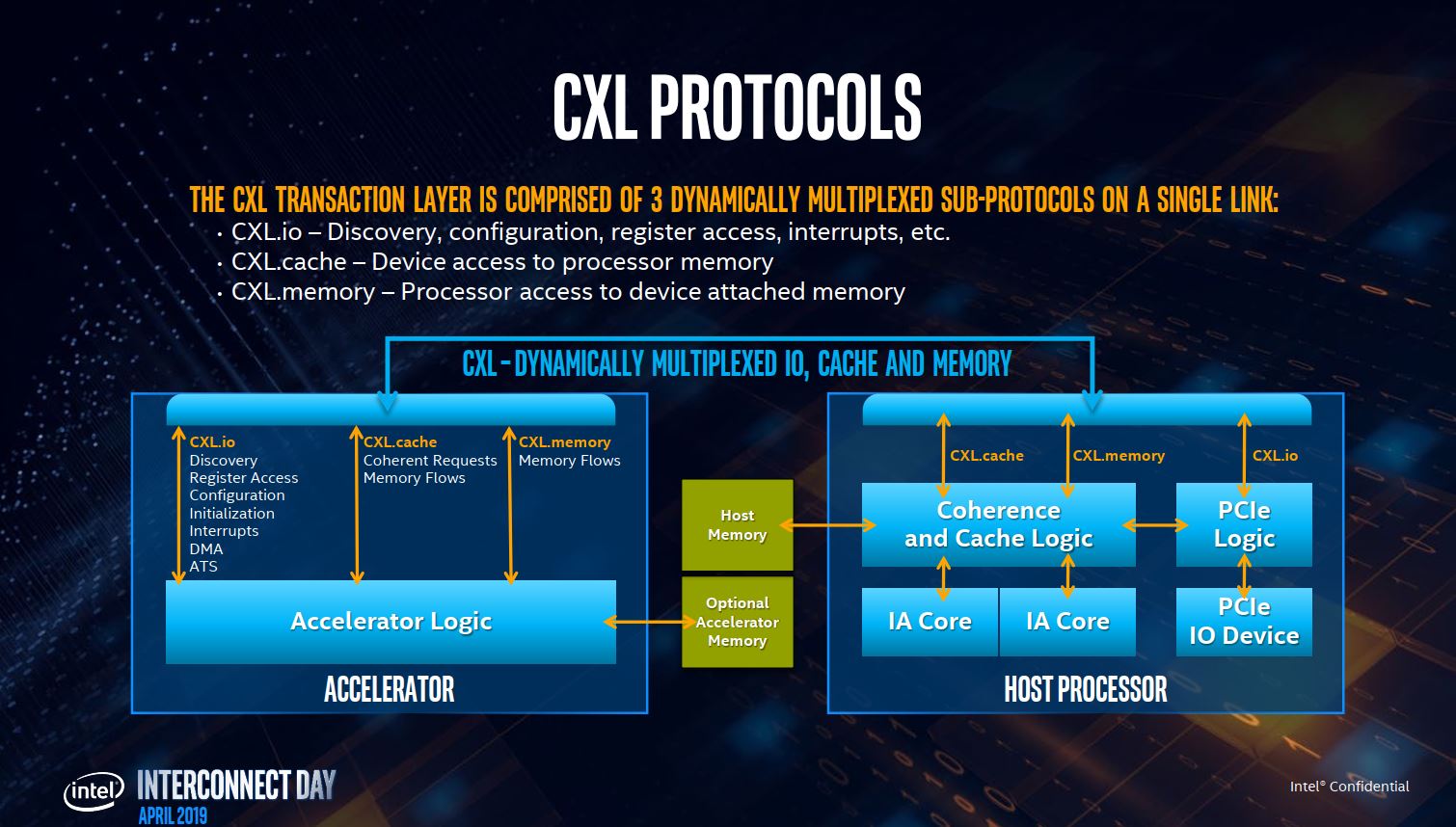

Intel announced the Compute Express Link 1.0 protocol in March as an open, low-latency and cache-coherent interconnect between the CPU and accelerators and memory, that builds upon the PCI Express infrastructure by leveraging PCIe 5.0’s physical and electrical interface. Since then, numerous members have joined the consortium, and it has published the CXL 1.1 specification.

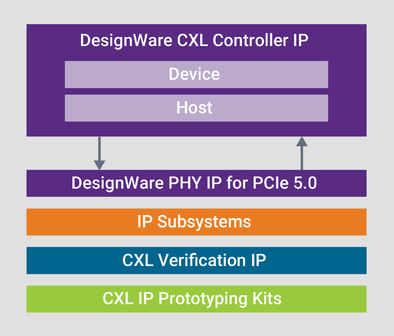

Similarly, Synopsys’ DesignWare CXL IP is built upon its PCI Express 5.0 IP, which it says reduces the integration risk. The complete solution consists of a CXL controller, PHY, and verification IP. It is compliant with the CXL 1.1 specification and supports all CXL device types (such as AI, memory expansion and cloud chips) and its three protocols: CXL.io, CXL.cache, and CXL.mem. The controller has a 512-bit architecture that supports x16 links, and it also has additional RAS capabilities. This enables up to 16 lanes at 32GT/s data rates.

Dr. Debendra Das Sharma, Intel Fellow and director of I/O Technology and Standards at Intel provided following comment: "With support from leading IP providers like Synopsys, we're well on the way to a robust, innovative CXL ecosystem that will benefit the whole industry."

The CXL PHY IP is available for 16nm, 10nm and 7nm processes. The controller and verification IP are also available now.

Also on Wednesday, Arm published a blog about its CXL membership. While we noted two months ago already that Arm had joined the consortium, it detailed its intentions for CXL and its place next to the CCIX protocol.

The company says it has dedicated key resources towards CXL and aims to ensure "low friction CXL development to the Arm ecosystem" as well as contributing to future specifications. Moreover, Arm sees CXL taking on the role as prime interconnect going forward, relegating CCIX to an inter-package interconnect:

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

"Arm brings to the table its track record in establishing a full software framework and aims to promote the migration to CXL as the interface to the accelerators and memory expansion. We expect to maintain CCIX to support inter-package chip-to-chip interface that is currently not in the scope of CXL. We will continue to support customer solutions based on existing CCIX hardware." (Emphasis added.)

While Arm does not exclude any protocols for now, and declares Gen-Z as "the fabric that allows for rack and row connectivity", the comments leave little room for imagination, indicating that Intel’s CXL – the last interconnect to have been announced – might be winning the cache-coherent interconnect wars even before the first chip has launched.