Intel Donates Compute Express Link, a High-Speed Protocol for PCIe 5.0

The newly-formed Compute Express Link (CXL) consortium has announced a new interconnect, developed and contributed by Intel, that is designed to provide a cache-coherent interface between CPUs and other devices, like GPUs, FPGAs, and memory devices.

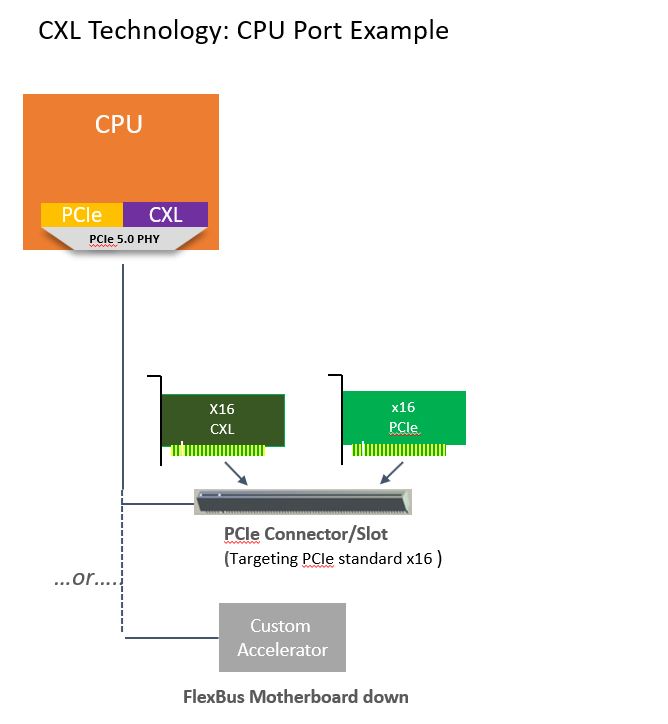

Notably, the new interconnect rides on top of the PCIe 5.0 interface that should debut in 2021, instead of the PCIe 4.0 interface that many have predicted will have a relatively short lifespan.

Unleashing the power of high-speed processors and accelerators requires fast and flexible interconnects that can feed compute cores with data for processing. The insatiable desire for more bandwidth is one of the most vexing problems for system architects because data movement consumes time and power, ultimately equating to higher operational costs.

The Compute Express Link interconnect is designed to help lessen that burden. The cache coherent interface is designed for data centers and enables shared memory spaces that reduce overhead and latency. The protocol runs across the PCIe 5.0 bus, so it is electrically and mechanically compatible with the soon-to-be-widespread interface and provides enhanced I/O and memory protocols, along with a coherency interface.

Unfortunately, deeper technical details aren't available at this time, though the consortium says the version 1.0 specification will be made fully available to members. The first revision is based entirely on Intel's internal development over the last four years, but the specification will evolve with input from the other members in the future. Intel contributed CXL as an open interface, so members of the consortium are free to use the IP without licensing fees.

Intel also announced that it is developing CXL-infused Xeon processors, FPGAs, GPUs, and SmartNICs. Those products will debut in 2021. This marks Intel's first disclosure of a rough timeline for PCIe 5.0 products, while it has yet to announce any firm plans around the PCIe 4.0 interface. CXL could also be used as an interconnect to persistent memory, so we expect an eventual tie-in with Intel's DC Persistent Memory DIMMs.

Other notable specifications, like OpenCAPI, CCIX, and Nvidia's NVLink also offer similar capabilities and enjoy broad industry support, while the relatively small initial list of backers for the CXL interface consists of Intel, Google, Dell/EMC, Microsoft, and Huawei, among others. Other notable names missing from the list of CXL backers, like Nvidia and AMD, are also free to join the consortium.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

The Gen-Z interface also looms large as another similar industry standard, but the CXL consortium views the interface as complementary to its technology, saying that a Gen-Z device could easily interface with a CXL device. The consortium did note that there is some overlap in capabilities between the CCIX interface and CXL, so we could see a war between the specifications emerge.

The unveiling of the new interconnect is somewhat surprising, but it meshes well with Intel's new strategy that it outlined during its recent Architecture Day. During the event, the company outlined six new pillars it will focus on in the coming years, including process technology, architectures, memory, security, software, and interconnects. CXL appears to be a big step forward on the interconnect front, and although the interconnect doesn't appear to be entirely open to non-members, the strategy does reflect a change of pace to Intel's typical proprietary approach.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.