ASML and TSMC Reveal More Details About 3nm Process Technology

TSMC's N3 node to use EUV extensively

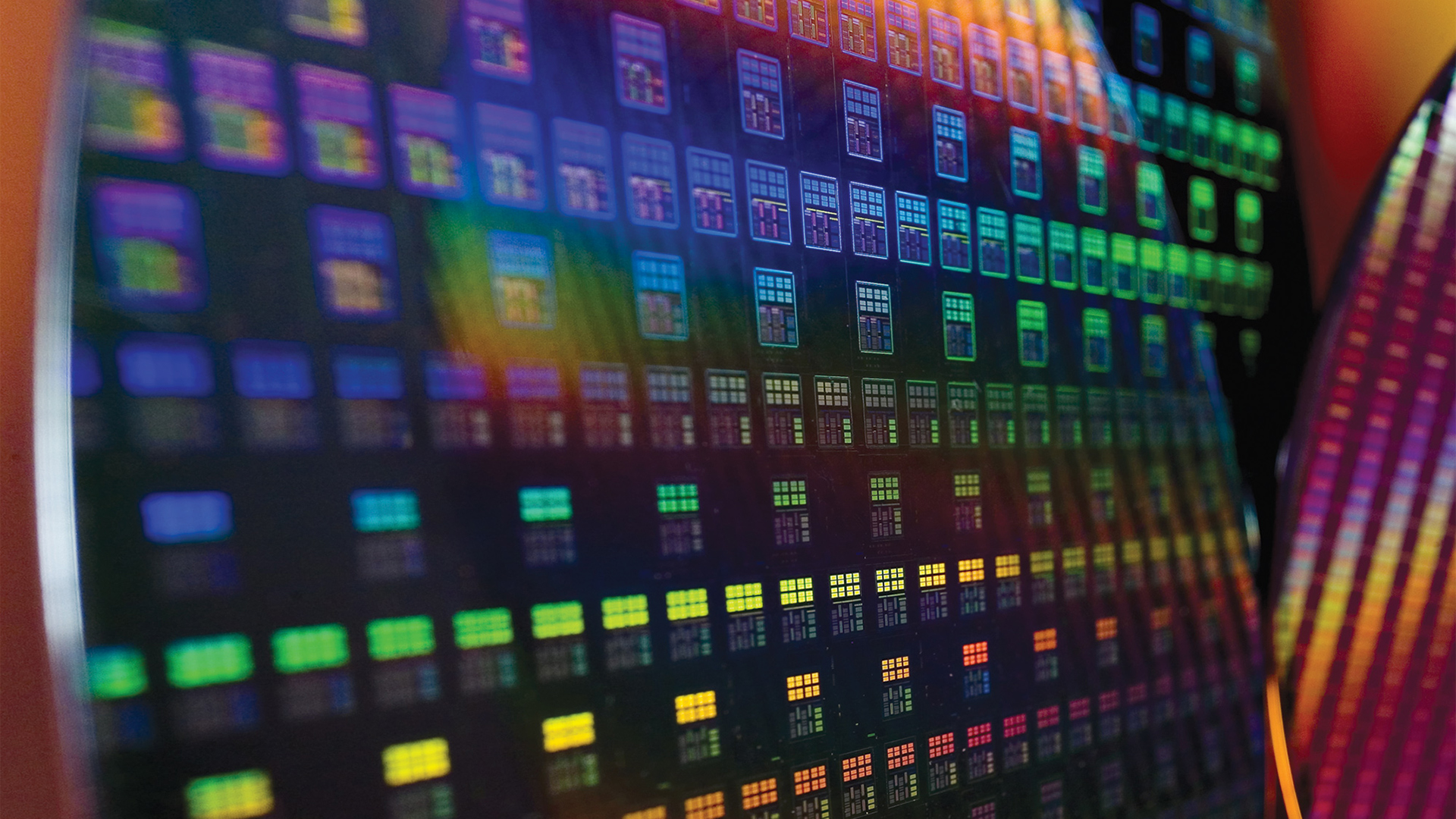

Taiwan Semiconductor Manufacturing Co. (TSMC) was the first company to initiate high-volume production using extreme ultraviolet (EUV) lithography tools. So far, the company has developed at least three processes that use EUV for select layers and has gained quite a lot of experience how to use the new equipment. TSMC will continue to expand usage of EUV for its next-generation technologies and its 3nm (N3) node is projected to use EUV for up to 'over 20 layers.'

Right now, TSMC has three fabrication processes that use EUV lithography: N7+, N6, and N5. TSMC's 2nd generation 7nm technology uses EUV for up to four layers in a bid to reduce usage of multi-patterning techniques when making highly complex circuits. The company's 6nm process is designed for clients who want to re-use IP designed for 1st generation 7nm, but still want to take advantage of EUV to slightly increase transistor density. Those customers who need a substantial increase in transistor density along with performance (when compared to N7+) can pick TSMC's N5 node that can use EUV for up to 14 layers.

Going forward, TSMC plans to offer its clients N5P and N4 fabrication processes that will largely be based on N5 technology and will provide some performance and power benefits. Both processes will be compatible with N5 on the IP and design rules levels and will provide an easy migration path for chip developers. N5P is expected to be available to TSMC's clients in 2021, whereas N4 will be available in 2022.

TSMC's next-generation process technology — N3 — will provide a full node improvement over N5. In particular, the contract maker of semiconductors promises an up to 15% performance gain (at the same power and transistor count), an up to 30% power reduction (at the same clocks and complexity), and an up to 70% logic density gain. One of the most interesting details about N3 is that it will use EUV for up to 'over 20 layers,' according to ASML.

"I think, on the N5 in logic we are over 10 layers and in N3 we will be over 20 and we actually see that creeping up," said Peter Wennink, CEO of ASML. "That has just the fact that it gives so much more advantage to go to single patterning and take away these multi patterning DUV strategies, which is also true for DRAM."

As it turns out, TSMC is very confident of the EUV tools and ASML's ability to supply them in quantities required for high-volume manufacturing, which is why it enables its customers to use EUV for up to over 20 layers.

Designed for both mobile and high-performance computing applications, TSMC's N3 will use FinFET transistor structures and will likely be a 'long' node that will be used for many years to come. After N3 comes N2, which will rely on GAAFET (gate all around) structures and will require TSMC's clients and partners to significantly redesign their chips and IP. As a result, the transition to N2 and its successors will likely take some time.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Sources: ASML/SeekingAlpha, TSMC

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

jkflipflop98 Those tools are expensive in both money and time. They're incredibly complex and MASSIVE. You have to reinforce your fab flooring to hold the weight of one. You also have to install a cleanroom-approved gantry crane system in the ceiling for moving the chunks of the tool around during maintenance. It's crazy to see.Reply -

jasonkaler "it enables its customers to use EUV for up to over 20 layers "Reply

So more or less 20? Give or take. -

drivinfast247 Reply

Possibly. Within reason.jasonkaler said:"it enables its customers to use EUV for up to over 20 layers "

So more or less 20? Give or take. -

gabriel95 ReplyLBby said:Hi,

can you post a link to some documentary showing that ?

thx

EUV: Lasers, plasma, and the sci-fi tech that will make chips faster | Upscaled -

jasonelmore Intel also has several of these new EUV lithography scanners from ASML but can't even do 7nm. I think it says a lot about the quality of their engineering team.Reply