Intel Releases Itanium 9500 Poulson Manual

Intel has quietly published a reference manual of its upcoming Poulson Itanium processors.

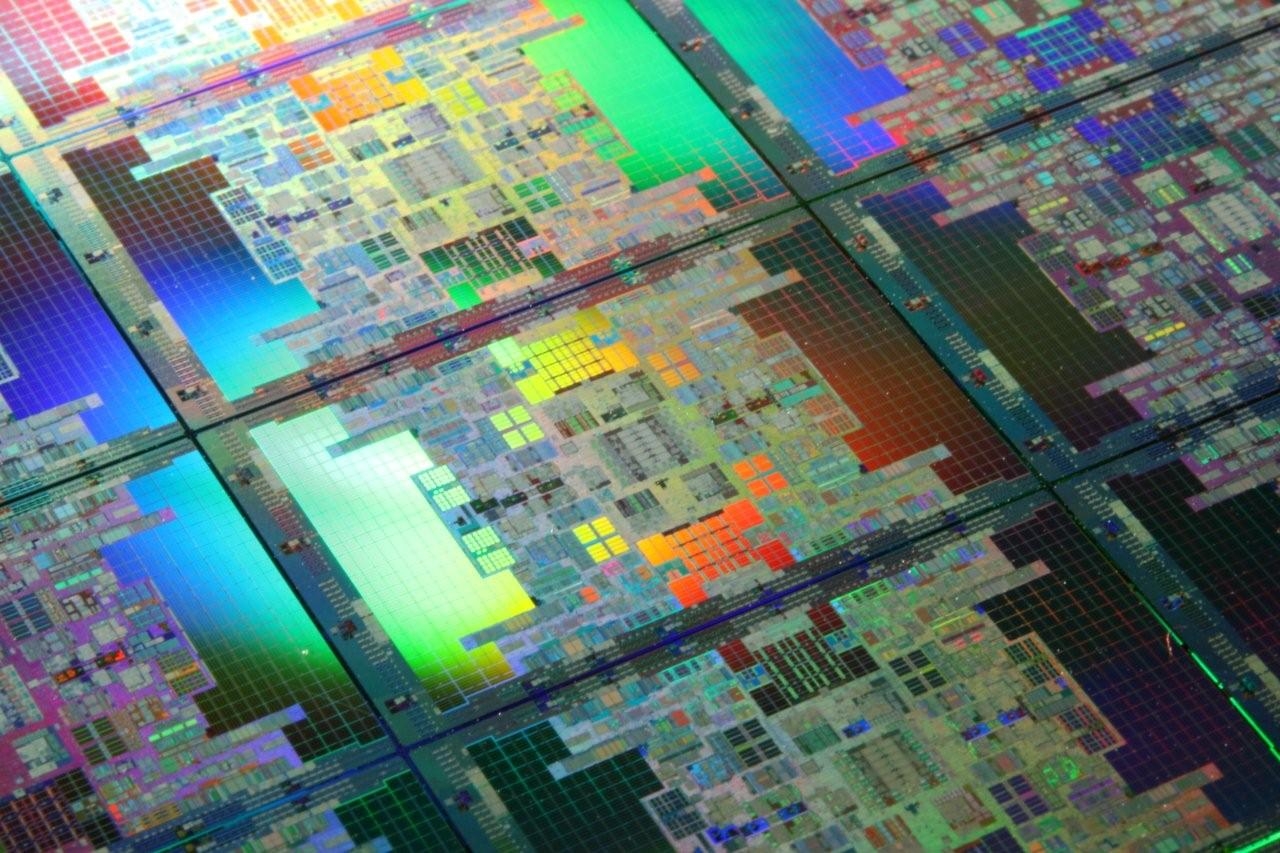

First spotted by the folks over at CPU World, the document provides detailed information about the 32 nm, 3.1 billion transistor CPUs.

According to the 512-page manual, there will be four eight-core versions of Poulson, the 9520, 9540, 9550 and 9560 models. The chip will replace the Tukwila-based Itanium 9300 quad-core series that was introduced in February 2010 and is manufactured in 65 nm. The die size will be 544 mm2, which is considerably smaller than the 699 mm2 of its predecessor.

Among the new features of the processor is Intel's Instruction Replay Technology, which allows the CPU to recover from pipeline errors much faster as the execution does not rely on an entire pipeline flush, but simply restarts at the last known correct position.

Article continues belowThe document also provides information about dual domain (front-end/back-end) hyper-threading, which makes its debut with Poulson. According to the manufacturer, the expanded hyper-threading approach, which will still allow two threads per physical processor, and the decoupled pipeline enable instruction fetch and instruction execution to operate independently and run much more efficiently: For example, the front-end can perform instruction fetch for either thread regardless of which thread the back-end is executing.

Intel was originally expected to launch Poulson sometime in Q2 of 2012.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Douglas Perry was a freelance writer for Tom's Hardware covering semiconductors, storage technology, quantum computing, and processor power delivery. He has authored several books and is currently an editor for The Oregonian/OregonLive.

-

fancarolina "First spotted by the folks over at CPU World, the document provides detailed information about the 32 nm, 3.1 billion processor CPUs."Reply

Processor ... I'm pretty sure that should be transistor. -

palladin9479 Itanium is low priority for development funds, it tends to be one to two years behind Intel's desktop offerings. And honestly I don't blame them, HP is the only one developing systems for Itaniums. Itanium doesn't compete with AMD it competes with IBM, Oracle (Sun) and their like in the HPC and enterprise world. These are specialized systems running very specific tasks with high cost software, Itanium's VLIW ISA just gets tore up. VLIW is bad design for a general purpose main CPU, good design for a DSP and GPU though.Reply -

teodoreh When Google started their business, they used... Celeron processors in order to achieve their goals. Anyone using exotic processors, just wastes his money nowadays..Reply -

blazorthon palladin9479Itanium is low priority for development funds, it tends to be one to two years behind Intel's desktop offerings. And honestly I don't blame them, HP is the only one developing systems for Itaniums. Itanium doesn't compete with AMD it competes with IBM, Oracle (Sun) and their like in the HPC and enterprise world. These are specialized systems running very specific tasks with high cost software, Itanium's VLIW ISA just gets tore up. VLIW is bad design for a general purpose main CPU, good design for a DSP and GPU though.Reply

Itanium uses EPIC, not VLIW. It's similar, but not the same, granted it still doesn't do too well. VLIW and it's direct derivatives seem to be bad for any workload that isn't embarrassingly parallel and without dependencies, not just poorly in general-purpose GPU workloads. Well, that is if AMD's VLIW GPUs are to be considered. -

mayne92 Fancarolina"First spotted by the folks over at CPU World, the document provides detailed information about the 32 nm, 3.1 billion processor CPUs."Processor ... I'm pretty sure that should be transistor.Yeah, I found that line interesting at first.Reply

Who's the editor for Toms again? -

palladin9479 Reply9380512 said:Itanium uses EPIC, not VLIW. It's similar, but not the same, granted it still doesn't do too well. VLIW and it's direct derivatives seem to be bad for any workload that isn't embarrassingly parallel and without dependencies, not just poorly in general-purpose GPU workloads. Well, that is if AMD's VLIW GPUs are to be considered.

EPIC is just HP / Intel's implementation of the VLIW design concept.

http://en.wikipedia.org/wiki/Very_long_instruction_word

Very long instruction word or VLIW refers to a processor architecture designed to take advantage of instruction level parallelism (ILP). Whereas conventional processors mostly only allow programs that specify instructions to be executed one after another, a VLIW processor allows programs that can explicitly specify instructions to be executed at the same time (i.e. in parallel). This type of processor architecture is intended to allow higher performance without the inherent complexity of some other approaches.

Traditional approaches to improving performance in processor architectures include breaking up instructions into sub-steps so that instructions can be executed partially at the same time (pipelining), dispatching individual instructions to be executed completely independently in different parts of the processor (superscalar architectures), and even executing instructions in an order different from the program (out-of-order execution). These approaches all involve increased hardware complexity (higher cost, larger circuits, higher power consumption) because the processor must intrinsically make all of the decisions internally for these approaches to work. The VLIW approach, by contrast, depends on the programs themselves providing all the decisions regarding which instructions are to be executed simultaneously and how conflicts are to be resolved. As a practical matter this means that the compiler software (the software used to create the final programs) becomes much more complex, but the hardware is simpler than many other approaches to parallelism.

Any ISA that pass's multiple instructions as a single word to the CPU is a VLIW ISA. VLIW isn't a set of instructions, its just a concept / technique to implement ILP. This is also why GPU's are VLIW processors, even if they use different terminology's their still implementing multiple instructions as a single instruction word. Nearly every DSP in the world is also a VLIW CPU, for these same reasons. -

palladin9479 Reply9380516 said:Wait, didn't they give up on Itanium?

No, although its market share is rather low. HP is the only OEM really building Itanium systems and the overwhelmingly run HP-UX. Mostly banks and other financial institutions have special software written for those HP systems.

The HPC world is very very slow to change, you tend to swap our your core hardware once every five to seven years and then you only swap it with stuff that has been out for a year or more (reliability is a major factor). The hardware cost is minor compared to the software and support costs. -

QEFX mayne92Yeah, I found that line interesting at first.Who's the editor for Toms again?Reply

Tom's has editors?