Intel’s Upcoming Gracemont Microarchitecture to Support AVX, AVX2, and AVX-VNNI

Intel discloses some additional details about Alder Lake: AVX2 & AVX-VNNI Support

Intel’s small low-power cores for client system-on-chips have always featured rather decent functionality, but have never supported the instructions required for various high-performance computing or media encoding/decoding workloads to minimize their sizes and power consumption. This is going to change with upcoming Gracemont cores that will support AVX, AVX2, and AVX-VNNI instructions.

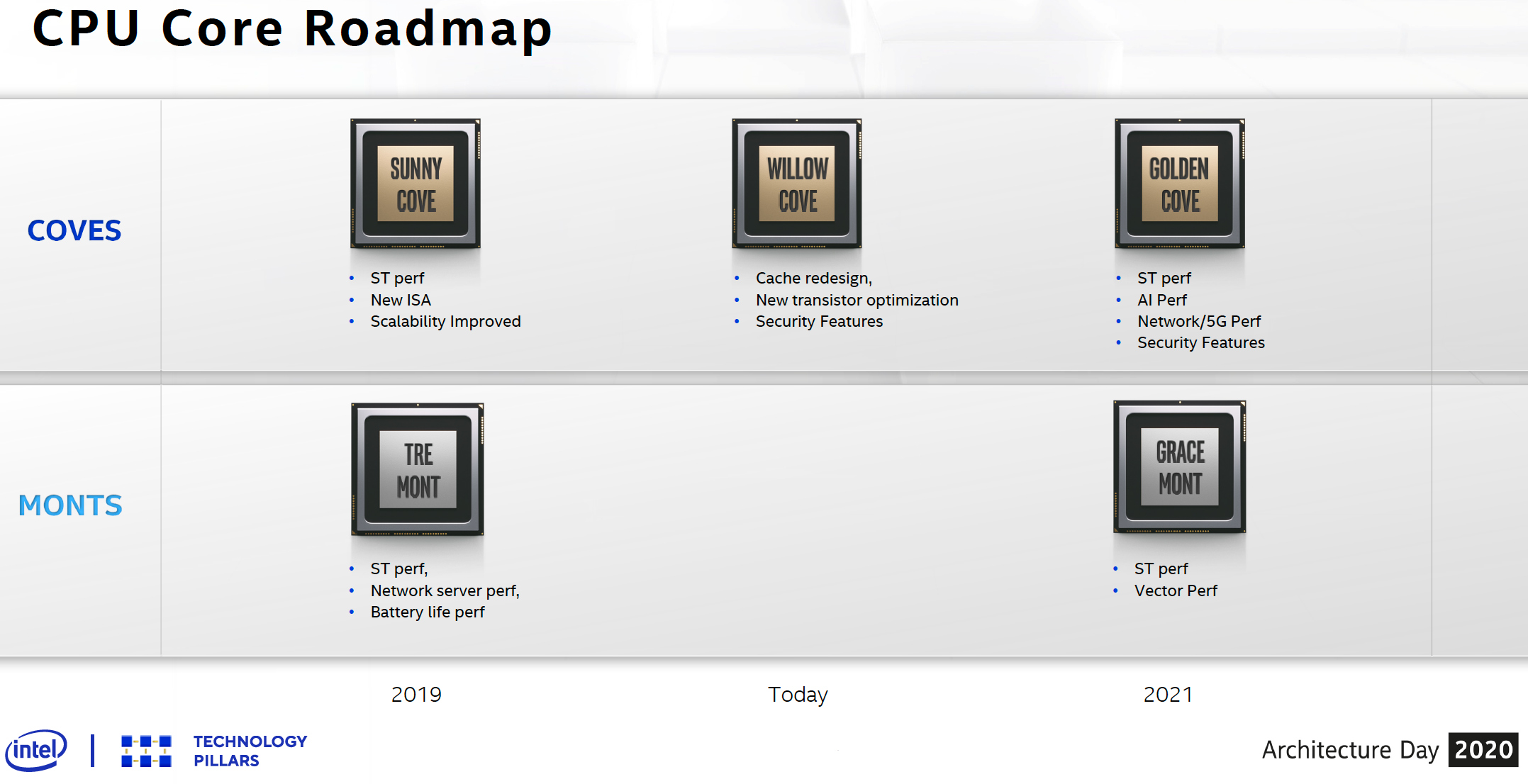

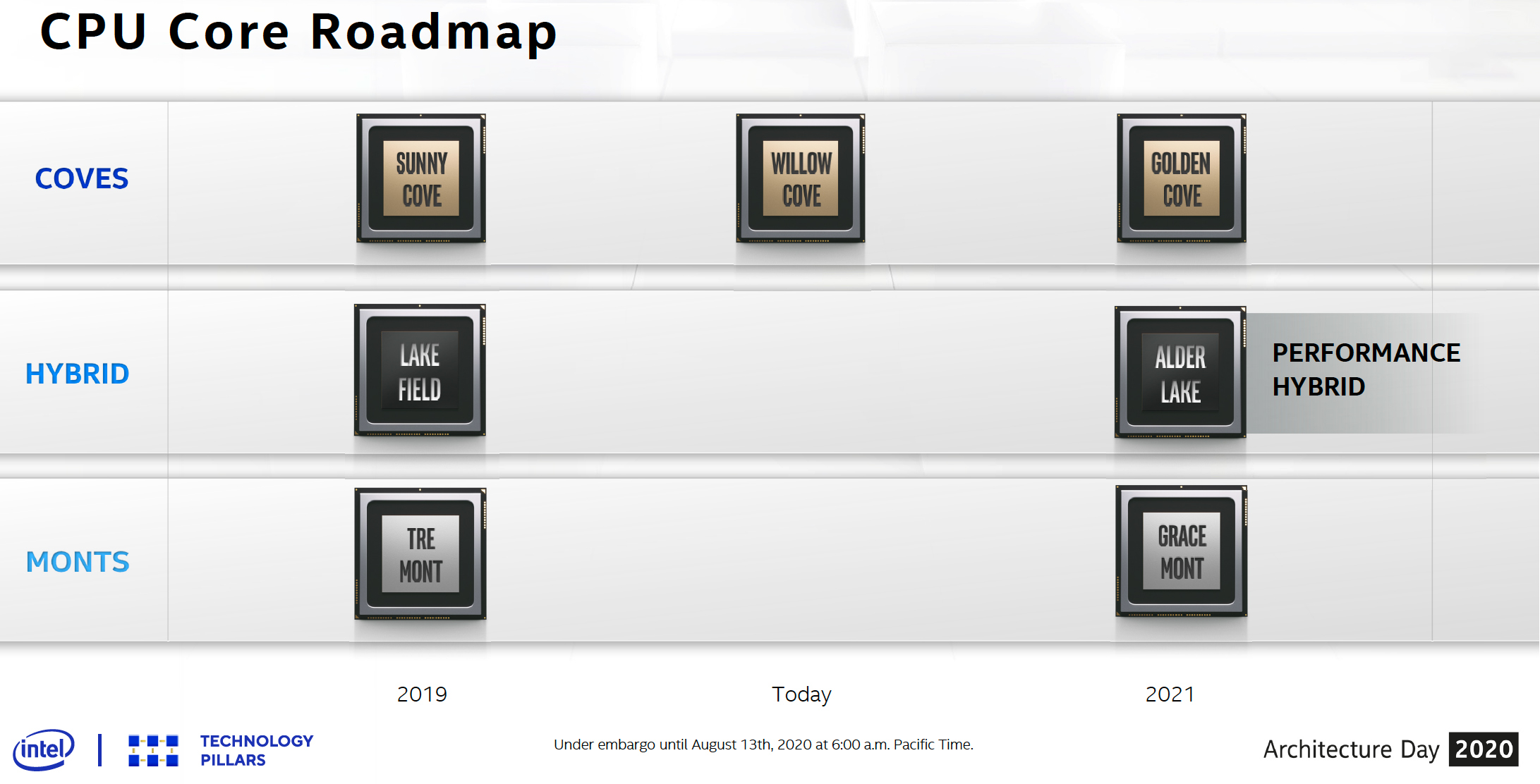

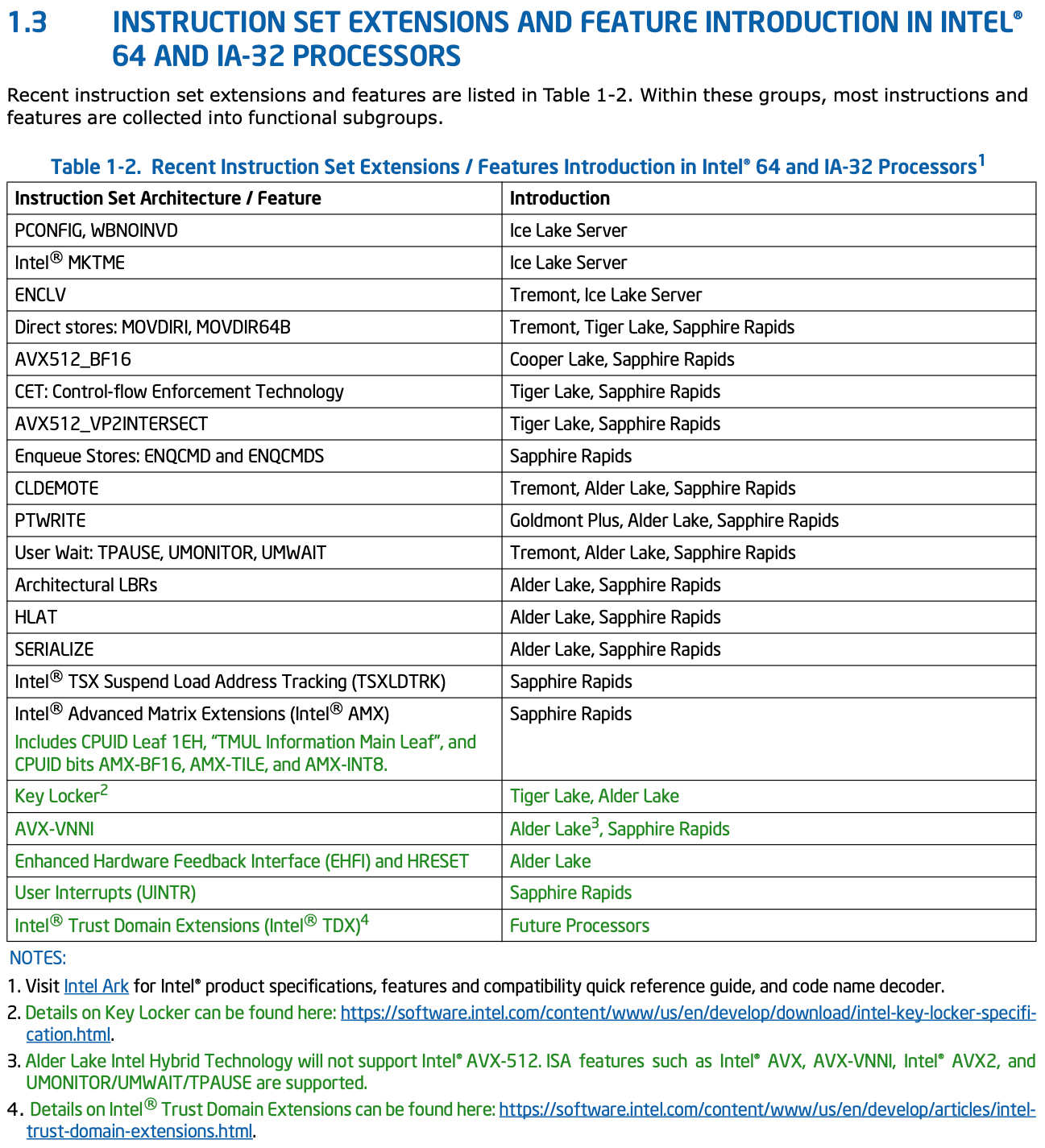

Intel recently updated its Architecture Instruction Set Extensions and Future Features Programming Reference document for software developers and revealed some additional details about its upcoming codenamed Alder Lake processors. These CPUs feature high-performance Golden Cove cores as well as low-power Gracemont cores along with Intel’s Hybrid technology that allows to switch between cores. (via Intel / David Schor/Twitter)

As it turns out, the ‘Alder Lake Intel Hybrid Technology will not support Intel AVX-512’, so the CPU will not be able to offload select AVX-512 workloads from its Golden Cove cores to Gracemont cores. Meanwhile, all cores used in Alder Lake will support AVX, AVX-VNNI, AVX2, and UMONITOR/UMWAIT/TPAUSE capabilities.

Intel’s AVX-512 hardware is known to be power hungry and such instructions yet have to be widely supported by client PC applications, so it hardly makes a lot of sense to add support for such instructions to low-power cores. Meanwhile, ‘typical’ 256-bit AVX instructions are rather popular, so Intel decided that it made sense to insert their support to its Gracemont microarchitecture. Unfortunately, Intel does not disclose details about implementation of its AVX/AVX2 support by Gracemont. Normally, a fully-fledged AVX2 implementation requires a fairly significant enhancements of the whole execution engine, which leads to die size increases.

In addition to existing AVX and AVX2 instructions, Intel’s Alder Lake and Sapphire Rapids CPUs will support AVX-VNNI (vector neural network instructions) for deep learning that will complement AVX512-VNNI supported by Intel’s higher-end CPUs.

The addition of AVX support to Gracemont will enable Intel to execute fairly performance-demanding applications using its low-power cores without firing up higher-performance Golden Cove cores. Furthermore, assuming that it will be possible to use both types of cores simultaneously, smaller cores will be able to assist larger cores in cases where every bit of performance matters, which includes DL workloads. Meanwhile, Intel yet has to disclose all the details about its Alder Lake processors.

It should be noted that Intel’s ‘small’ cores used for its Xeon Phi processors for high-performance computing (HPC) applications support select AVX-512 instructions. In addition, these highly-custom Atom cores also supported four-way Hyper-Threading to maximize their throughput. Typically, the addition of AVX-512 necessitates to throw-in additional hardware and increase bandwidth of internal interconnects, which upsurges power consumption and increases die size. For example, Intel’s Xeon Phi 7200-series features a 3.67W ~ 4.44W TDP per core. By contrast, Intel’s ‘small’ cores in consumer 14-nm Gemini Lake CPUs have a TDP of 1.5W ~ 2.5W.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

It remains to be seen how the addition of AVX/AVX2 affects power consumption of Gracemont versus current-generation Tremont.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.