TSMC Exploring On-Chip, Semiconductor-Integrated Watercooling

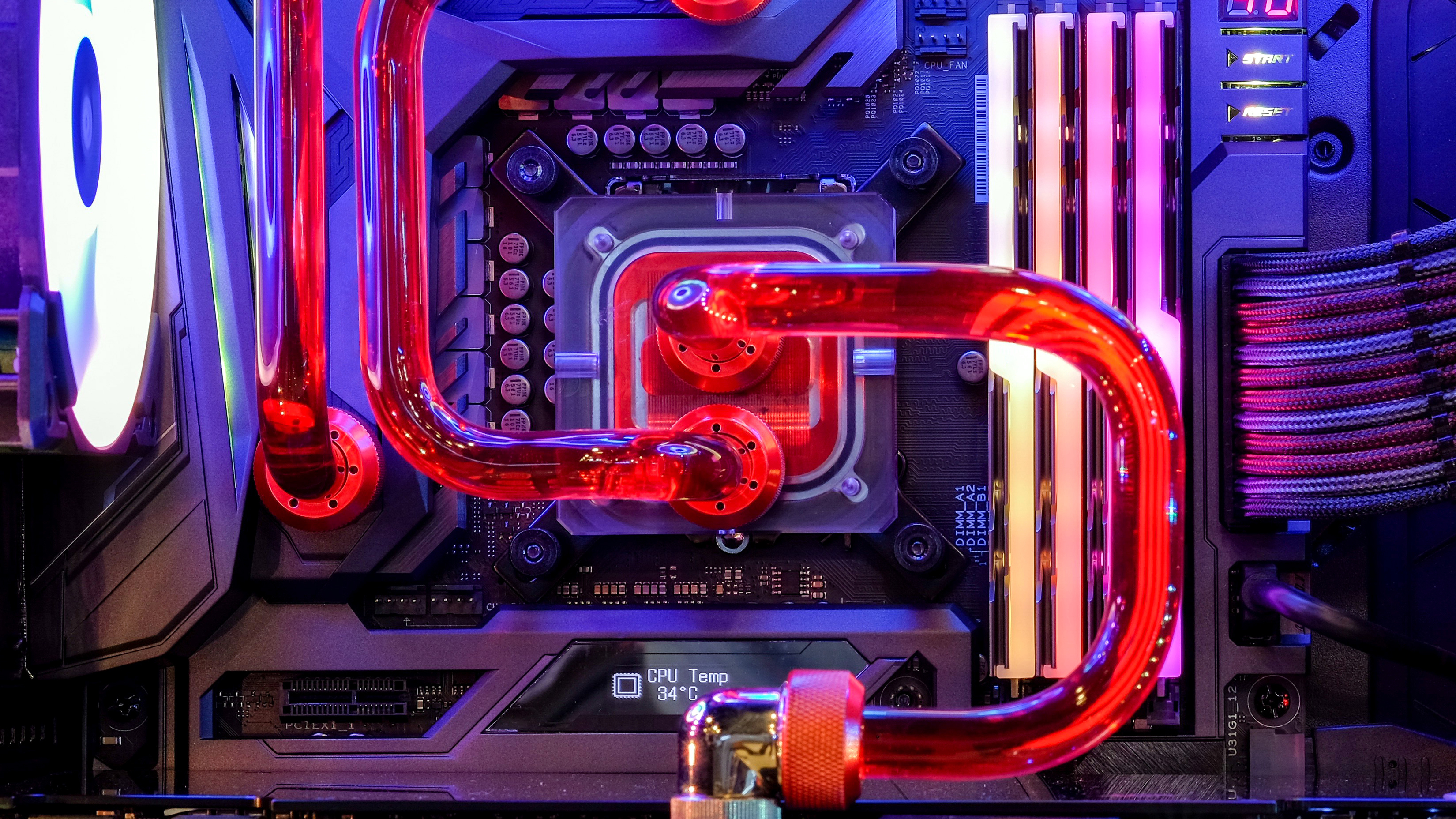

Future chips may feature watercooling integrated into the silicon.

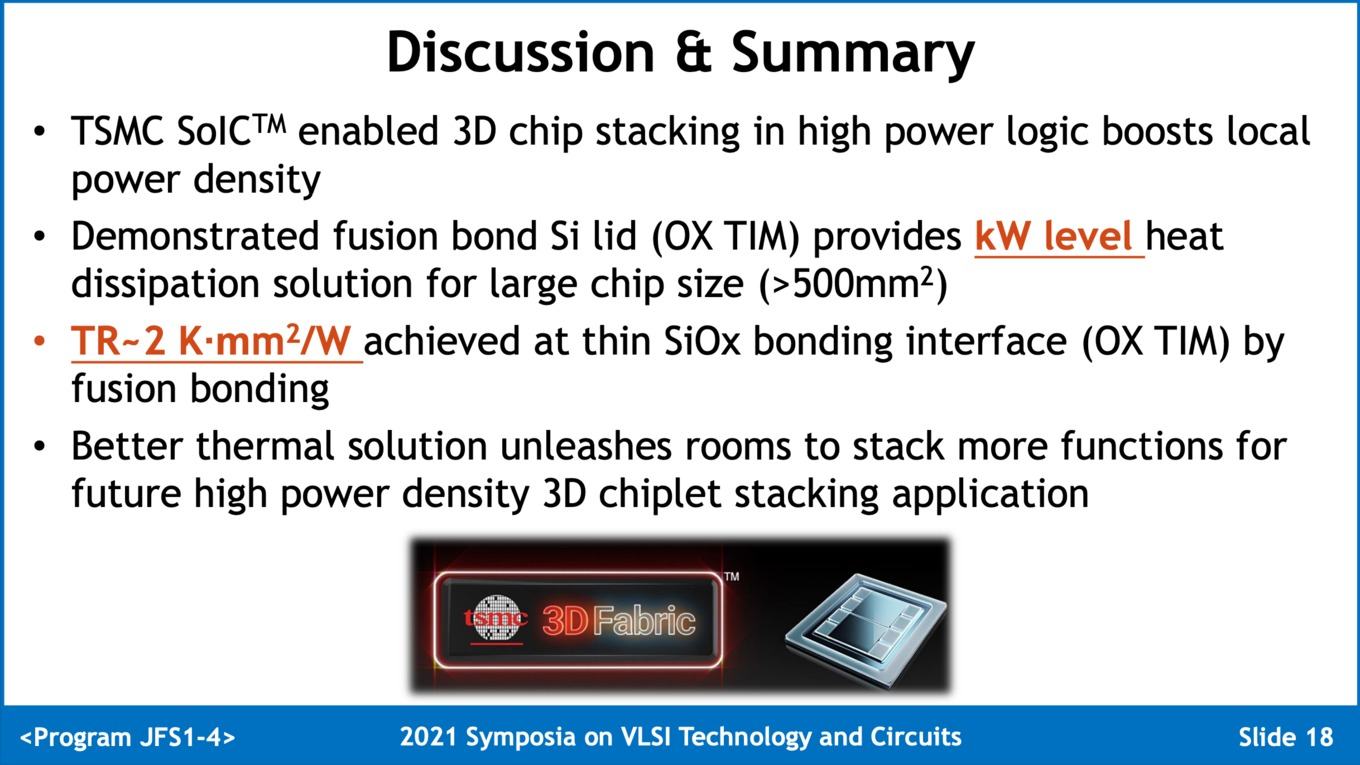

TSMC, at the VLSI symposium, recently presented its investigations into on-chip watercooling as a way to battle issues with heat dissipation. And it involves integrating water channels straight into the chip's design.

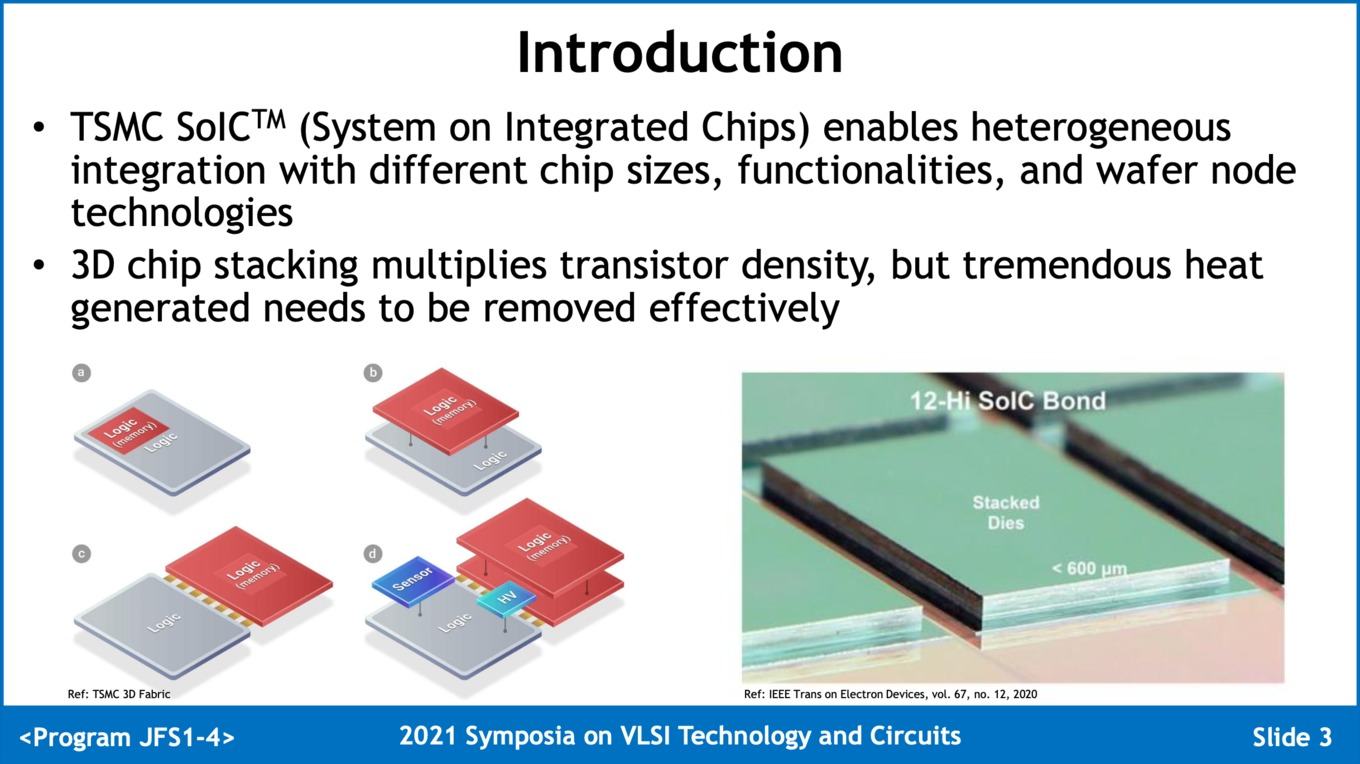

As transistors get increasingly compressed together due to denser manufacturing technologies and added vertical 3D chip stacking, temperature becomes an increasingly critical problem to address. TSMC's researchers think the solution is allowing water to flow in-between sandwiched circuits. It's an incredibly simple theoretical solution, but is an extremely difficult engineering feat to pull off safely --for the electronics, that is.

The mathematics are simple: Current cooling solutions typically work via direct contact with a given chip's heatspreader, direct die contact technologies, or full submersion in a non-conducting fluid. Of these, the first two solutions can only efficiently cool the layers they're directly in contact with, which brings huge problems for vertical chip stacking. The lower layers will have much more trouble dissipating their heat, with of damage or having to throttle, either of which would be bad for performance.

Article continues belowNot only that, but the top layer of the chip will have added strain from having to essentially carry the entire package's heat through to the dissipation layer. And liquid submersion, while efficient and likely better for stacked dies, is expensive and difficult to deploy in professional scenarios that are already geared for air or traditional water cooling.

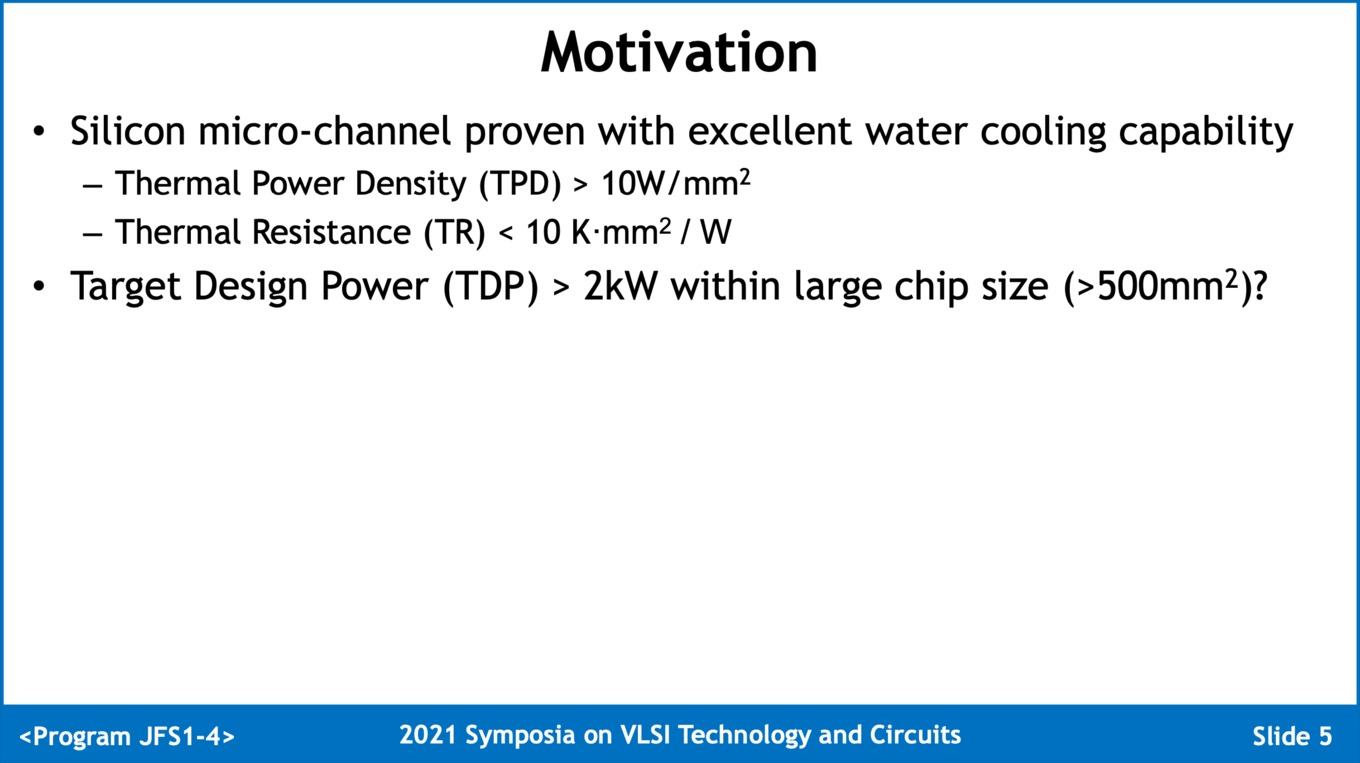

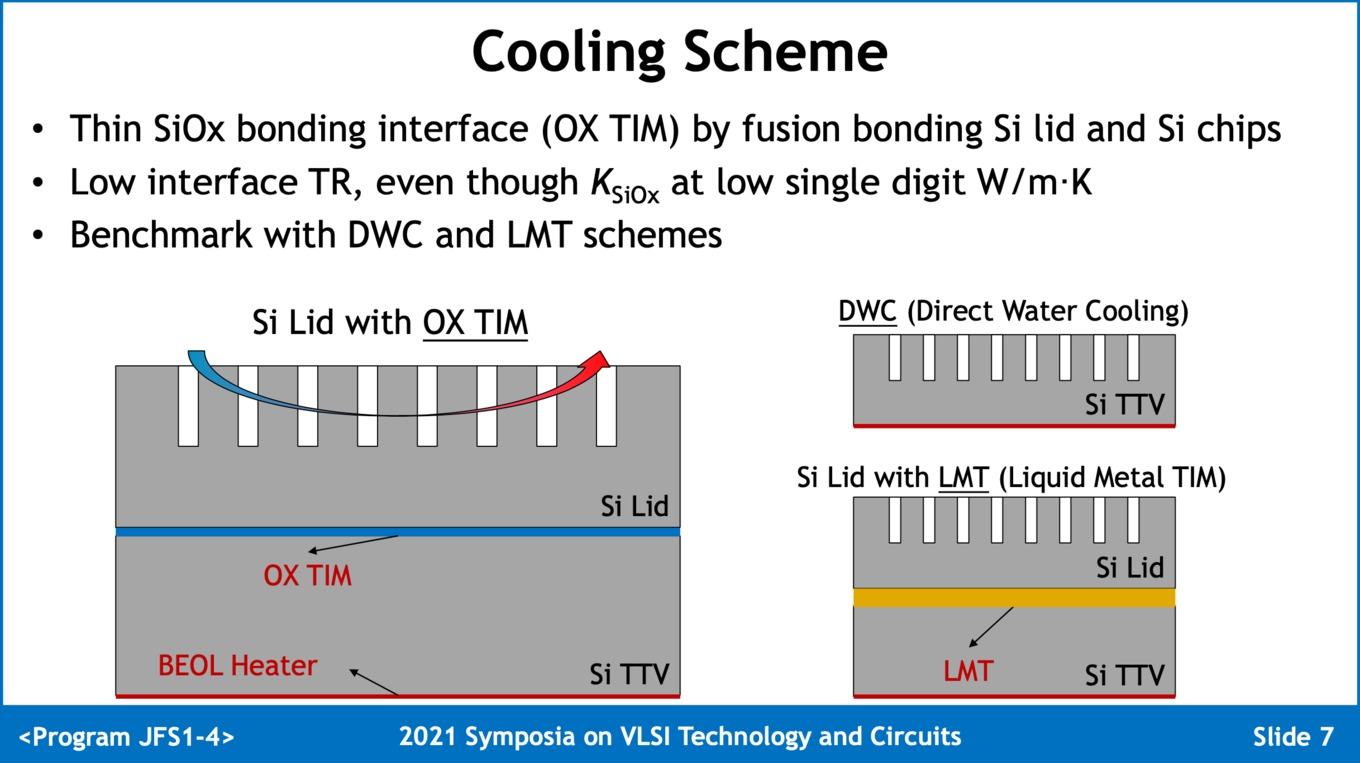

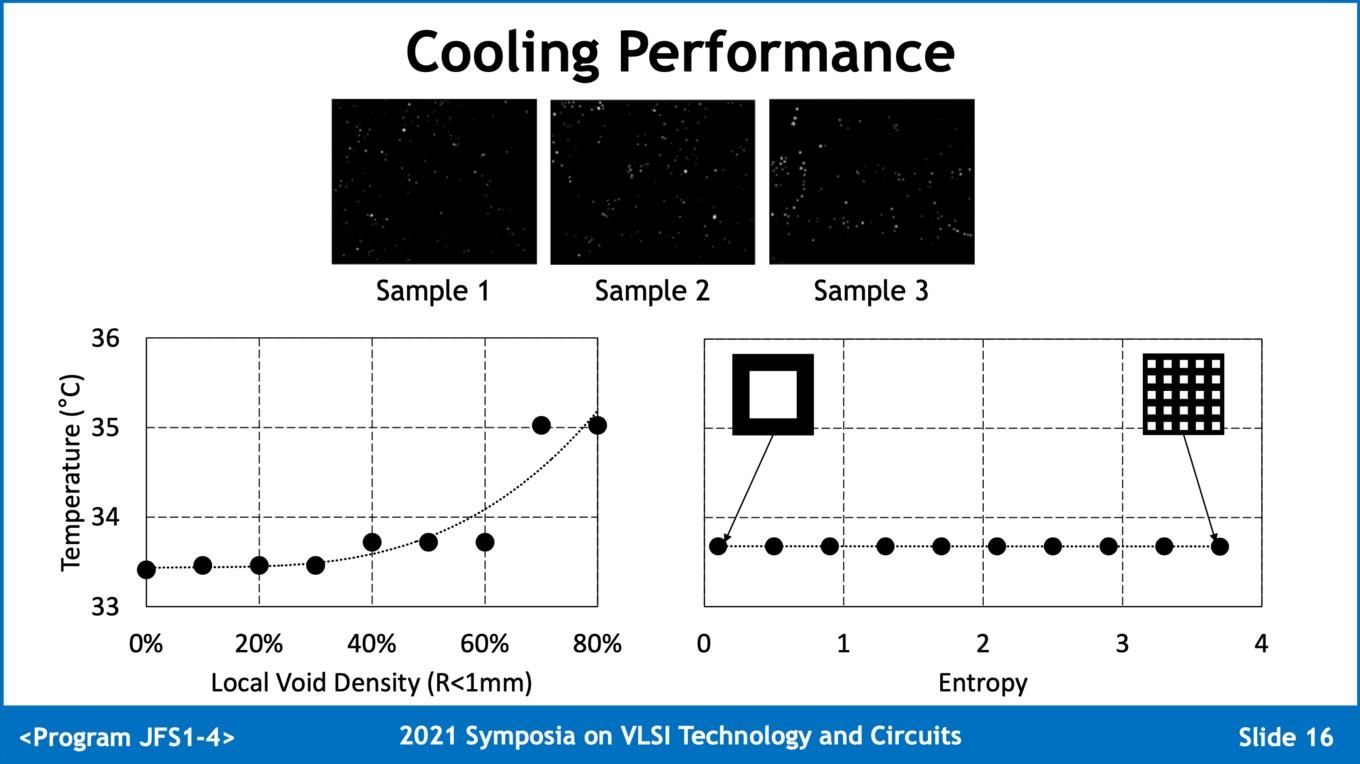

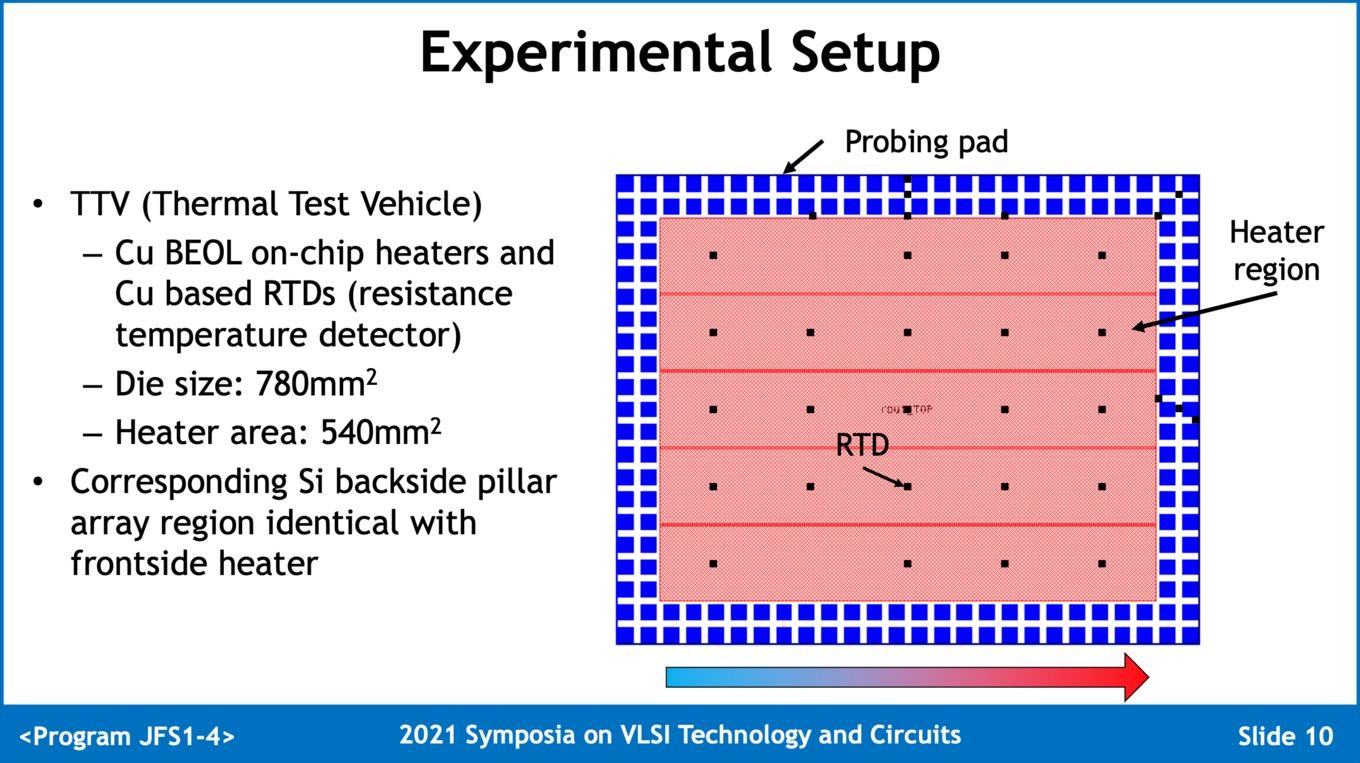

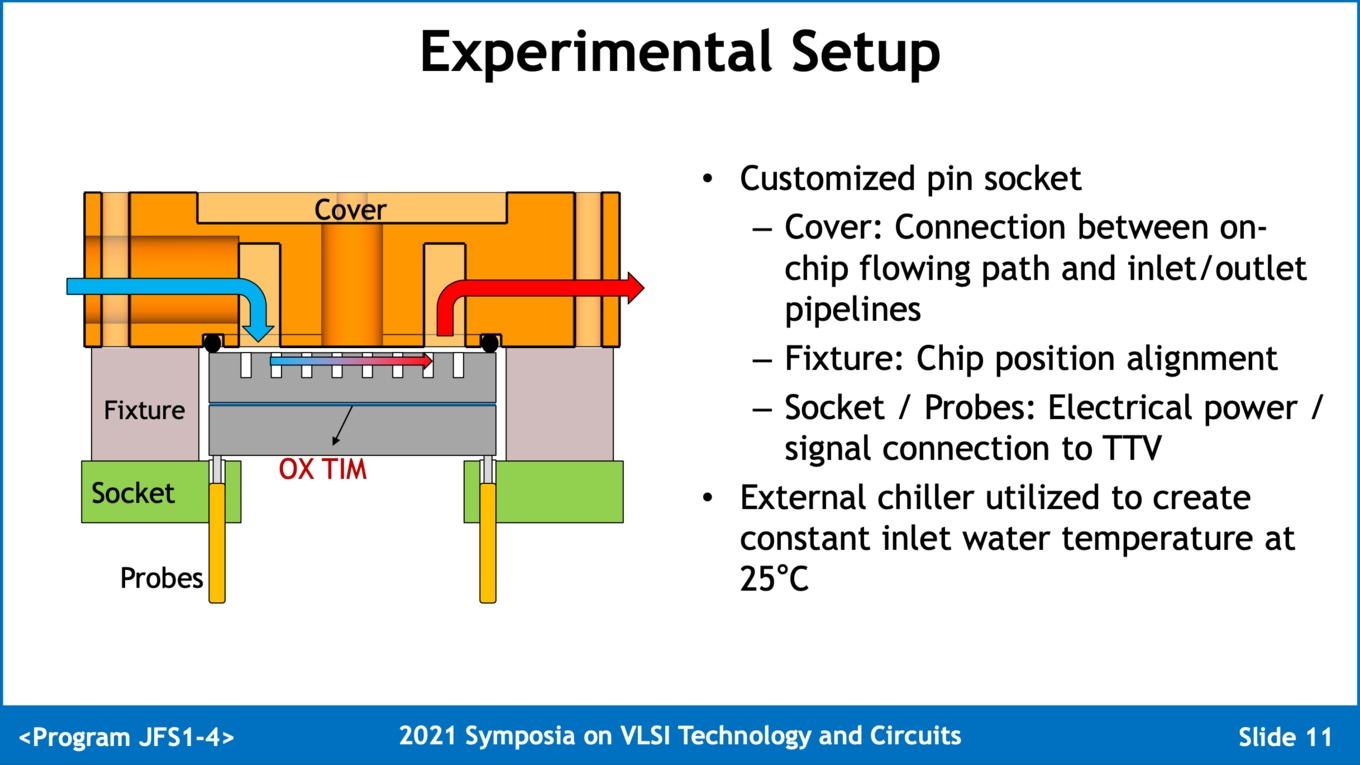

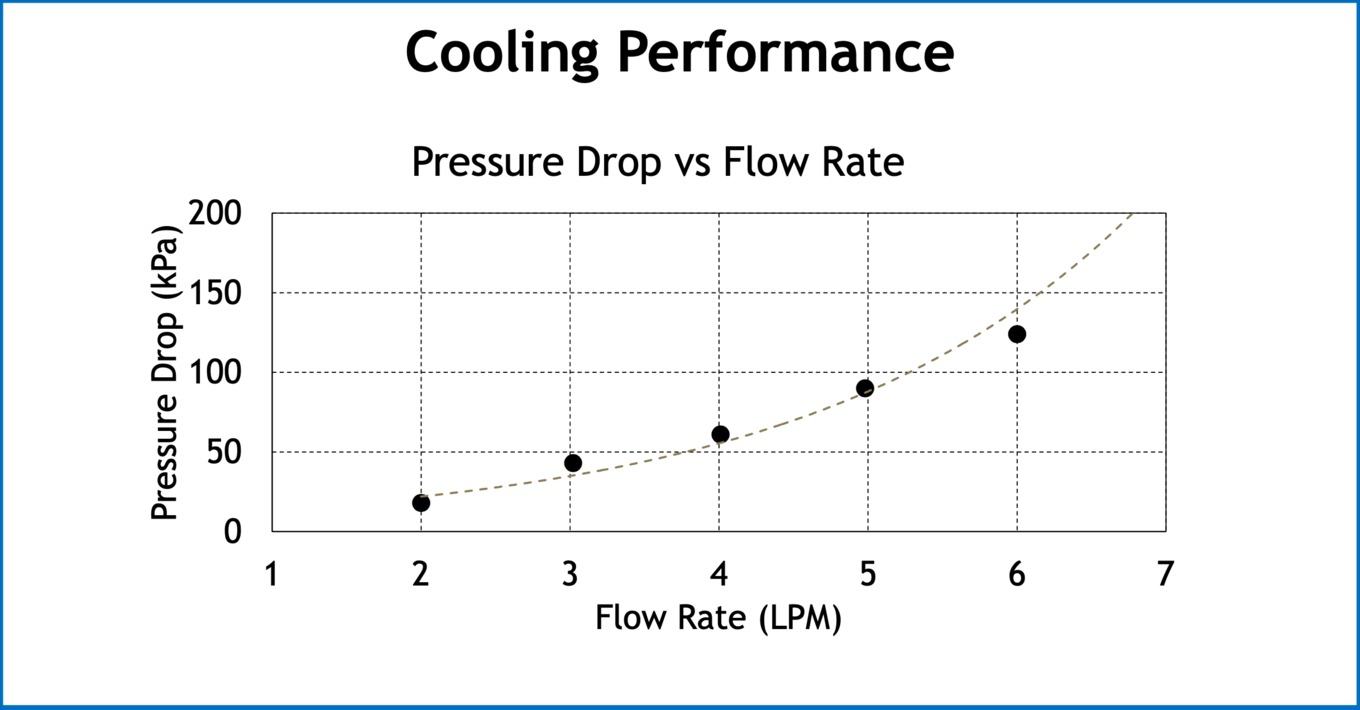

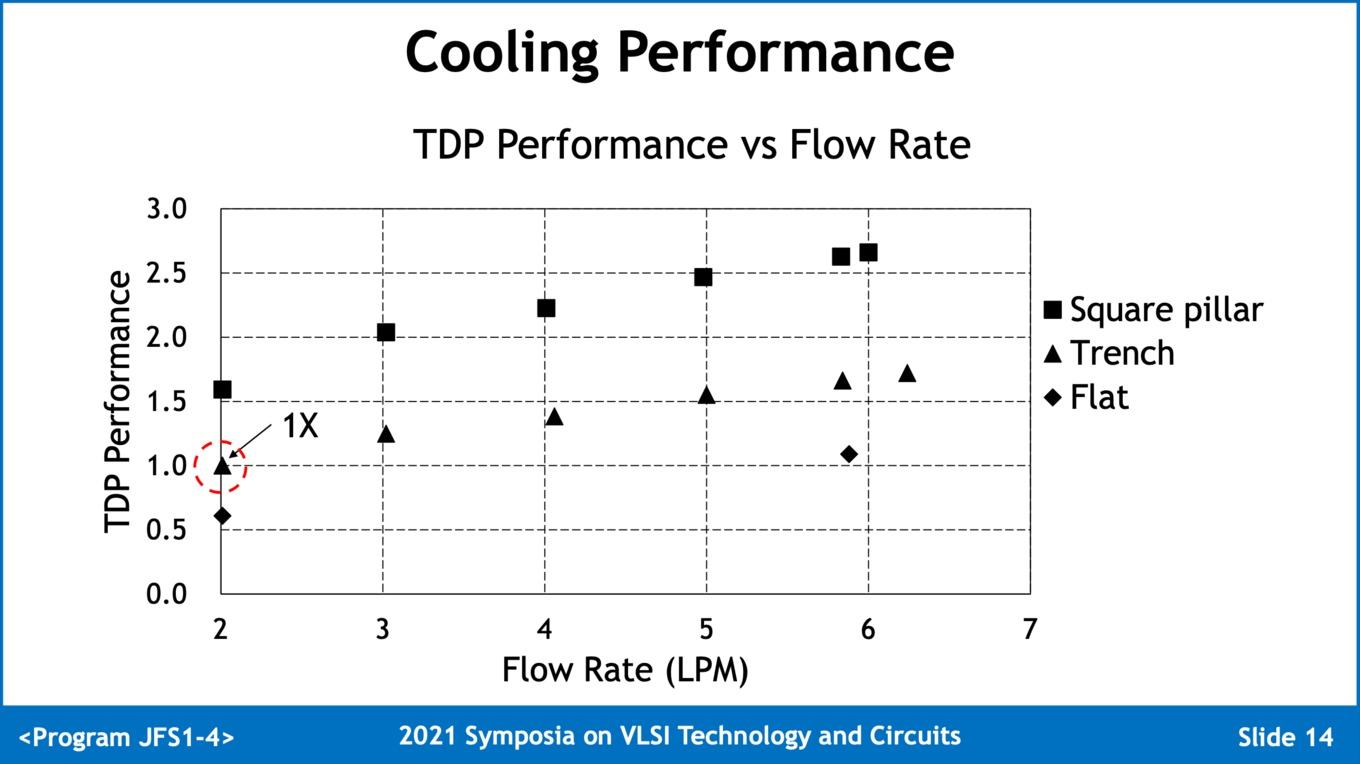

TSMC carried out testing on a dummy semicondutor - a Thermal Test Vehicle (TTV), which is essentially a heating element made out of copper - in controlled lab conditions. The company tested three types of silicon water channel integration in controlled conditions: It used a pillar-based channel, where water could flow around active semiconductor pillars to cool them down (think of water around an island); a design which featured a trench design (think of a river, controlled by its shores); and a simple, flat water channel on top of the rest of the silicon chip. The water was passed through an external cooling mechanism that chilled the water down to 25 ºC from its journey through the silicon chips.

The company further tested three types of water cooling designs: one with only direct water cooling (DWC), where water has its own circulating channels etched directly into the chip's silicon as part of the manufacturing process; another design with water channels being etched into their own silicon layer on top of the chip proper, with a Thermal Interface Material (TIM) layer of OX (Silicon Oxide Fusion) that carried heat from the chip to the watercooling layer; and lastly a design which swapped the OX layer for a simpler, cheaper liquid metal solution.

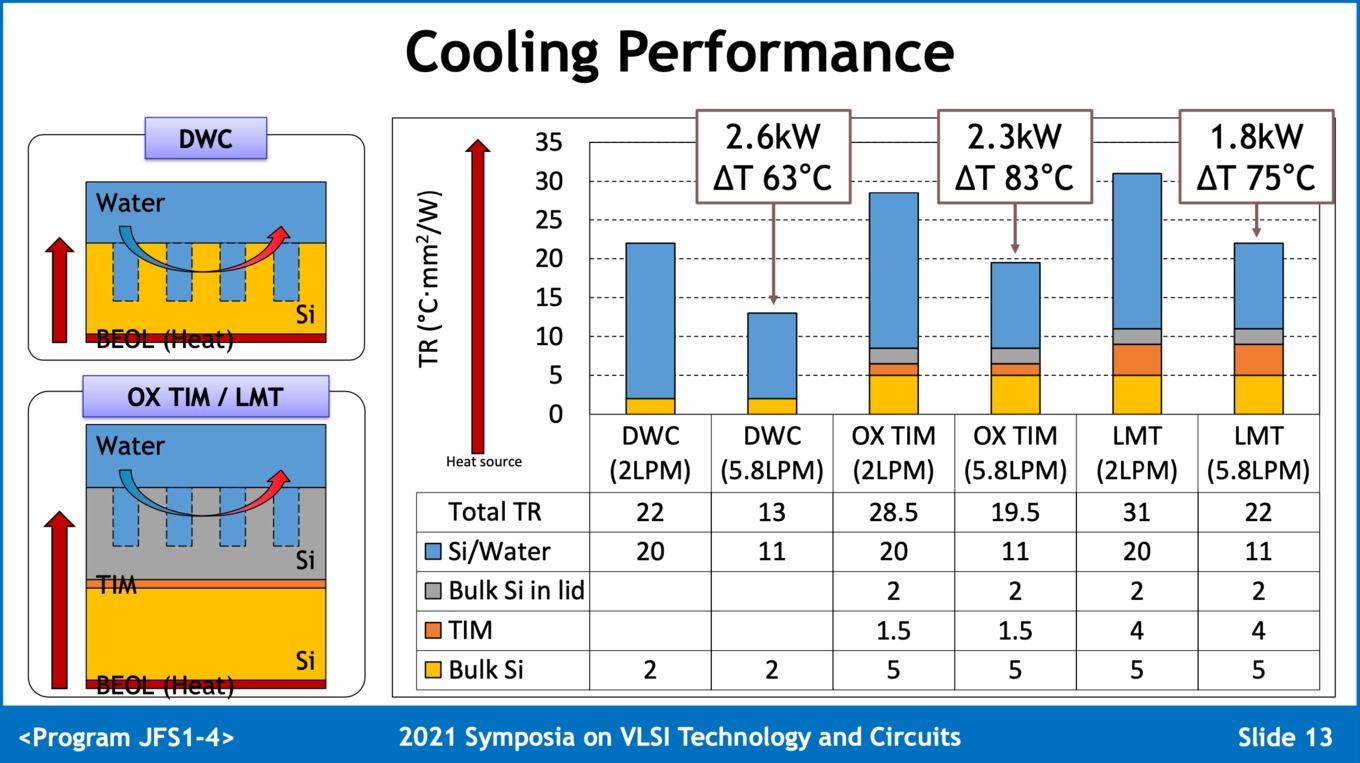

TSMC reported that the best solution was by far the direct water cooling method, which could dissipate up to 2.6 kW of heat and offered a temperature delta of 63 ºC. The second-best design was naturally the OX TIM-based one, which could still dissipate up to 2.3 kW of heat and offered a temperature delta of 83 ºC. The liquid metal solution came in last, still managing to dissipate up to 1.8 kW (temperature delta of 75 º C). Of all the water flow designs, the pillar-based one was the best by far.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Of course, it will take years until such exotic cooling solutions are adopted in the mainstream. But this is definitely one of the ways forward to enable continued increases in transistor density, continued improvement in the all-important performance-per-area metric, and for future 3D semiconductors.

Francisco Pires is a freelance news writer for Tom's Hardware with a soft side for quantum computing.

-

hotaru251 we knew yr or 2 ago some ppl were testing water cooled on chip cooling.Reply

and liek 6 yrs ago was when we heard ppl doing stuff related to FPGA

https://webcache.googleusercontent.com/search?q=cache:1PyD-oYF6HQJ:https://news.gatech.edu/2015/10/05/liquid-cooling-moves-chip-denser-electronics+&cd=3&hl=en&ct=clnk&gl=us&client=firefox-b-1-d

and last yr it was microchannels in microchips by the swiss

https://www.smithsonianmag.com/science-nature/researchers-craft-revolutionary-invention-cool-computers-180975807/

the results were fairly good.

Not a shock they are being looked at by the big boys now. -

escksu This is good. IMHO, chip stacking is likely the norm for future as we cramp more and more transistors into a die. There is a limit to how big it can get, so going vertical is the only way.Reply

Maybe high power CPUs will come with integrated waterblocks. -

ConfusedCounsel Wow. DARPA's Ice Cool Program did similar research. IBM modified one of their chips under the program. Boeing, Lockheed, Northrup, Raytheon developed their own variants under the program. Great to see the tech make it's way to civilian application.Reply -

Xajel ReplyConfusedCounsel said:Wow. DARPA's Ice Cool Program did similar research. IBM modified one of their chips under the program. Boeing, Lockheed, Northrup, Raytheon developed their own variants under the program. Great to see the tech make it's way to civilian application.

It will still take years to see it in consumer products, it will first be used in the server market as usual. Then for the HEDT market.

Two of the simplest issues I can think about is the mechanical support for consumers, I mean water cooling a PC hasn't been that much in the PC sector till we started to have an AIO solutions, custom loops is still not as consumer friendly as one might think of.

The second thing is the coolant, as we're heading towards even smaller grooves and structures even smaller than any modern micro-channel water block, the quality of the coolant and level of contamination will be crucial. Some engineers will for sure think about integrating a filter in the CPU/GPU package. -

AnimeMania It would be cool if they could figure out how to sandwich a diamond layer between each chip they stack, that should help with heat dissipation.Reply