Analysts Forecast TSMC To Double 5nm Output This Year

TSMC to focus on N5 this year as demand for chips grows.

Earlier this year Taiwan Semiconductor Manufacturing Co. outlined plans to increase its CapEx budget to $25 billion ~ $28 billion in 2021, many industry observers attributed the increase to building out 3-nm capacities in preparation to produce CPUs for Intel and other large customers. This is not quite the case, according to a forecast by China Renaissance Securities.

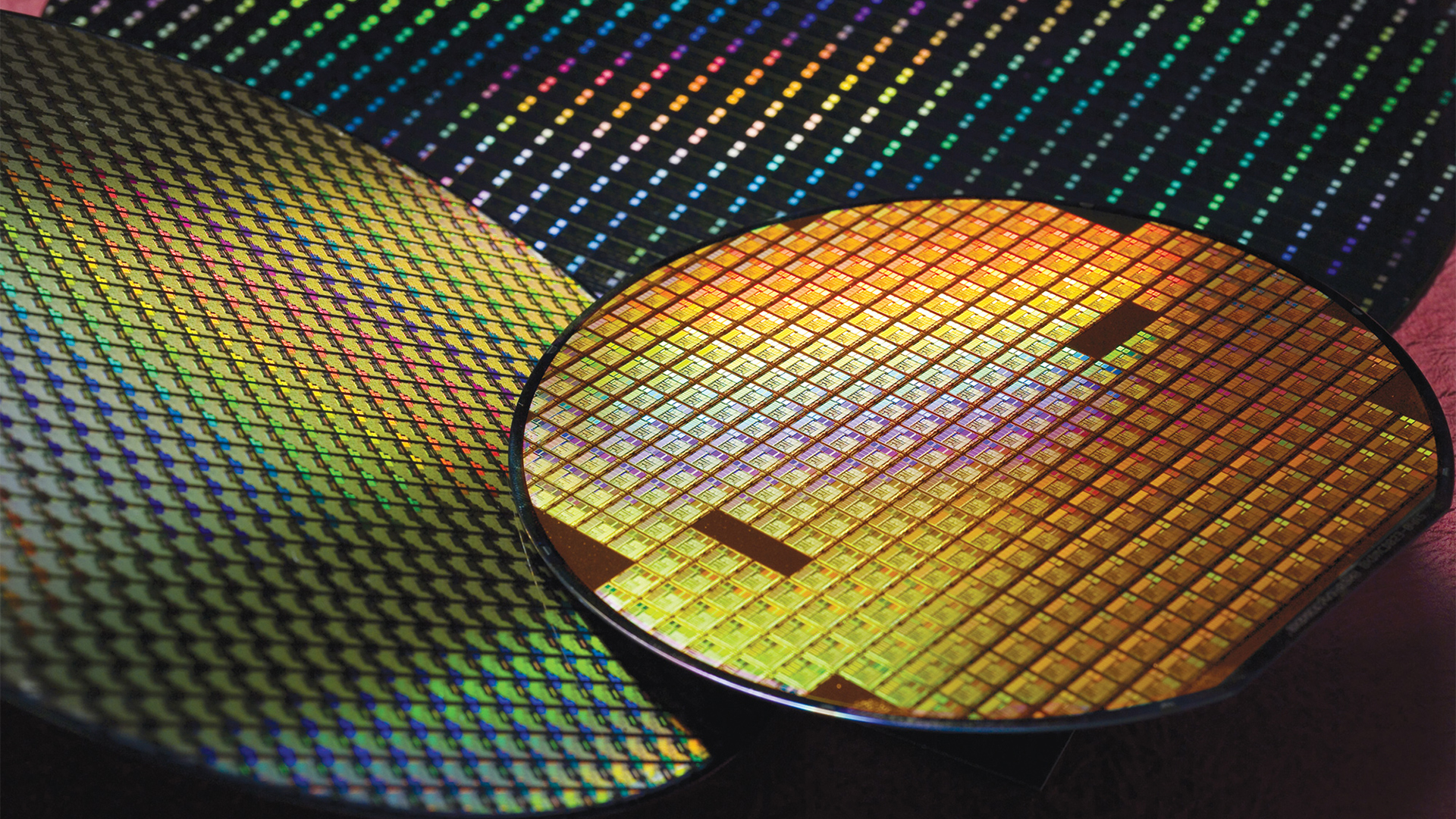

At present, TSMC's N5 capacity is around 55,000 ~ 60,000 wafer starts per month (WSPM), according to a forecast by China Renaissance Securities, which reiterated it earlier this week. Given the fact that TSMC can no longer serve Huawei's HiSilicon, the foundry's main and biggest N5 customer is Apple, which uses this technology to produce its A14 Bionic as well as M1 system-on-chips for its latest products. Apple is one of TSMC's key customers that has early access to the latest process technologies and is among the first to adopt the newest nodes.

Later this year other TSMC's customers, such as AMD and Qualcomm, are projected to start using the manufacturer's N5 fabrication process, which is when demand for this technology increases significantly. In a bid to satisfy demand for its N5 node in 2021 and in the following years, TSMC will spend the lion's share of its CapEx on expansion of its N5 capacity, the analysts say.

China Renaissance believes that TSMC will increase its N5 capacity by two times compared to today's levels, or to 110,000 ~ 120,000 WSPM, which essentially means that a year from now TSMC will have a GigaFab dedicated solely to N5 family, which includes N5, N5P, and N4 technologies. All of these processes are compatible on design rules, IPs, and SPICE levels, they will be used for years to come.

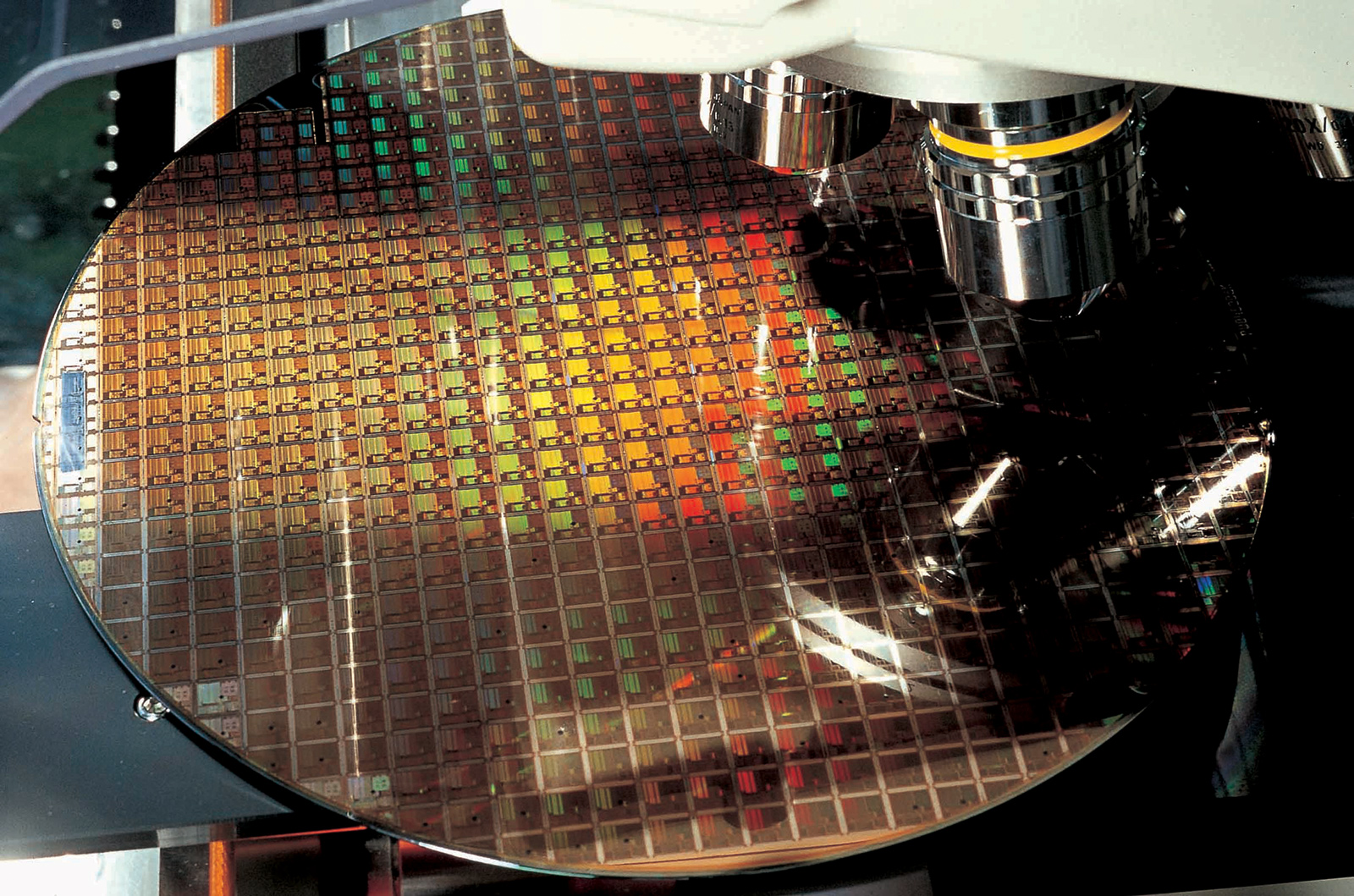

Another long node for TSMC will be its N3 (3 nm) technology. When compared to N5, the N3 process is expected to provide up to 15% performance improvement (at the same power and transistor count), or up to 30% power reduction (at the same speed and transistor count), along with up to 20% higher SRAM density and up to 70% higher logic density. TSMC expects N3 to enter risk production later this year, whereas volume production is expected in the second half of 2022. TSMC says that the interest towards N3 is higher than the interest towards N5 and N7 at the same stage of development (i.e., five to six quarters before formal launch).

Keeping in mind that N3 will not be needed for high volume manufacturing (HVM) for another year, it is logical for TSMC to spend big on N5 in calendar 2021 rather than prep for N3 in 2022 just now. The company is still expected to build a pilot N3 line with a capacity of around 10,000 ~ 15,000 WSPM this year.

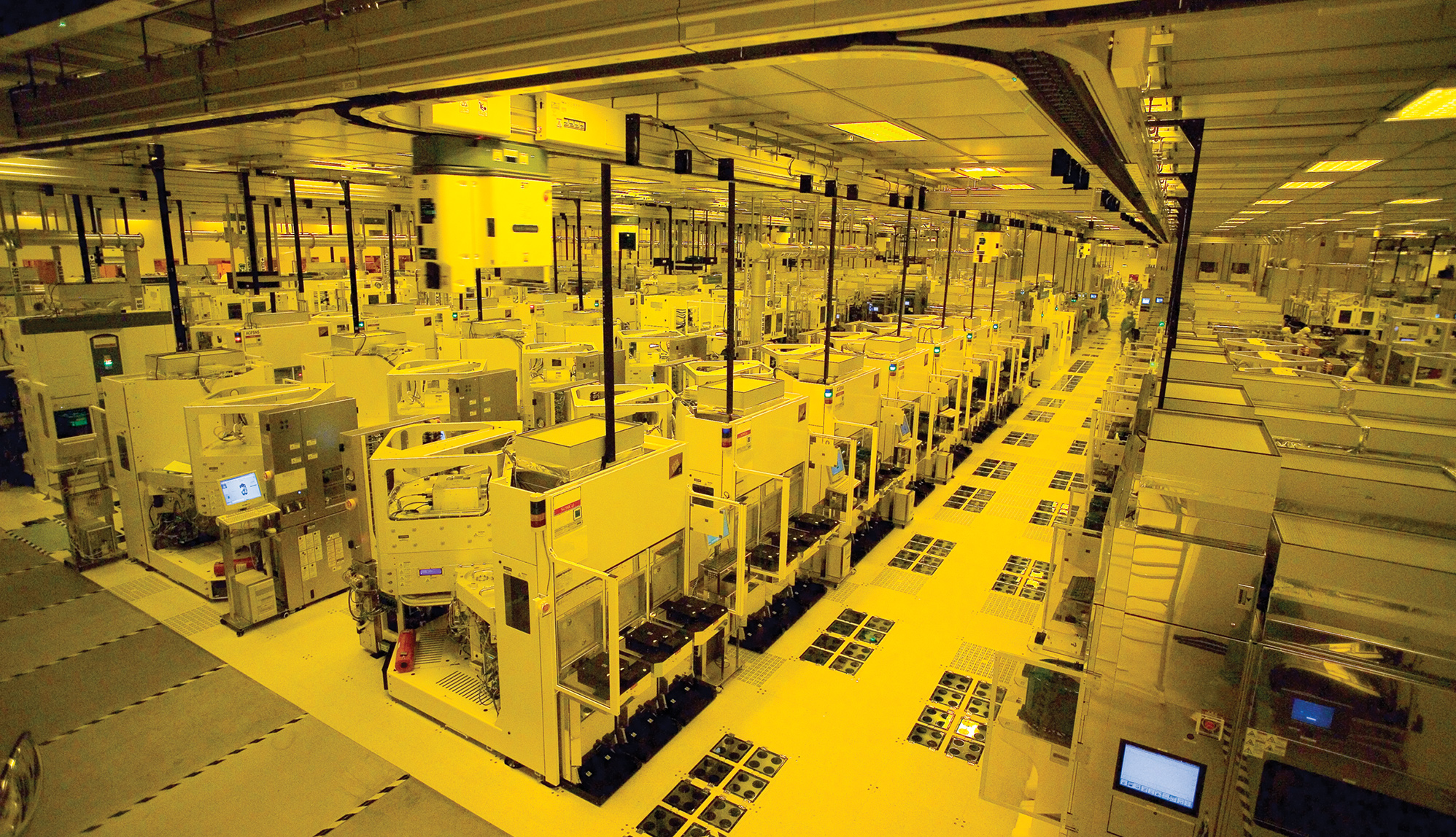

Both N3 and N5 nodes extensively rely on extreme ultraviolet (EUV) lithography. To expand N5 capacities and equip an N3 fab, TSMC will need to procure loads of ASML's Twinscan NXE scanners and deliver them. EUV tools take around six months to calibrate, so TSMC's expansion plans have to be very precise in a bid get the equipment ready exactly when it needs them.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

The main uncertainty for TSMC (and to a large degree the semiconductor industry) today is Intel's outsourcing plan. So far, the company has disclosed plans to outsource certain GPUs and SoCs to TSMC and it is believed that these chips will be made using TSMC's N5 or N7 nodes. Yet, it is unclear whether the chip giant intends to outsource production of its mainstream and performance CPUs to TSMC.

From transistor density point of view, Intel's 10nm SuperFin fabrication process (~100 MT/mm2) is comparable to TSMC's N7+ technology (~115 MT/mm2), but Intel's own technology might still be a better fit for the company just now as its CPUs have been tailored for this node. Meanwhile, TSMC's N5 has a significant advantage in terms of transistor density (~170 MT/mm2), which is something hard to ignore particularly when it comes to GPUs. When Intel is ready with its 7 nm technology (which is projected to double its existing transistor density) sometimes in 2023, it will still be behind TSMC's N3 by two or three quarters, which means that it will make sense for Intel to outsource some of its products to TSMC, exactly what the new chief executive Patrick Gelsinger told several weeks ago. Meanwhile, from CapEx allocation point of view it makes more sense for Intel to outsource a substantial portion of its products to TSMC and save on fabs.

"In the interest of engineering resource/CapEx allocation, Intel would be unlikely to run a hybrid internal-external foundry production for the same process, in our view; thus we expect any outsourcing decision will be a binary outcome (i.e., “winner takes all”, others take nothing)," wrote Szeho Ng, an analyst with China Renaissance Securities, in a note to clients. "Given that TSMC has clearly been well ahead of Intel in terms of EUV tech and capacity readiness, we expect CPU outsourcing for Intel to be the best path forward considering its current stance."

If Intel proceeds with the plan to outsource a significant portion of its production to TSMC in a bid to catch up with AMD in 2022, then it remains to be seen whether the foundry will have enough capacity to serve Intel and its existing customers, especially keeping in mind the fact that demand for N3 node may be higher when compared to demand for current nodes due to AI, HPC, and edge computing megatrends.

While it makes a great sense from financial point of view for Intel to CapEx save money and use TSMC's manufacturing capacities to build its products while concentrating on architectural innovations, it may not be exactly a good plan for Intel's long-term future. TSMC already has more EUV experience than Intel and it also has a certain standard-setting capability in the EUV ecosystem. If Intel does not catch up, then it will follow for many years to come and will not be able to use its superior fabrication processes as a competitive advantage over rivals.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

Co BIY Intel having control of their own production is allowing them to totally dominate the market right now despite the struggles. It is their major competitive advantage. I think if they choose to buy starts at TSMC it will be short term to deny them to competitors and will be carefully balanced against the danger of strengthening TSMC.Reply -

ginthegit Yes and no to dominating the market. They are able to control their own production, but with the Failure yields at the 10nm node, this is a big offset.Reply

The Success of Texas and TSMC and the others is still a kick in the nuts to intel who have failed to find a way to make the 10nm node work... They missed the point of the design. Coming out with a fancy 10nm 3D transistor, stacked on a lateral plane was a great theoretical Idea, but in practice, they have the problem of placing 48 layers of wafer and VIAs on top of a transistor that is too tall to take advantage of a die shrink. Yes its Transistors are equivalent to the 7nm node, but their vertical stack size has stuffed them as far as the multilayer PCB is concerned. It results in little advantage in the routing and the VIAs have to be more complex -

ginthegit ReplyAMD LOL said:What you your source for the "failure yields"?

Seems yields are pretty good, with "vanilla" 10nm in HVM for Ice Lake SP with SF and ESF being better.

For all we know half of Apple's 5nm are thrown away - since a Fab doesn't release actual production yields. One thing for sure the TMSC fabricated Nvidia A100 has not made any reductions to defect rate - as the current 80GB A100 is virtually identical to the launch 40GB A100s.

And all the yields in the world are meaningless if you can't source the materials to finish them to box ready status.

Eye roll. If official quotes are what you are looking for and the propaganda of the current press. then I guess as long as I can pay enough then I can prove anything. Heck I guess if I can come out with some "quotes" about the world being flat... does it make it flat... Pfft

Lets assume you like me owned a business. Most of our business is about keeping the ear to the ground and making conjecture of the sources you have, because, big money giants like Intel can't afford the bad press. Its like , we pay 100x the R&D that our little competitor pays... they were on their knees 4 years ago and now they are stomping all over us... Lies and deception is the new perception.

TSMC is nothing to do with Intel. In fact let me enlighten you on ASICs and PCB manufacturing and design I teach at College level Lol.

TSMC use a more traditional flat level approach to their Transistors. It was a wise and stable move. It did mean that the TSMC 7nm would be equivalent to Intels 10nm approach because hey ho, Intel not only wanted to go Finfet, but Phallic FinFET with their 3D stack of transistors where they would build them upwards. So in the same Lateral space, Intel can fit 3 Transistors where TSMC can only fit two....

Let me just give you a hint of something that you just don't get... The 3D FinFET design was Novel and inventive, but came with servere drawbacks and this is where Intel is in Deep Do do and this is why I know they are having yield problems and are now very eager to get to the 7nm conventional design and pretend their Novel idea never existed. So let me put my analystic type thoughts through to you... Intel has been stuck at the 10 nm node for .... HOW long? ... and still are not putting all its fabrication plants in the basket (which traditionally it does!) and has been criticized for being stuck in the dark ages of 14nm. So how does it mask the problems. It is pretending to be 14nm chipsets in 14nm and processors in 10nm yet the Graphics side of the chips are still 14nm. what does that tell you ....

Now what is cheaper, making the whole product 10nm or a half and half... Well Intel makes it out that this Part 10nm and part 14nm is for price for the consumers. Yet, to splice part 10nm and 14nm on a same die or grafted die is even more expensive as now they need an extra machine or two in the chain to either line up the spice and connect all the Via points and routing, or to put the same silicon through another process. This is more expensive, so Intel is on the Lie trail to save face.

The 10nm uses a sky scraper type lithography to fabricate is Novel 10nm tech, and this has created problems. Many of the chips can be 48 layers of spliced substrate material all etched separately and then stacked and interconnected with Via connections. But what good old Intel have a problem with is that the new vertical height of its monstrous transistors actually made this more difficult. They realized that stacking PCBs and Via connectors was a problem, because the new transistors made the layers too high and thus the novel idea turned into a nightmare... It means that now, their die has to have fillers to protect the new Transistor set to make it so the transistors dont get crushed in the stacking and binding process, and to make sure (like thermal paste does with processors) that the heat issues were not going to suffer, and hence the vertical size of the CPU die is larger than it should be. So they either risk destroying the transistors or they end up with no size advantage (which would be an obvious show of their fail), so they must go with the risk of potentially damaging the Processor in the bonding... But don't worry, its only the top and bottom layer (usually)... Or is it!???

Just check under the Lithographic progress chart for companies and progress and somehow Intel seems to be on the working and developed Fabrication of 7nm and 5nm already... So either that is true, and they are fabricating chips to put in your arm with the vaccine, or they are lying and struggling with the 10nm process under high risk of failures.

Your choice.. -

ginthegit ReplyAMD LOL said:"Lets assume you like me owned a business. Most of our business is about keeping the ear to the ground and making conjecture of the sources you have, because, big money giants like Intel can't afford the bad press. Its like , we pay 100x the R&D that our little competitor pays... they were on their knees 4 years ago and now they are stomping all over us... Lies and deception is the new perception."

Well, As I own 3 businesses and employ over 1000 people - and the spurious claim of owning a business - while the rest is just kinda /yawn

"TSMC is nothing to do with Intel. In fact let me enlighten you on ASICs and PCB manufacturing and design I teach at College level Lol."

Impressive, "own" a business and a teacher... I have designed and had manufactured quite a few PCBs for my home automation system... and didn't need to take a class for that.

"TSMC use a more traditional flat level approach to their Transistors. It was a wise and stable move. It did mean that the TSMC 7nm would be equivalent to Intels 10nm approach because hey ho, Intel not only wanted to go Finfet, but Phallic FinFET with their 3D stack of transistors where they would build them upwards. So in the same Lateral space, Intel can fit 3 Transistors where TSMC can only fit two...."

/yawn - and TSMC really knocked their long fragile supply chain out of the park. Phallic FinFET - that's a new one. Do you see phalluses in everyday scenes? Might need some professional help for that.

"Let me just give you a hint of something that you just don't get... The 3D FinFET design was Novel and inventive, but came with servere drawbacks and this is where Intel is in Deep Do do and this is why I know they are having yield problems and are now very eager to get to the 7nm conventional design and pretend their Novel idea never existed. So let me put my analystic type thoughts through to you... Intel has been stuck at the 10 nm node for .... HOW long? ... and still are not putting all its fabrication plants in the basket (which traditionally it does!) and has been criticized for being stuck in the dark ages of 14nm. So how does it mask the problems. It is pretending to be 14nm chipsets in 14nm and processors in 10nm yet the Graphics side of the chips are still 14nm. what does that tell you ...."

TL;DR

"Let me just give you a hint of something that you just don't get... The 3D FinFET design was Novel and inventive, but came with servere drawbacks and this is where Intel is in Deep Do do and this is why I know they are having yield problems and are now very eager to get to the 7nm conventional design and pretend their Novel idea never existed. So let me put my analystic type thoughts through to you... Intel has been stuck at the 10 nm node for .... HOW long? ... and still are not putting all its fabrication plants in the basket (which traditionally it does!) and has been criticized for being stuck in the dark ages of 14nm. So how does it mask the problems. It is pretending to be 14nm chipsets in 14nm and processors in 10nm yet the Graphics side of the chips are still 14nm. what does that tell you ...."

We still have not determined that Intel is having yield problems, your wall of text proved nothing. Analystic.. that's a new word - you make it up?

"Just check under the Lithographic progress chart for companies and progress and somehow Intel seems to be on the working and developed Fabrication of 7nm and 5nm already... So either that is true, and they are fabricating chips to put in your arm with the vaccine, or they are lying and struggling with the 10nm process under high risk of failures."

Intel has several processes in progress at any one time - 10nm "vanilla" is in HVM of MILLIONS of Ice Lake SP (yes Sapphire Rapids coming later this year, but the customer base for Ice Lake SP (VM farm mostly) is not the same as Sapphire Rapids). Their 10nm SF (big advance there is Cobalt which is needed at nano scale since copper becomes a resistor) is mostly the market dominating Tiger Lake and likely Nvidia's worst nightmare a 4 tile Xe HP compute GPU... And risk production started for 10nm ESF - as both that process and Intel's Full EUV 7nm are featured in the Xe HPC which is undergoing testing. Last I checked TSMC was not doing Cobalt and still only doing a couple of layers of EUV...

and the Anti Vax - WOW, just WOW. You Made my List - had I read that first, I would not have bothered to dignify your rambling circular logic with a response.

Good Luck in All Your Future Stupid Ventures - and those squiggly red lines under some words mean they are misspelled

My goodness, you are so full of yourself. Ok lets just pic apart your argument.

You says that you can Print PCBs at home... Wow, I'm impressed. This can easily be done with alkaline sets that I used to use 20 odd years ago. A messy mechanism and method, but yes, even a fool can make their own PCB's and generally only using thru'hole tech and usually employing 90 degree angles on their PCB on the traces that have problems with signal bouncing problems with high frequency signaling. The art of making complex PCBs is making them multilayer by stacking multiple micro thin slices of glass on top of each other, ultra thin lines and routing (with Via) that are way to small for your eyes to see. So if you are referring to the automated drilling systems that use simple coordinated Gerber files (which I use with my students programmed through PROTEUS), then how do you expect me to be impressed. You certainly have not produced a PCB with a reliable Soldermask or silkscreen, so I remain unimpressed.

Simply claiming they can make a PCB, because making an Ugly PCB is not hard at all and even my kids when they were young did it. So unless you are talking access to the complete process and not just the hand drawn stuff or the drilling cutter.

About spelling, I can be bothered to answer with much time or even correcting any mistakes on people like you, who don't have much knowledge on materials or ASICs. And when proper design terminology is SMT or "THRU'Hole" Tech (leet speak is considered good for an Engineering term) is used to describe componentry and tech on a board, I also don't give too much heed to spell checkers. In the engineering game, acronyms and terminology that is used is often flagged as red underlines, so I often ignore it when writing PCB design and manufacturer docs or comments. But obviously you are picking at straws.

And well done for reading about the Cobalt issue, but you clearly don't understand it. Copper still has a lower resistance than Cobalt, with the only exception of when the Copper etching and lining is poor allowing a diffusion of the copper into other materials (often tantalum) and thus spreading an impurity through the copper raising its resistance. And this is a problem when the fabrication process is not great and often causes yield problems (my point) when the lithographic lasers cause this process to happen. Intel classically uses the lie of calibration of the lasers can take months, but in their case Years.

My Assumption of the point of lower yields is based on Intel having a great track record of lying about all their failures in the past, and being as I am quite up on the knowledge of the RARE earth materials, being a proponent of trying to get them to use Carbon as a replacement, but they wont, because it means the Laser tech would have to change as Carbon is better than near all other materials for thermals, conduction and Quantum reactions, but as a result is also resistant to the laser and requires a complete change to how the fabrication is to be layered and set. It is also Immune to diffusion, if it is shaped correctly. But this would require years of revamping the tech (which they will eventually have to do) as the apparent size of an atom is 0.1nm for its current materials. Cobalt is a material that is similar to Graphene (carbon) in its properties, but still not as good over all. And yes you are wrong, Copper in its pure form has less resistance than Cobalt... Its just that Intel's design with its 10nm needs it because their copper always diffuses when trying to connect it to its Erected (hence the joke phallus) 3D Fin FETS that have 3 gates per lateral until space of TSMCs 2 gates... Yet because of the connection problems with the lateral transistor setup, they need a stronger material (cobalt to connect it and IMPROVE YIELDS.., DUH!

# 3 Businesses wow. I used to own just one before I got Cancer (probably due to not being careful around leaded solder for long periods. So now I am teaching because I can't do much more and won't even be employed by companies interested in my skill set. I was working in Dubai when I got sick, but even then I was training students, because I had enough of my ultra heavy schedule... My Business was small scale, so I am impressed if you are telling the truth... But I am guessing you are not.

Finally, as I said before many times, Intel rarely tells the truth, and even with my dealings with them, their techs were lying and twisting facts. When they were litigated constantly by AMD and other companies for stealing tech and unfair practices, I decided to hole up with AMD for products (despite their lack luster products). Now I am too old to care much, I don't even play games, but one of my Interests will always be PCB manufacture and design, especially as we near the Atomic limit. But How am I to produce evidence from the Great silicone Liars. So I have to go by my experience and how companies, like theirs lie to save face... And Intel likes to lie at the science level too... and few dare to question them.... Unless they can litigate.

If you trust to wait for Intel to tell the truth, then you'll be waiting for the Flat earthers to prove their point, because they are likely to happen at the same time. LOL