AMD’s Bulldozer And Bobcat Architectures Pave The Way

Ahead of its most significant processor redesign since 2003, AMD is talking about its Bulldozer and Bobcat architectures, both of which are expected in 2011. Will AMD be able to catch up, or even surpass Intel's lead? The future looks interesting, indeed.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

More On Bobcat

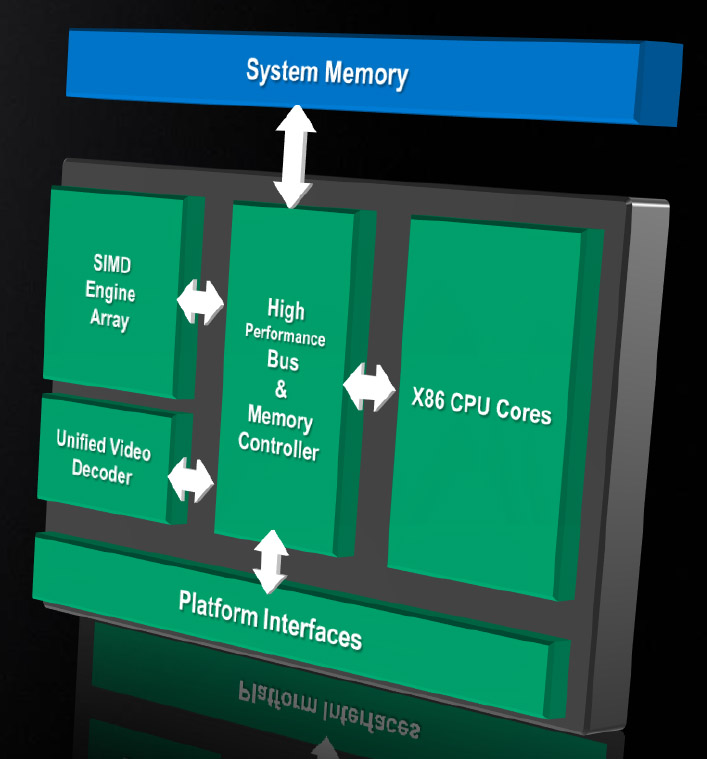

AMD had a bit more to add on its Bobcat design, unquestionably created with the Fusion initiative in mind. The focus here is on Bobcat as a technology, which AMD plans to use to create SoCs targeting specific markets—the first of which should be its Ontario APU, featuring on-die graphics processing, fixed-function video playback acceleration, a DDR3 memory controller, and the dedicated bus linking everything together.

AMD’s estimate here is retention of 90% of today’s mainstream performance (I’d certainly consider something in Athlon II territory reasonable) in less than half of the silicon area. That’s a figure we’ve seen AMD use in past discussions of Bobcat. But perhaps less known was how the company planned to achieve this.

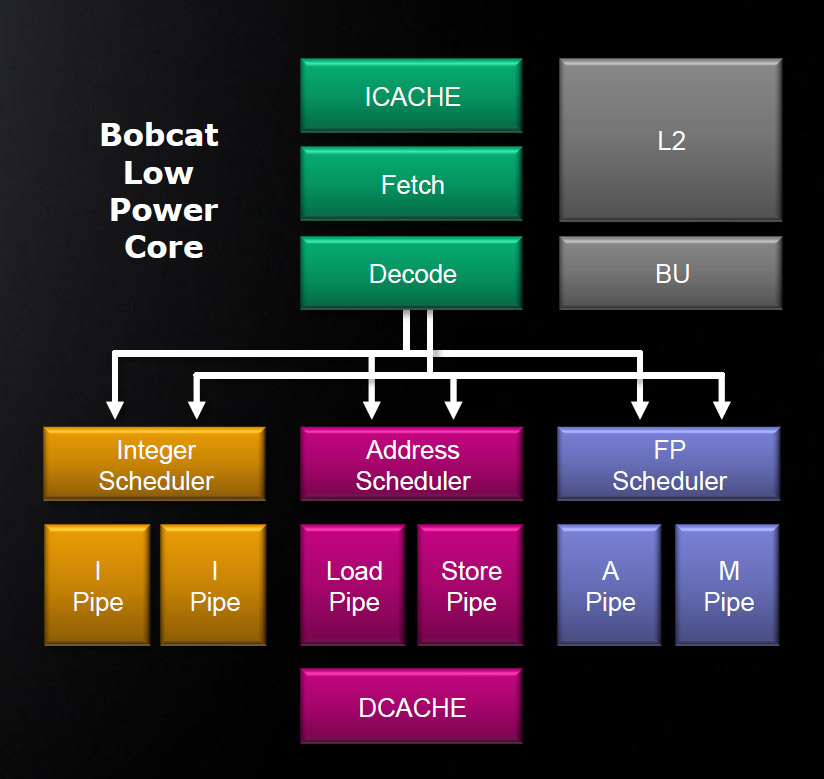

Details being discussed today include a dual-issue x86 decoder and out-of-order execution, perhaps enabling a performance advantage compared to Intel’s Atom CPUs. Bobcat will support SSE, SSE2, and SSE3, along with virtualization acceleration.

Beyond its performance implications, though, AMD repeats over and over that this is a sub-1 W-capable core. Possible though that might be (at standby), remember that Ontario will incorporate a pair of these cores. Additionally, Bobcat is part of a SoC. So, it might be a little more realistic to expect power numbers between 10 and 20 W.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: More On Bobcat

Prev Page More On Bulldozer Next Page Keeping AMD’s 2011 Code-Names Straight-

tacoslave dogman_1234No new news here, but I cannot wait until AMD releases "Bulldozer"! The thing that got me was the use of the cores. Really, all AMD needs now is a Commercial. Anybody?Reply

Put it in a mac, the sheeple will eat this Sh1t up.

-

buzznut Thanks for the great article and valuable information. Someone scolded me for saying I wanted to wait for a bulldozer processor to upgrade. Thanks for clearing this up. Yes, Bulldozer is what I'm waiting for, prolly a Zamboni would be nice.Reply

By the way, just who the hell comes up with these ridiculous names? I personally think manufacturers would sell more units if they weren't so confusing. -

Judguh dogman_1234No new news here, but I cannot wait until AMD releases "Bulldozer"! The thing that got me was the use of the cores. Really, all AMD needs now is a Commercial. Anybody?I'd have to say I partially agree with you. I see way more Intel commercials (many) than AMD (none). My next build: Bulldozer :DReply -

SpadeM ReplyDetails being discussed today include a dual-issue x86 decoder and out-of-order execution, perhaps enabling a performance advantage compared to Intel’s Atom CPUs.

Not quite, the out of order execution WILL enable a performance advantage compared to Atom, + the added bonus that the AMD GPU on the Ontario platform (if similar or better in performance to the ION) WILL again make for a better platform as a hole.

On the Bulldozer side, Power Gating and Turbo for modules, TST > SMT should be something to look forward.

PS: On the commercials side I'm looking forward to something like this:

http://www.youtube.com/watch?v=MK0hU0OYvCI -

luke904 ok everyone... I swear to god if AMD pulls this one off and bitch slaps Intel again... PARTY AT MY HOUSE!!!Reply -

joytech22 Excellent!! i skipped the Istanbul CPU's because i'm waiting to score on a "Scorpius" platform! and i know 100% that i will be able to afford it on release!Reply -

thomaseron Hopefully, Bulldozer will easily outperform my 955BE. So when the time comes, Bulldozer, Northern islands and about 8GB RAM on a new motherboard. :-) I hope Bulldozer kicks the living daylight out of intel for like one or two generations, so we can get som balance on the market.Reply -

thomaseron SpadeMNot quite, the out of order execution WILL enable a performance advantage compared to Atom, + the added bonus that the AMD GPU on the Ontario platform (if similar or better in performance to the ION) WILL again make for a better platform as a hole. On the Bulldozer side, Power Gating and Turbo for modules, TST > SMT should be something to look forward.PS: On the commercials side I'm looking forward to something like this: http://www.youtube.com/watch?v=MK0hU0OYvCIReply

I totaly agree on the commersial bit. :)