Game Over? Core 2 Duo Knocks Out Athlon 64

Split Busses

Although all busses are 128 bit wide, this size is not always necessary. As busses are designed for worst-case scenarios, Intel decided to add a feature that allows the processor to split busses, so it can shutdown unused parts of it. An 8-byte word only requires a 64 bit data path, so the second half of an affected bus can remain inactive and thus conserve power.

Platform Related Power Features: PSI-2, DTS, PECI

An energy-efficient processor yet is not enough. An energy saving mechanism will only be efficient in a suitable environment. Intel integrated three more energy management features that are related to the platform:

- PSI-2 (Power Status Indicator)

- DTS (Digital Thermal Sensors)

- PECI (Platform Environment Control Interface)

All three originate in the mobility (PSI) or server space, and all of them have undergone major improvements before they were implemented into the Core 2 micro-architecture.

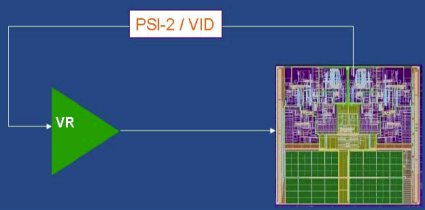

PSI-2 Communicates CPU Power Requirements

Each Core 2 processor has a circuit that keeps track of power requirements. If your motherboard features the PSI-2 controller counterpart on the motherboard it can receive this signal and adjust the load to available voltage regulators and their most efficient use can be selected. When the processor power requirements drop, the PSI-2 controller will take notice and shutdown one or more voltage regulators, so the VRM can always operate at maximum efficiency.

As far as we know, the PSI-2 feature is limited to mobile processors (Merom), but might be enabled for platform solutions at some point.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: Split Busses

Prev Page Intel SpeedStep Technology Next Page Digital Thermal Sensors (DTS)

Patrick Schmid was the editor-in-chief for Tom's Hardware from 2005 to 2006. He wrote numerous articles on a wide range of hardware topics, including storage, CPUs, and system builds.