PCI Express 3.0: On Motherboards By This Time Next Year?

After an unfortunate series of untimely delays, the folks behind PCI Express 3.0 believe they've worked out the kinks that have kept next-generation connectivity from achieving backwards compatibility with PCIe 2.0. We take a look at the tech to come.

Moderately-Priced Chipsets

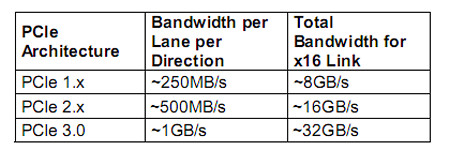

Any gamer with an Intel P55 chipset can tell you about the advantages and disadvantages of P55 versus Intel's X58 chipset. Advantage: motherboards employing using the P55 chipset are more reasonably-priced than those using X58, on average. Disadvantage: P55 comes equipped with minimal PCI Express connectivity, instead relying on Intel Clarkdale- and Lynnfield-based CPUs with 16 lanes of second-gen PCIe built into the processor itself. Meanwhile, X58 leverages 36 lanes of PCI Express 2.0.

For P55 customers who want to use two graphics cards, both boards are forced down to x8 signaling rates. If you want to add a third card to a P55-based platform, it'll have to occupy the chipset's connectivity, which unfortunately runs at first-gen signaling rates and is limited to a maximum of four lanes on a board with the corresponding slot.

When I asked Al Yanes of the PCI-SIG group how many lanes we could expect to see in PCI Express 3.0-enabled chipsets from AMD and Intel, he responded that this was “proprietary information” that he “could not discuss.” I didn’t really expect an answer. But still, given the opportunity, the question had to be asked. We feel it’s unlikely that AMD and Intel, both members of the PCI-SIG Board of Directors, would invest time and money into PCI Express 3.0 development if they planned on using PCI Express as an excuse to reduce lane counts. Thus, we feel it’s far more likely that future AMD and Intel chipsets will continue to employ segmenting similar to what we see today, with high-end platforms sporting enough connectivity to support a pair of graphics cards at native x16 signaling, and more mainstream chipsets shaving off PCIe from there.

Picture a chipset like the P55, but with 16 available PCI Express 3.0 lanes. Since these 16 lanes run at twice the speed of PCI Express 2.0, you'd actually be getting the equivalent of 32 lanes. Then, it'd just be a matter of a company like Intel making its chipset compatible with three- and four-way GPU configurations. Unfortunately, we already know that Intel's next-generation P67 and X68 chipsets will still be limited to PCIe 2.0 (and the Sandy Bridge CPUs will similarly be limited to 16 lanes of on-die connectivity).

In addition to CUDA/Fusion/parallel processing, the expansion of mainstream capabilities through higher-bandwidth interconnects like PCI Express 3.0 is where we see the technology's true potential emerging. Without question, PCI Express 3.0 will enable moderately-priced motherboards with interfaces that were limited to high-end platforms in the previous generation. Those high-end platforms, armed with PCI Express 3.0, will naturally set new performance records, thanks to innovations in graphics, storage, and networking that exploit the available throughput.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

-

cmcghee358 Good article with some nice teases. Seems us regular users of high end machines won't see a worth until 2012. Just in time for my next build!Reply -

tony singh What the..... pcie3 already devoloped & most games graphics are still of geforce 7 level thnk u consoles..Reply -

iqvl Good news to peoples like me who haven't spent any money on PCIE 2.0 DX11 card due to nVidia's delay in shipping GTX460.Reply

Can't wait to see PCIE 3.0, native USB3/SATA3, DDR4, quad channel and faster&cheaper SSD next year.

In addition, I hate unreasonably priced buggy HDMI and would also like to see the Ethernet cable(cheap, fast and exceptional) based monitors as soon as possible.

http://www.tomshardware.com/news/ethernet-cable-hdmi-displayport-hdbaset,10784.html

One more tech that I can't wait to see: http://www.tomshardware.com/news/silicon-photonics-laser-light-beams,10961.html

WOW, so much new techs to be expected next year! -

ytoledano Processor speed *is* increasing exponentially! Even a 5% year-on-year increase is exponential.Reply -

Casper42 I havent read this entire article but on a related note I was told that within the Sandy Bridge family, at least on the server side, the higher end products will get PCIe 3.0.Reply

And if you think the Core i3/5/7 desktop naming is confusing now, wait till Intel starts releasing all their Sandy Bridge Server chips. Its going to be even worse I think.

And while we're talking about futures, 32GB DIMMs will be out for the server market most likely before the end of this year. If 3D Stacking and Load Reducing DIMMs remain on track, we could see 128GB on a single DIMM around 2013, which is when DDR4 is slated to come out as well. -

JonnyDough ReplyAfter an unfortunate series of untimely delays, the folks behind PCI Express 3.0 believe they've worked out the kinks that have kept next-generation connectivity from achieving backwards compatibility with PCIe 2.0. We take a look at the tech to come.

It's nice to see the backwards compatibility and cost be key factors in the decision making. Especially considering that devices won't be able to saturate it for many years to come. -

rohitbaran ReplyNothing in the world of graphics is getting smaller. Displays are getting larger, high definition is replacing standard definition, the textures used in games are becoming even more detailed and intricate.

Even the graphics cards are getting bigger! :lol: -

iqvl rohitbaranEven the graphics cards are getting bigger!I believe that he meant gfx size per performance. :)Reply -

Tamz_msc ReplyWe do not feel that the need exists today for the latest and greatest graphics cards to sport 16-lane PCI Express 3.0 interfaces.

Glad you said today, since when Crysis 3 comes along its all back to the drawing board, again.