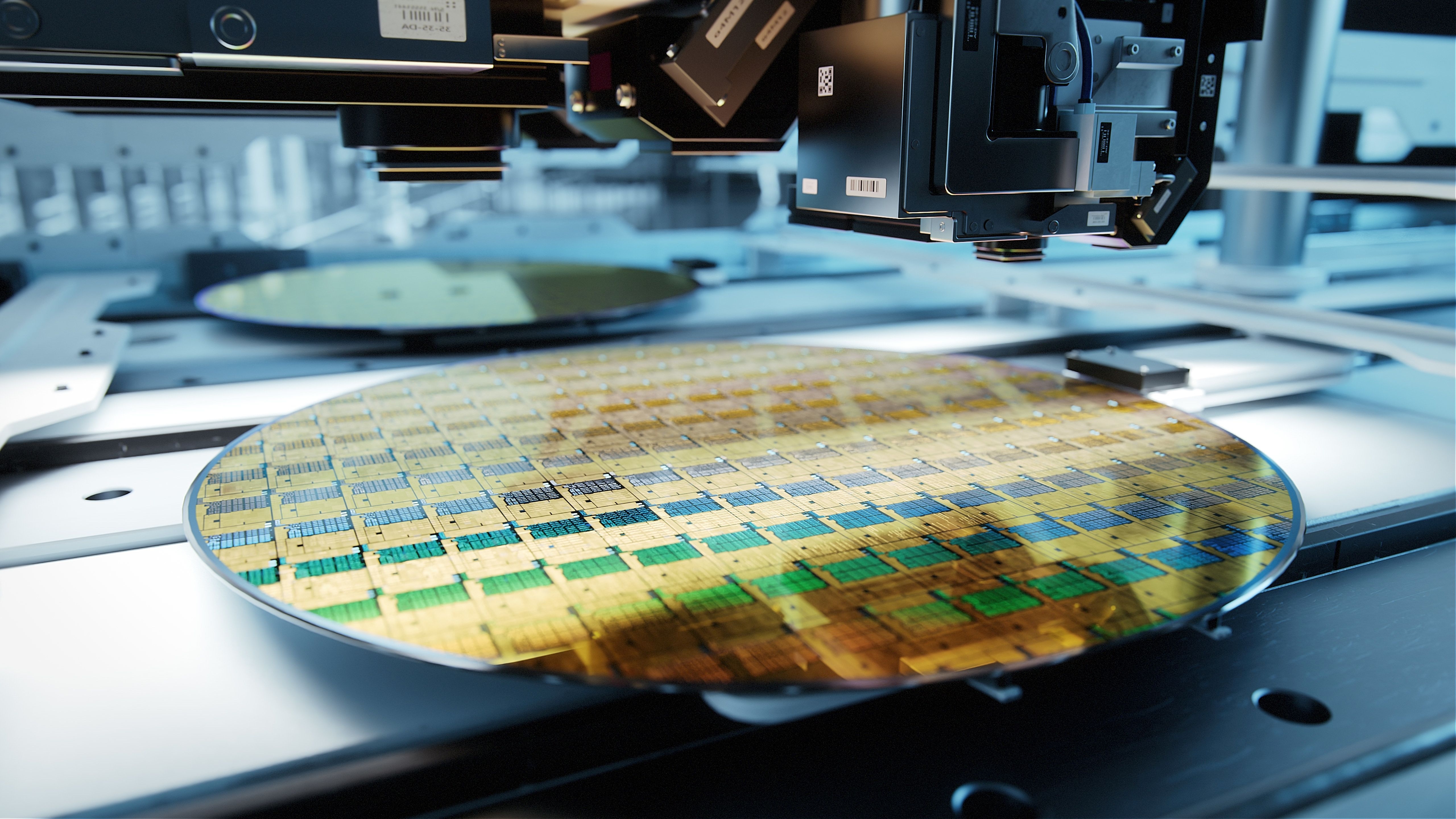

Firm predicts it will cost $28 billion to build a 2nm fab and $30,000 per wafer, a 50 percent increase in chipmaking costs as complexity rises

Chips are not getting cheaper.

Increasingly sophisticated wafer fab tools are needed to produce chips on leading-edge process technologies, thus intensifying costs with each new node. Analysts from International Business Strategies believe that the situation will worsen at 2nm, with chip costs growing by around 50% compared to 3nm processors, reports Nikkei, ultimately resulting in a $30,000 price tag for each wafer of 2nm chips.

IBS estimates that a 2nm-capable fab with a capacity of roughly 50,000 wafer starts per month (WSPM) costs around $28 billion, up from around $20 billion for a 3nm fab with a similar production capacity. The cost increase will be driven by the increased number of EUV litho tools required to maintain a 50,000 WSPM capacity for a 2nm-class technology. This will significantly increase production costs per wafer and per chip, which will inevitably affect companies that use leading-edge fabrication technologies, such as Apple, which is currently the only company that mass produces processors for smartphones and PCs using TSMC's latest N3B (3nm-class fabrication process).

Fascinating article about miniaturization of chips, and how the demise of Moore's law may impact global geopolitics. "gap is narrower than it ever has been between Intel and SMIC, China’s top chipmaker" https://t.co/j8AeDzFzA2 pic.twitter.com/u7mBXS1ComDecember 14, 2023

Expand the tweet above to see the relevant predictions. IBS further estimates that it will cost Apple around $30,000 to process a single 300mm wafer using TSMC's N2 fabrication process when it is introduced in the 2025 – 2026 timeframe, which is up from around $20,000 for an N3-based wafer, as estimated by IBS and some other analysts. Such a tangible cost-per-wafer increase will inevitably increase the per-chip cost by a similar margin.

However, IBS seems to be a little dramatic with its per-chip cost estimate. The company believes that Apple's current 3nm per-chip cost is around $50, but it does not define the chip's die size. Arete Research estimates that Apple's latest A17 Pro system-on-chip for smartphones has a die size between 100mm^2 and 110mm^2, which is in line with die sizes of the company's previous-generation A15 (107.7mm^2) and A16 (around 5% larger than A15, so, approximately 113mm^2) SoCs. If Apple's A17 Pro has a die size of 105mm^2, then one 300-mm wafer can fit 586 of these, which brings their cost to approximately $34 at an unrealistic 100% yield and $40 at a more realistic 85% yield.

International Business Strategies further estimates that a 2nm 'Apple chip' will cost around $85, up from $50, which implies rather low yields. At $30,000 per wafer and 85% yield, a single 105mm^2 chip would cost $60, but this is a very rough estimate.

In contrast, a projection from earlier this year indicated a cost of $25,000 per 2nm wafer at TSMC's fabs, reminding us that estimates can vary significantly.

Even with very rough estimates about 2nm fab costs and wafer costs, it is clear that chips made using a 2nm node will be more expensive than processors produced on a 3nm-class process technology. That said, expect companies like AMD and Intel to accelerate the adoption of multi-chipset designs comprised of chiplets made on different nodes in the coming years, thus defraying the costs associated with leading-edge nodes. Meanwhile, it is likely that smartphone processors will retain monolithic designs for a while as advanced packaging costs are still quite high.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

coolitic I wonder if we're going to start having lines of products using cheaper nodes, but still giving them generational improvements to architecture. AMD is kind of doing that already with their I/O chiplets.Reply -

usertests 256 dies at 15x15 (225mm^2) which would be a budget GPU (Navi 23 = 237, Navi 33 = 204mm^2) or larger APU (Renoir = 156, Cezanne = 180, Rembrandt = 208, Phoenix = 178mm^2). $138 at 85% yield.Reply

Massive increases in wafer cost aren't good, but they aren't a death knell for consumer electronics. It might add $50 to the BOM of smaller stuff. The perf/efficiency benefits are going to outweigh the $50.

I wonder what die sizes we'll see for Strix Point (AMD's first mainstream 12-core APU) and Strix Halo (chiplets?).

A simple solution might be to get all L3 cache (SRAM) off of the latest node, and make 3D stacking of L3 cache made on a cheaper node the standard. Not just for premium products. If it would be too large to fit in 1 layer, increase the layer count.coolitic said:I wonder if we're going to start having lines of products using cheaper nodes, but still giving them generational improvements to architecture. AMD is kind of doing that already with their I/O chiplets.

Come on Samsung, start making stacked SRAM already:

https://news.samsung.com/global/samsung-announces-availability-of-its-silicon-proven-3d-ic-technology-for-high-performance-applications -

DavidMV I think you are going to see older nodes (7, 10, 14, 28 nm) stick around a lot longer than expected. Not everything needs to be the latest nodes, those new nodes will be reserved for very high performance battery powered devices. Maybe that is why there are so many new fab buildings being built, the old lines aren't going away like they normally would.Reply -

George³ The problem seemed completely honestly considered and calculated. Even mathematically it looks good. How do I trust any calculations when I don't have company information on wholesale pricing? Anyone can set false metrics to begin with and then make calculations with them that are mathematically infallible.Reply -

usertests Reply

There has been plenty of news on wafer costs, and a clear trend:George³ said:The problem seemed completely honestly considered and calculated. Even mathematically it looks good. How do I trust any calculations when I don't have company information on wholesale pricing? Anyone can set false metrics to begin with and then make calculations with them that are mathematically infallible.

https://www.siliconexpert.com/blog/tsmc-3nm-wafer/

You just need to use one of the online wafer calculators to figure out how many dies of a certain size are possible on an industry standard 300mm diameter wafer, divide the numbers, divide by 0.85 to represent increased cost from bad yields, etc.

https://www.silicon-edge.co.uk/j/index.php/resources/die-per-wafer -

George³ Yes, a lot of news, and each of them carries company pricing secrets that are otherwise kept in a safe away from the eyes of customers and competitors.Reply

I can't argue with the trend. Maybe I should not trust the slope of the graphs. Too steep it seems -

sjkpublic 50 percent increase in cost, 50 percent increase in speed and decrease in electric going from 3 to 2nm. Generally speaking.Reply -

Sippincider ReplyDavidMV said:I think you are going to see older nodes (7, 10, 14, 28 nm) stick around a lot longer than expected. Not everything needs to be the latest nodes

Indeed. Consider mundane-but-crucial applications such as automotive powertrain and PLCs (programmable logic controllers). The ones that had trouble getting chips during Covid.

Chips for these need to be available and reliable under tough conditions, more than they need to feature cutting-edge nodes. -

Co BIY If the $50 dollar chip in the $1400 iPhone doubles to $100 in the $1800 future iPhone I doubt it'll make a big difference.Reply

There is a point to be made about reducing returns on improvements that will eventually occur even if Moore's "law" continues without interruption. The types of applications that can make reasonable use of the increased performance at the bleeding edge will become a smaller and smaller. -

Co BIY ReplyDavidMV said:I think you are going to see older nodes (7, 10, 14, 28 nm) stick around a lot longer than expected. Not everything needs to be the latest nodes, those new nodes will be reserved for very high performance battery powered devices. Maybe that is why there are so many new fab buildings being built, the old lines aren't going away like they normally would.

The older nodes aren't just sticking around - TSMC is building new Fabs for "Mature" nodes.

https://www.anandtech.com/show/17456/tsmc-to-expand-capacity-for-mature-and-specialty-nodes-by-50