DRAM Alternative Developed: 4X Higher Density at Higher Speed and Lower Power

Unisantis' DFM combines qualities of DRAM and NAND.

Unisantis Electronics, a startup led by Fujio Masuoka, the inventor of NAND memory, has developed Dynamic Flash Memory (DFM), a volatile type of memory that promises four times higher density than dynamic random access memory (DRAM) along with higher performance and lower power consumption.

DRAM memory relies on arrays of charge storage cells consisting of one capacitor and one transistor per data bit. Capacitors charge transistors when '1' is recorded into that cell and discharge when '0' is recorded into that cell. The arrays are arranged in horizontal wordlines and vertical bitlines. Each column of cells consists of two '+' and '−' bitlines that are connected to their own sense amplifiers that are used to read/write data from/to the cells. Both read and write operations are performed on wordlines, and it is impossible to address a single bit.

Throughout the history of DRAM, manufacturers have focused on making memory cells smaller by applying new cell structure and process technologies in a bid to increase DRAM capacity, reduce power consumption, and improve performance.

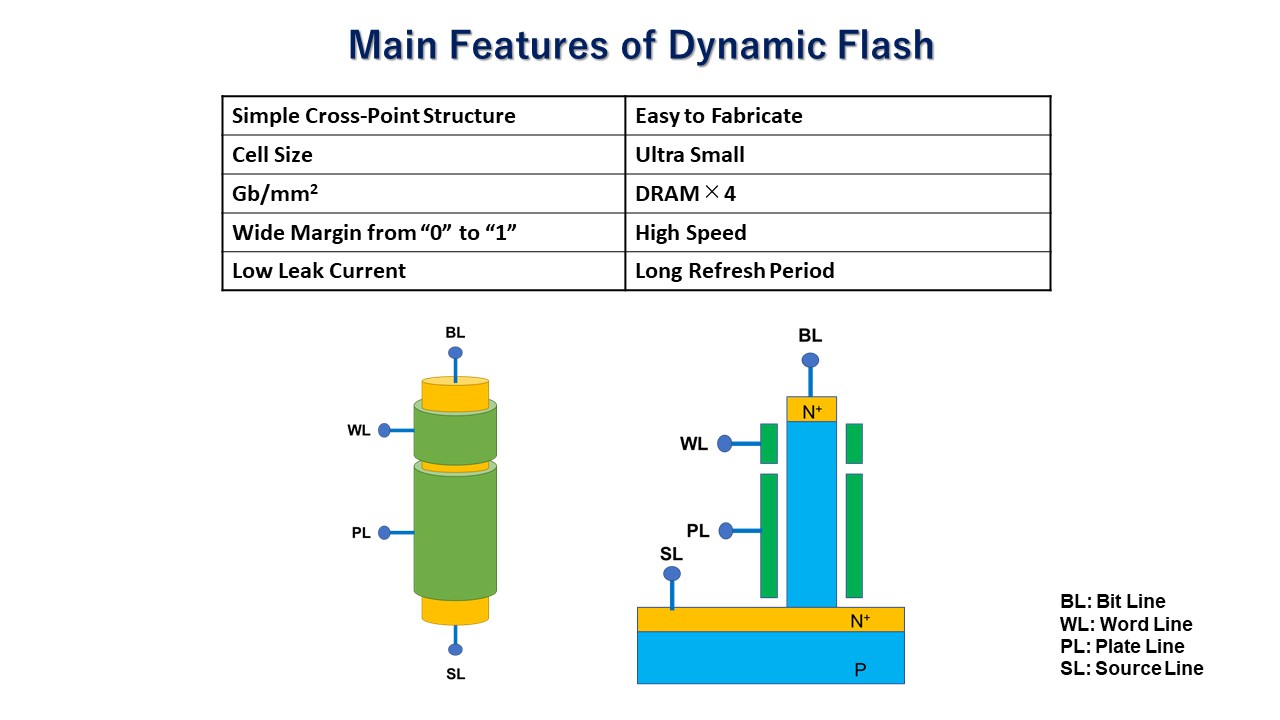

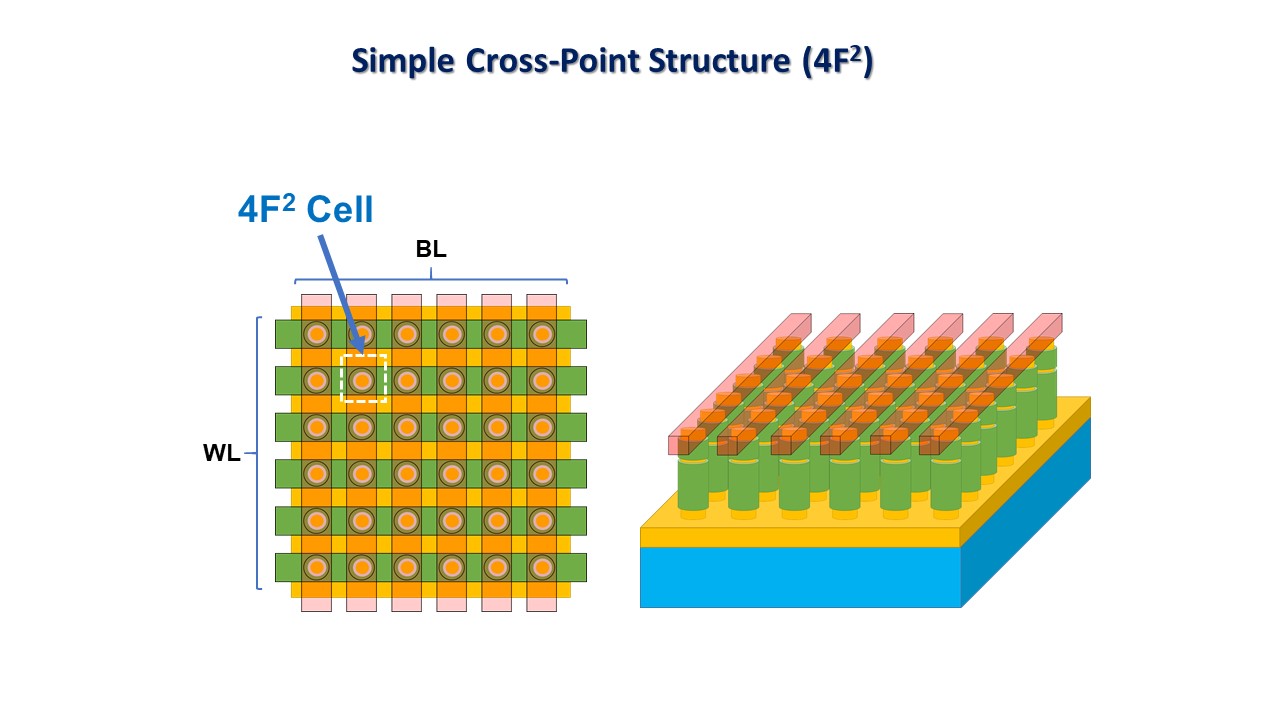

Unisantis' Dynamic Flash Memory uses a Dual Gate Surrounding Gate Transistor (SGT) to eliminate capacitors and uses 4F2 gain cell structures (which are smaller than 6F2 used by DRAM today), something that significantly increases bit density (by up to four times) of memory compared to DRAMs. DFM is not the industry's first capacitor-less type of random access memory (RAM), but previous attempts were unsuccessful.

According to Unisantis, unlike ZRAM (where the margins between 1 and 0 have been too narrow), its DFM has significantly increased '1' and '0' margin results, increasing speeds and improving the reliability of the memory cell. DFM uses the PL (Plate Line) gate to 'stabilize' the FB (Floating Body) by separating '1' write and '0' erase modes, Unisantis says.

Unisantis is an IP licensing company that does not produce memory or commercialize its technologies. The company's DFM will only come to market if Unisantis manages to persuade the industry (namely SoC and memory makers) to adopt its dynamic flash memory. Since DFM uses conventional CMOS materials and does not require very sophisticated manufacturing methods, it may indeed be commercialized. Meanwhile, the company's Dual Gate Surrounding Gate Transistor (SGT) IP could be licensed by various parties that want to take advantage of GAAFET-type transistors.

The DFM technology was described by its inventors, Drs. Koji Sakui and Nozomu Harada earlier this month at the 13thIEEE International Memory Workshop.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

mikewinddale Of course, this comes just as the industry has adopted DDR5!Reply

Maybe this will become the DDR6, so to speak?

Or I wonder if a DDR5 module could use these DFM chips plus some sort of controller chip, similar to registered DRAM, but appearing to the system as if it were an ordinary unregistered module with regular DDR5 DRAM chips? That would add complexity, but if DFM is so much more dense than DRAM, perhaps it would be worth it? For the price of one controller chip, you use 1/4 the memory chips.

Or perhaps that might at least be worth it for systems that already use registered memory? 2 TB of DFM that use a special registered controller chip might cost a fraction of the price of regular registered DRAM, even if the controller chip is more complex because it has to appear to the system as if it were DDR5 DRAM. -

aldaia "Each column of cells consists of two '+' and '−' bitlines that are connected to their own sense amplifiers that are used to read/write data from/to the cells."Reply

That is incorrect. Static RAM do have two + - bitlines. Dynamic RAM however has a single bitline per column. -

InvalidError One more memory design claiming to be capacitor-less yet uses gate charge to store data. Smaller than conventional DRAM cell capacitors but still very much a capacitor.Reply

DDR5 is just an interface. The internal implementation can be whatever the manufacturer wants as long as it maintains compatibility with DDR5 interface requirements, nothing in the DDR5 spec says that memory cells must be capacitor-based. You could make DDR5 SRAM if you wanted to, just set irrelevant latencies to as low as the DDR5 spec will allow.mikewinddale said:Of course, this comes just as the industry has adopted DDR5! -

1843320948 Umm, it is using a surround gate so electron tunneling will yield the same durability as flash (electron tunneling).Reply