Intel Graphics Just Tweeted an Image of a Massive, Mysterious Chip

Is this a socketed Intel Xe Graphics GPU? Intel showed off this multi-chip Xe HP package.

We're all a little curious about what's in store for us with Intel Xe Graphics, and we've been following the company's @IntelGraphics Twitter channel closely. The latest tweet gave a hint of what might be on the horizon:

Silicon bring-up with many tens of billions of transistors needs surgical teamwork of various engineering functions. With only remote access to labs spread worldwide, this was deemed impossible, until now. #NoTransistorLeftBehind #JoinTheOdyssey pic.twitter.com/z3ub5eOV9tMay 1, 2020

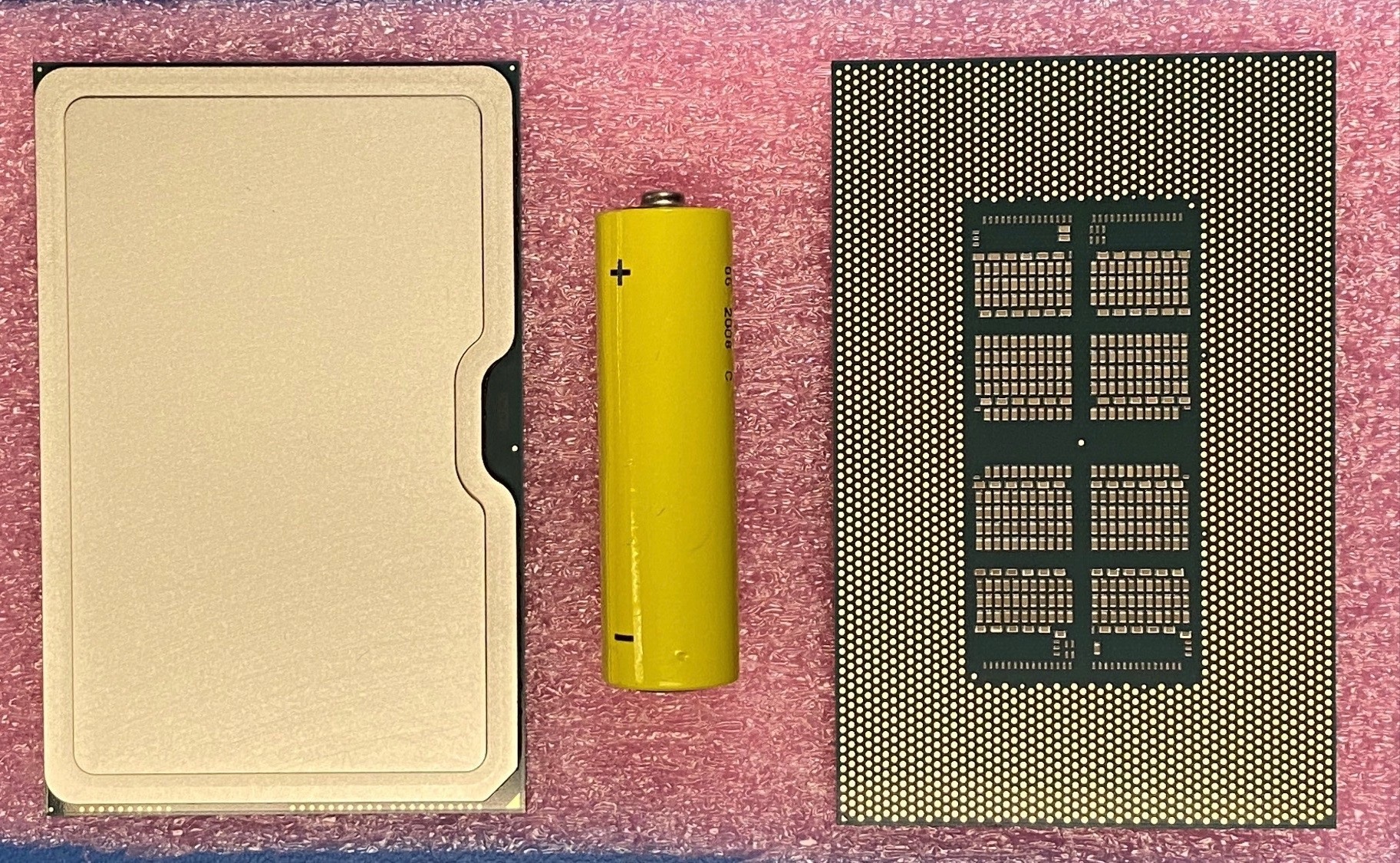

The object of interest is the image of the chip next to the AA battery. The tweet itself doesn't reveal much about the chip, nor does it have any inscriptions on it to guide us. All we have to go by is that this image was tweeted by @IntelGraphics, and that it's a big chip. Also, Raja Koduri has previously shown a wafer with what appears to be massive Xe HP die, which would coincide with this final chip package.

[Update: @IntelGraphics deleted a previous tweet showing Raja and Jim with masks and replaced it with the above tweet focused just on the chip. Updated tweets confirm this is for data center, not consumers.]

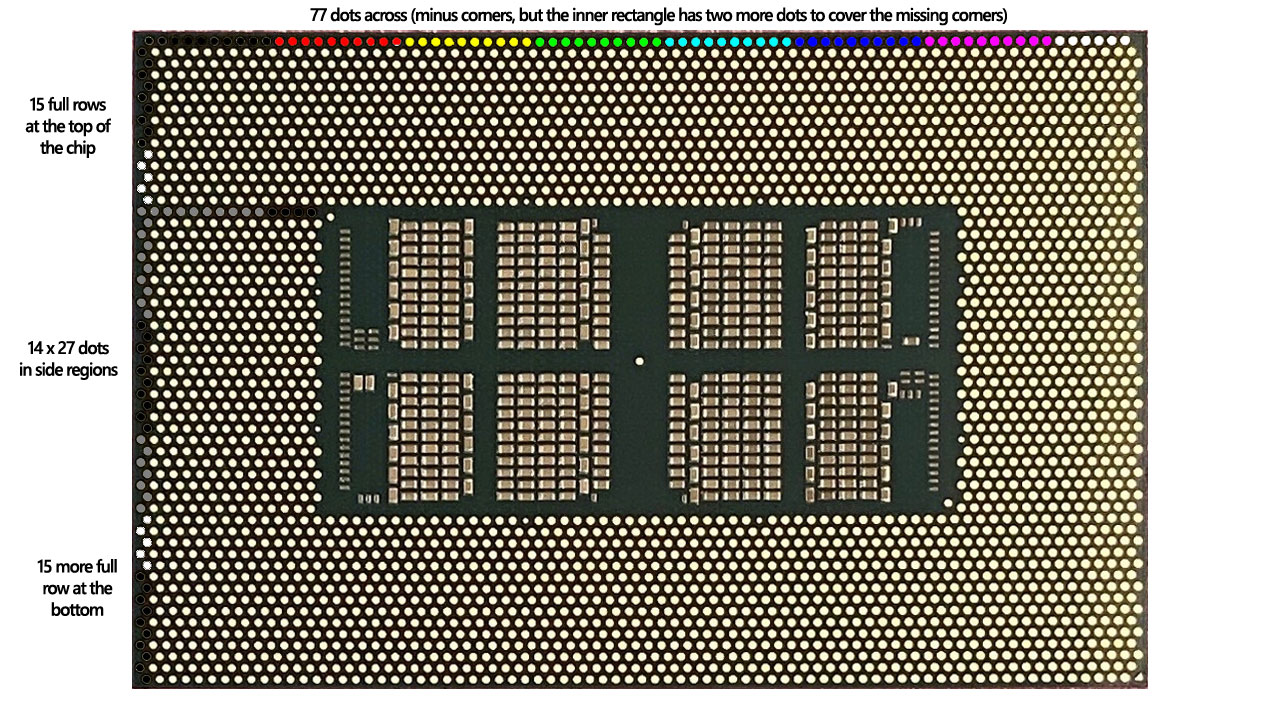

Consequently, the only sensible thing we can tell you is that it's clearly a big chip, and appears to be some kind of GPU packaged like a CPU. There could be an interposer under the IHS, with multiple HBM2 chips. We can't say without additional images, though the center grid does hint that there might be four separate chiplets inside. Also, there appear to be two separate power grids for each of the chiplets, the smaller for HBM2e and the larger for the actual GPU most likely. And of course, the whole package is ready to drop into a socket.

We also have to note that the tweet appears to have been sent out by Raja Koduri, who is the chief architect and VP of Intel's graphics department. Therefore, it is quite safe to assume that it has something to do with Xe Graphics. Beyond that lies the realm of speculation.

Watching the image do the rounds on Twitter, it's clear that nobody has a definitive answer as to what this chip is. As we note in our Xe Graphics article, however, unless Intel is trolling everyone, our best guess is that this is the data center Xe HP Graphics variant. We count 2,688 pads on the LGA package, which is significantly more than sockets LGA2066 and LGA1200, but also fewer than the current Xeon chips use for FCLGA3647.

We can also get a good estimate of the total package size, thanks to the AA battery. The battery measures 49.2-50.5mm long and is 13.5-14.5mm in diameter. Based on that, the package is approximately the same area as six AA batteries, measuring about 80 x 52 mm. Or if you want to be more precise, the package is somewhere between 77.6 x 50 mm and 80 x 52 mm based on the relative sizes of the battery and package (plus or minus another 2mm). Given the size, it's again unlikely this is a consumer oriented product.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

One thing is clear: Intel is taking the "go big or go home" mentality with this chip. Time will tell what it is exactly, what it can do, and whether it can compete with AMD and Nvidia when it comes to the best graphics cards.

Niels Broekhuijsen is a Contributing Writer for Tom's Hardware US. He reviews cases, water cooling and pc builds.

-

Deicidium369 It is NOT Xe HPC - which will debut on Intel 7nm process. Most likely it is a Xe HP for the discrete graphics card they have said will be released shortly.Reply

Xe LP Low Power Integrated Graphics - 1st Gen in Tiger Lake (Gen12)

Xe HP High Power for discrete graphics cards

XE HPC High Perf Compute - for Ponte Vecchio - Will be on Intel 7nm.

You know, you all should read the articles on Tom's Hardware - none of this info is hard to find. - or you are admitting that Intel's EUV 7nm is actually producing Ponte Vecchio silicon way early

Why are you all immediately jumping to the conclusion this is Xe HPC? Why was the Wafer assumed to be Xe HPC and not the most likely Xe HP? Xe HPC will be 7nm and released for the Exascale along with Saphire Rapids Xeons and most likely requires PCIe5. -

crysis2 Reply

Well for an Xe HP this one is really an over killDeicidium369 said:It is NOT Xe HPC - which will debut on Intel 7nm process. Most likely it is a Xe HP for the discrete graphics card they have said will be released shortly.

Xe LP Low Power Integrated Graphics - 1st Gen in Tiger Lake (Gen12)

Xe HP High Power for discrete graphics cards

XE HPC High Perf Compute - for Ponte Vecchio - Will be on Intel 7nm.

You know, you all should read the articles on Tom's Hardware - none of this info is hard to find. - or you are admitting that Intel's EUV 7nm is actually producing Ponte Vecchio silicon way early

Why are you all immediately jumping to the conclusion this is Xe HPC? Why was the Wafer assumed to be Xe HPC and not the most likely Xe HP? Xe HPC will be 7nm and released for the Exascale along with Saphire Rapids Xeons and most likely requires PCIe5.

It is like using NVIDIA fully unlocked top tire GPU die (even bigger than Quadro 8000) just for let say a 2080Ti which is not really logically fuse able.

Hope you understand what i mean cause i am not a native English-speaking person. -

JarredWaltonGPU Reply

Why are you assuming that Xe HPC will only be 7nm? My assumption based on current information is that round one of Xe Graphics will have LP, HP, and HPC -- all on 10nm. Round two will also have LP, HP, and HPC variants -- with the most powerful being Ponte Vicchio. That may be incorrect, but Intel has not publicly stated anywhere I've read that Xe HPC is 7nm Ponte Vicchio only.Deicidium369 said:It is NOT Xe HPC - which will debut on Intel 7nm process. Most likely it is a Xe HP for the discrete graphics card they have said will be released shortly.

Xe LP Low Power Integrated Graphics - 1st Gen in Tiger Lake (Gen12)

Xe HP High Power for discrete graphics cards

XE HPC High Perf Compute - for Ponte Vecchio - Will be on Intel 7nm.

You know, you all should read the articles on Tom's Hardware - none of this info is hard to find. - or you are admitting that Intel's EUV 7nm is actually producing Ponte Vecchio silicon way early

Why are you all immediately jumping to the conclusion this is Xe HPC? Why was the Wafer assumed to be Xe HPC and not the most likely Xe HP? Xe HPC will be 7nm and released for the Exascale along with Saphire Rapids Xeons and most likely requires PCIe5.

One possibility is that potentially Xe HP and Xe HPC are actually going to be the same chip, but HPC will use multiple chips and EMIB while HP will be a single chip. However, that wouldn't make much sense if HP is going into consumer parts, since it would have unnecessary FP64 features. Sure, it could be Intel's equivalent of Titan V I guess, but if so it's going to flop hard in the enthusiast sector.

Basically, the massive package in this shot looks to have four chips under the IHS, and probably four HBM chips as well (could be HBM2 or HBM2e -- we don't know yet). That alone is enough to make the product cost a massive amount of money to produce, which means it won't be for the consumer market. Especially not from Intel.

HEDT chips are a fraction of this size and complexity, and Intel still charges $600+ for such CPUs. Based on the wafer picture, the die looks like it will be massive -- and Raja has hinted as much as well. It's not a great wafer shot, however, so tough to say. The HCC Skylake-X chips (12-18 core) are about 21.2 x 22.1 mm, or 468.5mm2 ($600+), and the XCC chips (up to 28-core) are about 21.7 x 31.7 mm, or 687.9mm2 and go into chips that Intel sells for $2000+.

So, if a single Xe HPC (or Xe HP possibly, depending on what Intel does) chip is larger than the XCC die, it is going to be extremely expensive. Four of them? $15,000-$25,000 each for exascale supercomputers isn't out of the realm of possibility. And if the chips are really Xe HP and measure close to 800mm square, the cheapest graphics cards with the chips are still going to be in the $1000+ range for sure. -

TerryLaze Any possibility for this to be an APU?Reply

Why would it be socketable,just for R&D maybe? -

JarredWaltonGPU Reply

I think it's socketable because Intel wants to have potentially dual-socket add-in boards, maybe even four-socket. Perhaps there's also plans to put it directly on motherboards. For the consumer market, though, I can't think of a good reason to make a socketed GPU like this.TerryLaze said:Any possibility for this to be an APU?

Why would it be socketable,just for R&D maybe?

As far as APU, I mean, it could be done. I'm 99.9% sure that this is just a pure graphics solution, though. Intel needs to prove it can do a compute focused card that will enable an exascale supercomputer. That's what this will be. The socket is sort of like the mezzanine connector approach used on the GV100 supercomputers IMO. -

Deicidium369 Reply

Your English is fine.crysis2 said:Well for an Xe HP this one is really an over kill

It is like using NVIDIA fully unlocked top tire GPU die (even bigger than Quadro 8000) just for let say a 2080Ti which is not really logically fuse able.

Hope you understand what i mean cause i am not a native English-speaking person.

It is well known that there will be a 10nm+ graphics card released by Intel this year for sure.

It is not Xe LP - that is in Tiger Lake

It is not Xe HPC - that is 18 months out - and will be on Intel EUV 7nm along with Sapphire Rapids (EUV 7nm Xeon, PCIe5 and DDR5).

OneAPI works will all the variations of Xe along with Agilex (10nm FPGA PCIe5) and what was thir AI play in Nervana, which is being replaced with Habana.

So the most likely scenario is it's Xe HP - and probably not the low end, low core count variant. This is most likely one of the higher end variants to compete with 2080 at least - so maybe the 8192 core mentioned before or maybe the 16,384.. The number is not known - we know it's big - which lends credence to the possible 16K cores.... but we can't see silicon to be able to determine what it exactly is.

This would be overkill for LP - which is 96 cores in Tiger Lake - for HP it would not be overkill - Intel has no intention of this being another lackluster i740. With Ampere coming out this year, and I am sure AMD will release something underwhelming, so not overkill at all - actually right in the heart of what HP is designed for.

XE HPC is a whole other beast - it is not just a simple variant on LP or HP like HP is. Those 6 GPUs are for all intents and purposes 1 unit - and built on 7nm not 10nm. -

Deicidium369 ReplyJarredWaltonGPU said:I think it's socketable because Intel wants to have potentially dual-socket add-in boards, maybe even four-socket. Perhaps there's also plans to put it directly on motherboards. For the consumer market, though, I can't think of a good reason to make a socketed GPU like this.

As far as APU, I mean, it could be done. I'm 99.9% sure that this is just a pure graphics solution, though. Intel needs to prove it can do a compute focused card that will enable an exascale supercomputer. That's what this will be. The socket is sort of like the mezzanine connector approach used on the GV100 supercomputers IMO.

This is probably an Engineering Sample - so packaging it as it is makes it easy to test changes/ etc. Packaging is irrelevant at this stage. I am not sure I agree with the idea of a dual or quad socket Xe HP - but is most definitely possible. I do not agree with it being placed directly on mother boards - that is the idea of Xe HPC - not sure if it will be sockets or more like the Nvidia V100 SXM3 form factor - same as Habana uses for the Cray Blades for the Exascale computer (I think you referred to this as the mezzanine connector, which is correct - also used on several Inspur systems and the DGX).

Ice Lake and Tiger Lake are already APUs - Gen11 in Ice Lake is already competition for the Vega cores, and with a doubling in perf per core, and increasing the core count by 50% it will more than be a match for the 4000 and positioned well for the eventual 5000 APU.

And I do 100% agree this is a pure GPU play. But whether this is the 2080 variant or the Tesla variant - we don't know if it's a compute only or if it's both. I would imagine that to keep the # of SKUs down - it will have dual use - maybe 64-128GB HBM2e on the compute card and only 16GB on the graphics card.

I think we all agree on the broader points... I for one can't wait to see the specs - I am 100% Nvidia, as soon as 4rd party Ampere cards are released, I will buy - same as I pre ordered Vega VII and had one of the first few 3rd party 5700XTs - but most likely a high end variant of Xe will end up in one of my systems. -

Deicidium369 ReplyJarredWaltonGPU said:Why are you assuming that Xe HPC will only be 7nm? My assumption based on current information is that round one of Xe Graphics will have LP, HP, and HPC -- all on 10nm. Round two will also have LP, HP, and HPC variants -- with the most powerful being Ponte Vicchio. That may be incorrect, but Intel has not publicly stated anywhere I've read that Xe HPC is 7nm Ponte Vicchio only.

One possibility is that potentially Xe HP and Xe HPC are actually going to be the same chip, but HPC will use multiple chips and EMIB while HP will be a single chip. However, that wouldn't make much sense if HP is going into consumer parts, since it would have unnecessary FP64 features. Sure, it could be Intel's equivalent of Titan V I guess, but if so it's going to flop hard in the enthusiast sector.

Basically, the massive package in this shot looks to have four chips under the IHS, and probably four HBM chips as well (could be HBM2 or HBM2e -- we don't know yet). That alone is enough to make the product cost a massive amount of money to produce, which means it won't be for the consumer market. Especially not from Intel.

HEDT chips are a fraction of this size and complexity, and Intel still charges $600+ for such CPUs. Based on the wafer picture, the die looks like it will be massive -- and Raja has hinted as much as well. It's not a great wafer shot, however, so tough to say. The HCC Skylake-X chips (12-18 core) are about 21.2 x 22.1 mm, or 468.5mm2 ($600+), and the XCC chips (up to 28-core) are about 21.7 x 31.7 mm, or 687.9mm2 and go into chips that Intel sells for $2000+.

So, if a single Xe HPC (or Xe HP possibly, depending on what Intel does) chip is larger than the XCC die, it is going to be extremely expensive. Four of them? $15,000-$25,000 each for exascale supercomputers isn't out of the realm of possibility. And if the chips are really Xe HP and measure close to 800mm square, the cheapest graphics cards with the chips are still going to be in the $1000+ range for sure.

Xe HPC is quite a different animal than the Xe LP and Xe HP. This will be released on EUV 7nm specifically for the Cray machine - initially. I would be willing to bet that the engineering is not even done on the Xe HPC. There was the idea of a consumer GPU based on Gen11/Gen12 (then renamed Xe LP and further split into LP integrated and HP discrete) with the high end variant (more of a purpose built GPU) coming later - which became Xe HPC.

I think there is some confusion about HP - we all know LP will almost 100% be an IGP - but HP would fill the roles from Late Turing/Early Ampere is both the Video card and compute card markets - it is modular - more slices can be added for higher end compute cards (Tesla)with 64-128GB HBM2e or HBM3 (RTX8000 is 48/96GB) and the Video card would be less slices and less memory 16GB HBM2e)... That modularity is the key here - same broad product Xe HP - but wildly varying capabilities. I think the high end HP is being conflated with the Xe HPC.

At any rate - going to be interesting.

When Xe HPC comes we will see a radical transformation - PCIe5 will enable CXL and GenZ (intra and inter rack) with pools of memory (normal volatile and non volatile RAM), pools of accelerators (FPGA, GPU, AI) etc. This will be a fundamental shift in computing - and is one of the main reason Intel talks about TAM and not just CPUs. -

bit_user Reply

I also wondered about this.TerryLaze said:Why would it be socketable,just for R&D maybe?

First, is it socketed? I don't exactly know what BGA chips look like that aren't soldered down. It definitely looks similar to a LGA, but I'm not sure it is. I'll bet @InvalidError knows.

Second, if it is socketed, does anyone actually know if it's common for engineering samples to be socketed? -

InvalidError Reply

Simple obvious reason this chip must live in a socket: you cannot BGA a chip that has capacitors under it. If this chip was meant to be soldered on board, Intel would design it with all capacitors on top so manufacturers don't have to route a hole into the PCB.bit_user said:First, is it socketed? I don't exactly know what BGA chips look like that aren't soldered down. It definitely looks similar to a LGA, but I'm not sure it is. I'll bet @InvalidError knows.

Another reason to put it in a socket would be CCIX: use the same socket for CPUs, GPGPUs, FPGAs and whatever other forms of semi/full-custom ASICs clients may want to toss in there so SIs can mix-and-match components for their specific application. For exa-scale computing, I imagine saving a whole routing hop by integrating Infiniband-like functionality into a CCIX node instead of going through PCIe slots would do wonders for latency. (Still got a physical PCIe slot with its electrical limitations, but the card itself would be little more than a dumb media converter between the external IB network and CCIX chip it is attached to.)