Silicon Motion SM2258 Technical Preview With Micron 3D TLC NAND

Why you can trust Tom's Hardware

Benchmarks And Comparisons

Comparison Products

We built a diverse group of low-cost SSD products to compare with the product under review. Most companies started pushing higher capacity products over the last year, so our stable of 256GB SSDs has not seen a significant refresh in some time.

The Mushkin Triactor is the newest retail 256GB-class SSD in our tests, and we are working on a full review of the 240GB and 480GB models for a future release. The other products in this review have all shipped for at least the last year.

The Samsung 850 EVO 250GB is the premium product in this group, even though it is a mainstream SSD that often sells at entry-level prices. The Crucial MX200 256GB and Plextor M6V 256GB both utilize planar MLC flash. The Plextor uses a Silicon Motion SM2246EN controller that was very popular from 2014 to early 2015.

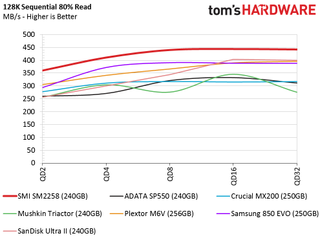

Sequential Read Performance

To read about our storage tests in-depth, please check out How We Test HDDs And SSDs. Four-corner testing is covered on page six of our How We Test guide.

The SMI SM2258 with Micron 384Gbit TLC excels with sequential data reads, and it is just as fast as the Samsung 850 EVO 250GB with Samsung's 64Gbit-per-plane 3D TLC. Sequential reads under these conditions are rarely a problem for SSDs, and even modern low capacity products manage to break the 500 MB/s mark.

Sequential Write Performance

Sequential write performance is another story. Micron's new 3D TLC packs a quad-plane die to increase performance, which exceeds Samsung's dual-plane 3D TLC flash. The direct-to-TLC write technology keeps write performance steady, and we didn't observe any large performance drops throughout the sequential tests. The SM2258 prototype outperformed the Samsung 850 EVO 250GB at all queue depths. It's rare for an entry-level product to dominate the 850 EVO series in any test.

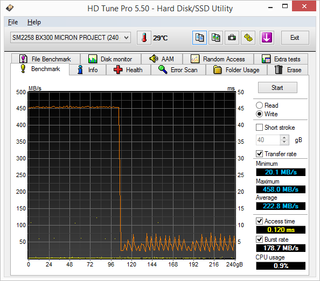

Native TLC Sequential Read Performance

The direct-to-TLC algorithm keeps 128KB block sequential write performance fast through the first 100GB of the SSD during our full-LBA-range write test. After the data fills the SLC buffer and secondary layer, the performance drops to a low rate and fluctuates between 20 MB/s and 75 MB/s.

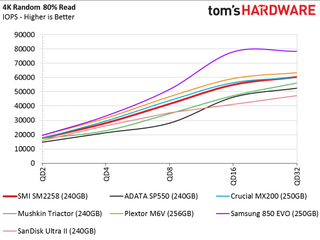

Random Read Performance

The random read performance was much lower than we expected, especially compared to the impressive sequential performance. The queue depth 1 read performance is average for many of the new low-cost SSDs. The SM2258 scales well to queue depth 4, but the large jumps in performance slow down at higher queue depths.

The MX300 and the SMI prototype are the only two products we've tested with Micron's new 3D TLC flash. Neither product managed to breach 10,000 random read IOPS at a queue depth of 1. Without reaching that mark, we couldn't place either product in the modern mainstream SSD category. It is interesting that Silicon Motion's controller is faster at QD1 random reads than the MX300 750GB we tested. It will be very interesting to see what the SM2258 controller can do with more than just six die to address at one time, and it wouldn't be the first time a BX-series product outperformed the current mainstream MX series.

Random Write Performance

The SM2258's random write performance at low queue depths is in line with other products in the chart, including those with MLC flash. The controller does a really good job of keeping performance high. Heavy workloads usually saturate the SLC buffer, but that doesn't happen with the SM2258 due to excellent buffer management.

80 Percent Sequential Mixed Workload

We describe our mixed workload testing in detail here, and describe our steady state tests here.

The high sequential performance for both reads and writes shines through in the light-use mixed workload. The difference between the SM2258 prototype and the 850 EVO in this test surprised us. Could SMI be in a position to overtake the long-standing mainstream performance leader with the help of Micron's 3D TLC?

80 Percent Random Mixed Workload

Apparently, it's still too early to go that far. SMI needs to address the SM2258's low random performance before anyone can make that claim. We see how low performance in the 100-percent read and write tests compounds during mixed workloads during this test. The results will have an impact on the real-world application performance later in the review.

Sequential Steady-State

Earlier, we looked at sequential write steady state performance with HD Tune Pro. SMI appears to trade a large buffer for longer recovery times. Most products armed with the SM2258 controller will fall into the entry-level to mainstream product category, so most users will not use this combination for professional applications with heavy drive writes. This test reveals that it takes quite a bit of time to recover once a user gets a drive into a degraded state.

Random Steady-State

The random steady state test focuses more on performance consistency than the data rate. The SM2258 delivers fairly consistent random performance, but the low performance means it's not a good product for RAID 0 arrays with desktop PCs.

MORE: Best SSDs

MORE: Latest Storage News

MORE: Storage in the Forums

Current page: Benchmarks And Comparisons

Prev Page Specifications And Features Next Page Performance And ConclusionStay on the Cutting Edge

Join the experts who read Tom's Hardware for the inside track on enthusiast PC tech news — and have for over 25 years. We'll send breaking news and in-depth reviews of CPUs, GPUs, AI, maker hardware and more straight to your inbox.

-

Badelhas What does this mean, in reallity? It will outperform the high-end samsung 850 pro drives?Reply -

stairmand It's pretty cool, but I really don't see the point. S-ATA SSDs are a dead end, the future belongs to M.2 and U.2.Reply -

Reply18409763 said:Low endurance 3-bit per cell?!? That is 32 bit right?!

tlc have 3-bit cells. there are 8 levels of states (not sure if these are volts or amps), each level give a binary number between 000 and 111, so can represent 3 independent bits. To have 2 independent bits, you only need to reliably distinguish 4 states, which is obviously easier, but the 66% less memory per density.