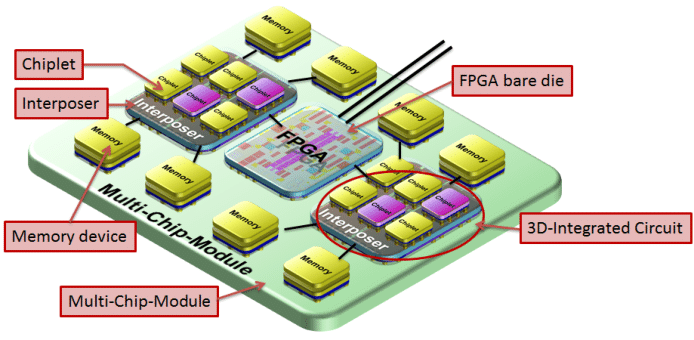

European ExaNoDe Combines Chiplets, FPGAs, HBM, Active Interposers in 3DIC

FPGAs, HBM2 memory, and active interposers with 7nm Arm chiplets, all in a multi-chip module.

The European ExaNoDe project has built a complete prototype of a 3DIC exascale compute node and software stack that heterogeneously integrates many pieces of hardware, including chiplets, HBM, and FPGAs with active interposers.

The project is coordinated by an engineer at CEA-Leti, a French research institute for microelectronics research. CEA has developed the 3D active interposer that enables the integration of chiplets for a 3D integrated circuit (3DIC). Its goals are similar to what Intel has described as its plans with its own Foveros 3D packaging technology: to achieve higher yield by using smaller chiplets, to improve interconnect energy efficiency, and to reduce cost via the modular design.

The concept diagram shows a large multi-chip module (MCM) composed of an FPGA in the middle, surrounded by two of the active interposers and eight dies of HBM2 memory. The interposer itself contains six chiplets, based on 7nm Arm cores.

Project coordinator Denis Dutoit, said, “Affordability and power consumption are the main hurdles for an exascale-class compute node. In the ExaNoDe project, we have built a complete prototype that integrates multiple core technologies: a 3D active interposer with chiplets, Arm cores with FPGA acceleration, a global address space, high-performance and productive programming environment, which will enable European technology to satisfy the requirements of exascale HPC.”

The project also uses the results of some other European projects, such as a scalable UNIMEM memory system that allows for shared memory across multiple of the compute nodes, available through an API. The software stack also uses virtualization. Several 'mini-applications' have already been developed for the node.

Thirteen partners from six countries were involved in the pan-European collaboration, providing expertise in areas such as chiplet design, packaging, UNIMEM and software. It is funded under the European Commission’s Horizon 2020 program, the same program under which HPC processors were delivered earlier this year, as part of another project. More recently, TSMC showed a passive interposer chiplet design for HPC using 7nm Arm cores.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.