TSMC and Arm Show First 7nm Interposer-Based Chiplet System for HPC

TSMC and Arm announced they developed the industry’s first 7nm chiplet system. The proof-of-concept HPC system is based on multiple high-speed Arm cores and a mesh bus, using TSMC's new LIPINCON inter-chiplet interconnect with CoWoS packaging technology.

Chiplet-based designs are one of the current industry trends. This could be connecting various chiplets to a base die, but for high-performance computing (HPC) it often involves partitioning a big die into multiple smaller chiplets, then using advanced packaging technology to achieve performance as close as possible to monolithic integration. The benefit is improved overall yield, and thus cost, due to the smaller silicon dies, although the advanced packaging cost can offset the savings somewhat.

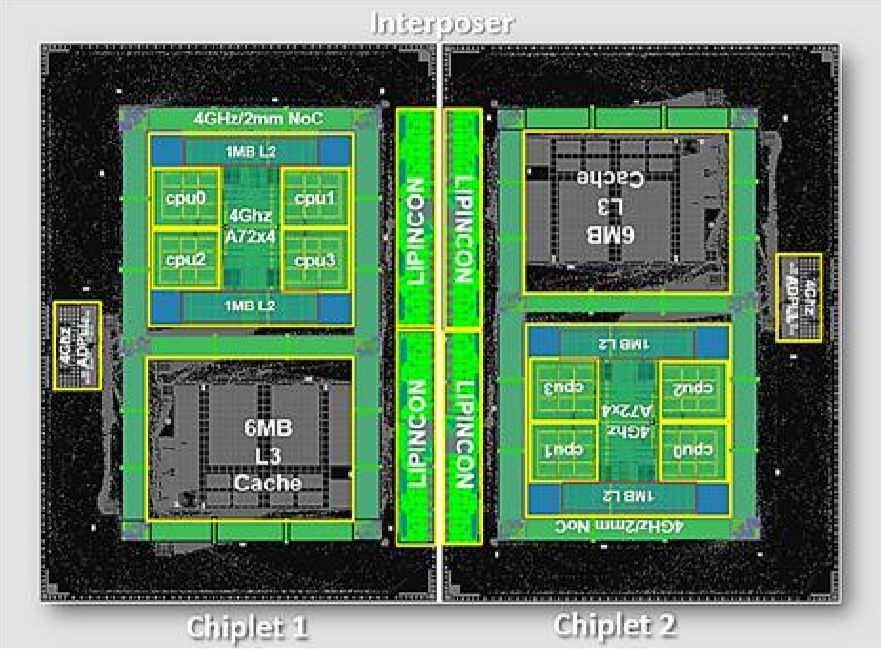

The system that TSMC and Arm presented on Thursday is comprised of two chiplets. Each 7nm FinFET chiplet has four Cortex-A72 cores, connected via a "bi-directional interconnect mesh bus." The chiplet has 2MB of L2 and 6MB of L3 cache. The cores and mesh all operate at 4GHz.

The inter-die interconnect consists of a Chip-on-Wafer-on-Substrate (CoWoS) interposer. More specifically, it uses TSMC’s upcoming LIPINCON interconnect architecture, which stands for Low-voltage-In-Package-INterCONnect. It is TSMC’s alternative to Intel’s AIB and upcoming MDIO chiplet interconnect, which Intel uses with its EMIB packaging technology. In that sense, LIPNCON is to CoWoS what AIB or MDIO is to EMIB.

LIPINCON operates at 0.3V and has a bandwidth of 8Gb/s per pin and 320GB/s total bandwidth. Bandwidth density is claimed at 1.6Tb/s/mm2. It has an energy efficiency of 0.56pJ/bit. For reference, AMD’s non-interposer Infinity Fabric consumes ~2pJ/bit, while Intel has claimed as low as 0.3pJ/bit for EMIB, and 0.5pJ/bit for MDIO.

The significance of this announcement is not so much that TSMC has produced a chiplet or interposer design. Many of those have been produced, such as Xilinx’ four-chiplet FPGAs and a slew of designs that use interposers for HBM integration. Rather, it is TSMC’s proof-of-concept of its LIPINCON interconnect, which might find its way to commercial products next year.

TSMC says the system taped out in December 2018 and was produced in April 2019 (which gives a rough indication of 7nm's cycle time). TSMC provided more details of the design at the 2019 VLSI.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.