Intel Announces Socketed 56-Core Cooper Lake Processors

EDIT 8/6/2019, 12:30am PT: After several rounds of back and forth, Intel has confirmed that "the 56 core Cooper Lake part will have the same socket/pin out mapping between the mainstream platform compatible for Cooper Lake and Ice Lake." We modified the text below to reflect the clarification.

Original article, 8/6/2019, 6:50am PT:

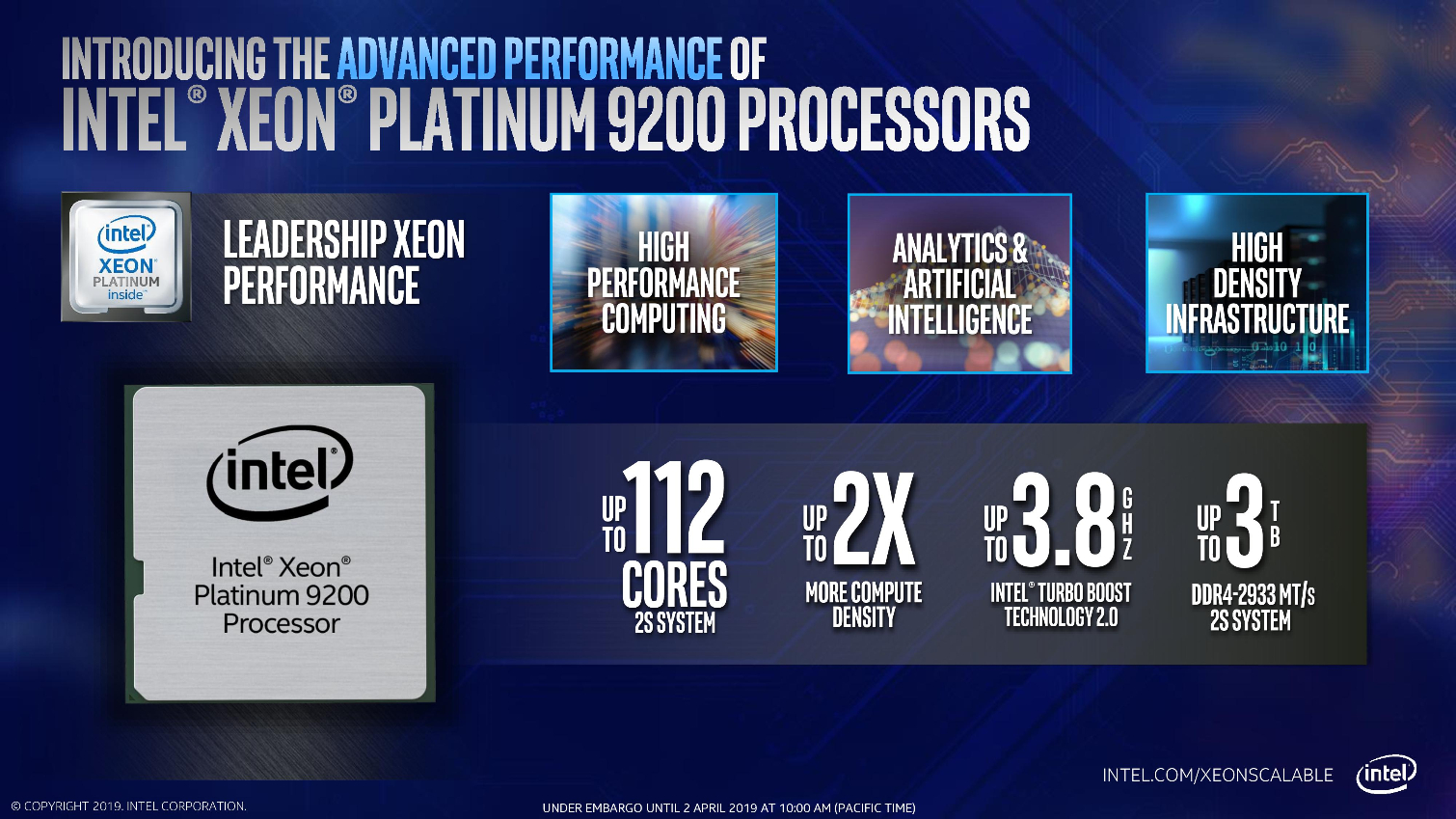

Today Intel announced that it would bring up to 56 cores to its forthcoming Cooper Lake platform, and most importantly, the processors come in a socketed form factor, meaning that unlike the current 9200-series, they will install in more traditional server designs. These processors will also be socket-compatible with the Ice Lake processors.

Article continues belowIntel also announced the processors would support bfloat16 instructions as part of its DL Boost suite of AI enhancements. Intel also claims a lower power envelope than the 9200-series.

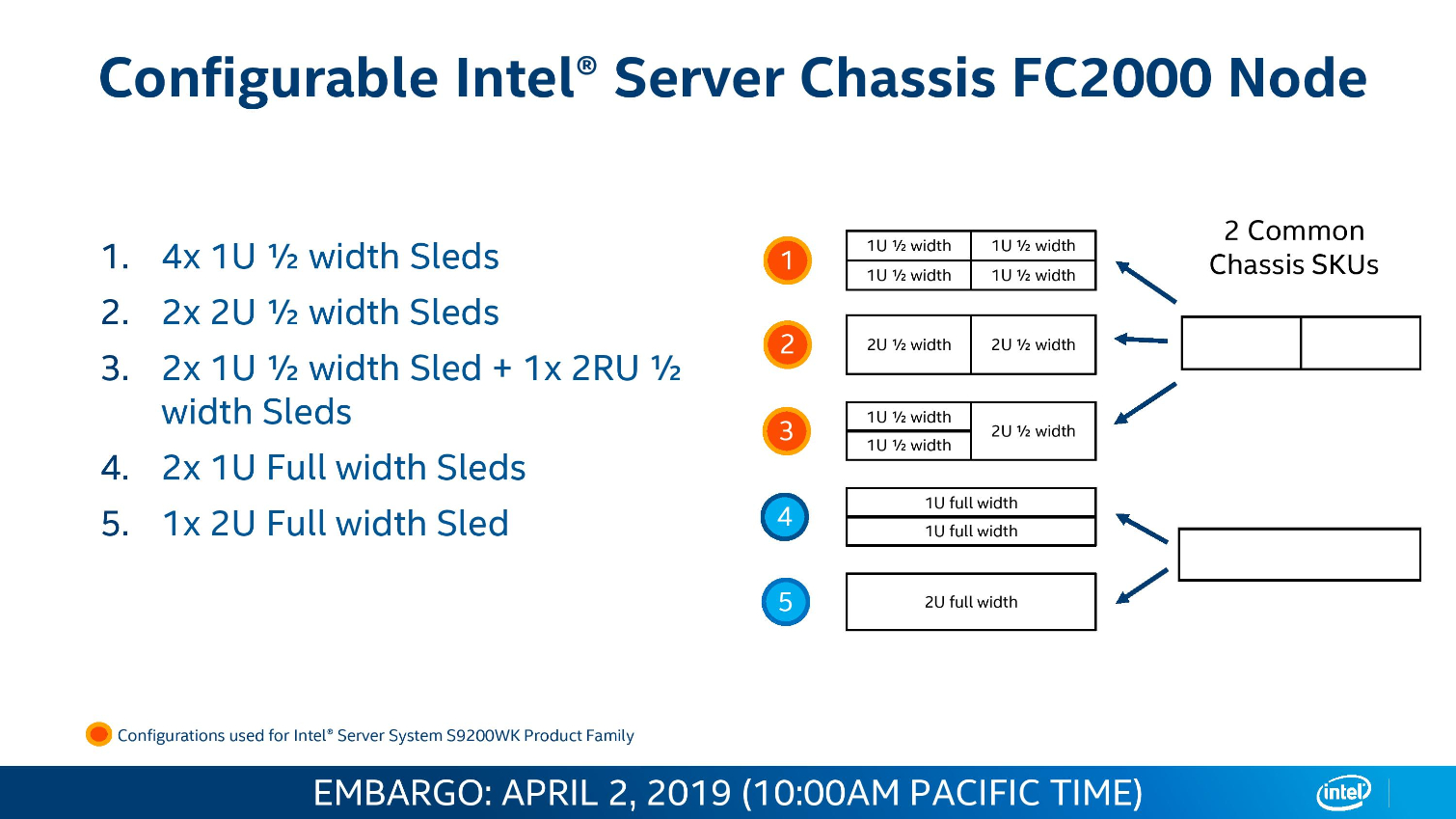

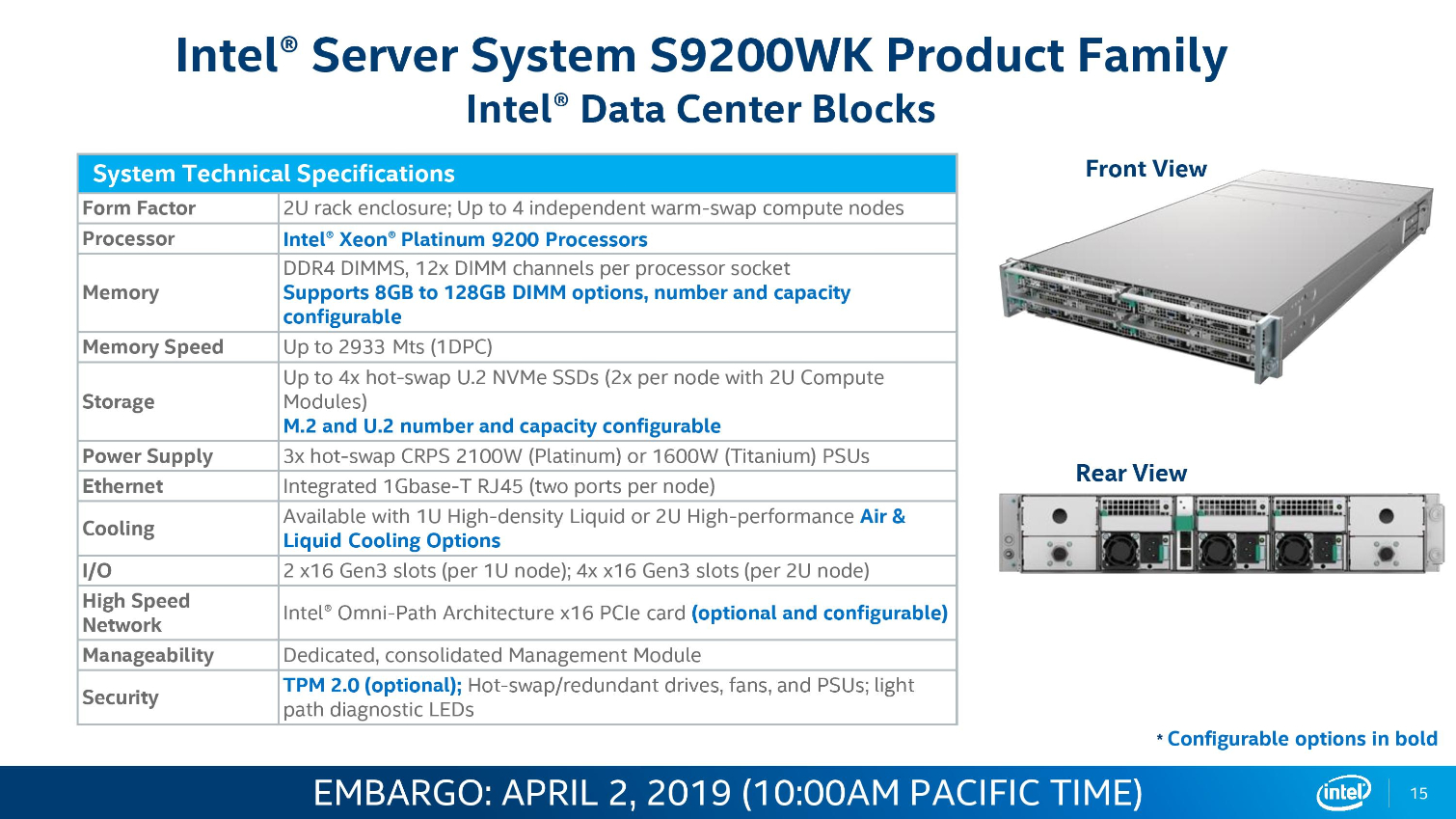

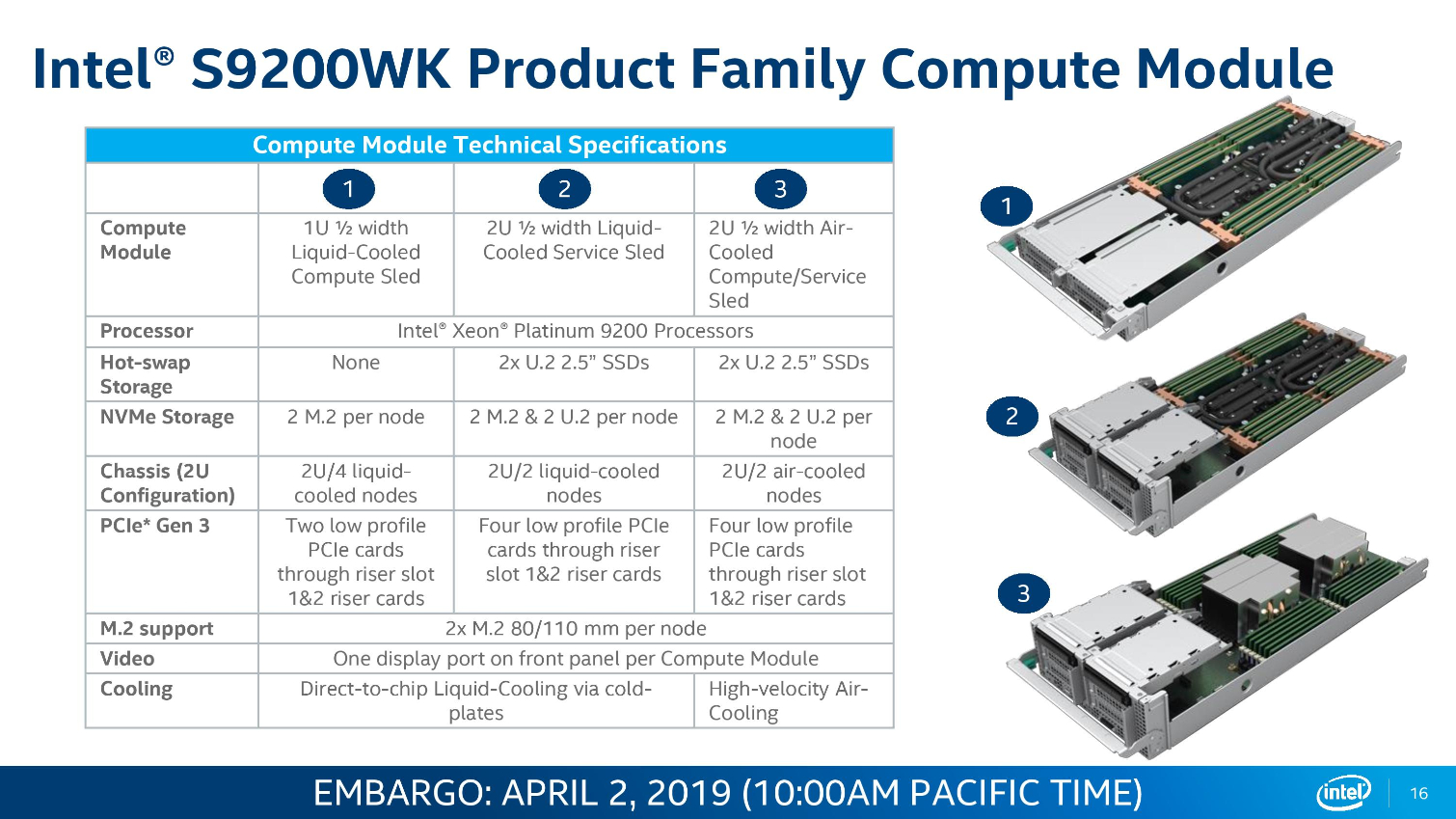

Intel originally turned to a new line of Cascade Lake-AP processors (9200-series) to shore up its defenses in the high core-count space as it braces for the EPYC Rome impact (here's benchmarks of Rome), but these processors only come in pricey custom-built OEM systems and are BGA-mounted, which restricts deployment options.

AMD's formal announcement of its EPYC Rome processors, which will come with up to 64 cores and 128 threads, comes tomorrow. Intel has been busy promoting its partnerships with OEMs, like Lenovo and SAP, as it looks to counter that buzz. Word also trickled out last week that Advania has deployed an HPC cloud service for Intel's existing lineup of 9200-series processors. But aside from the Advania announcement, it appears that uptake of Intel's 9200-series processors has been muted.

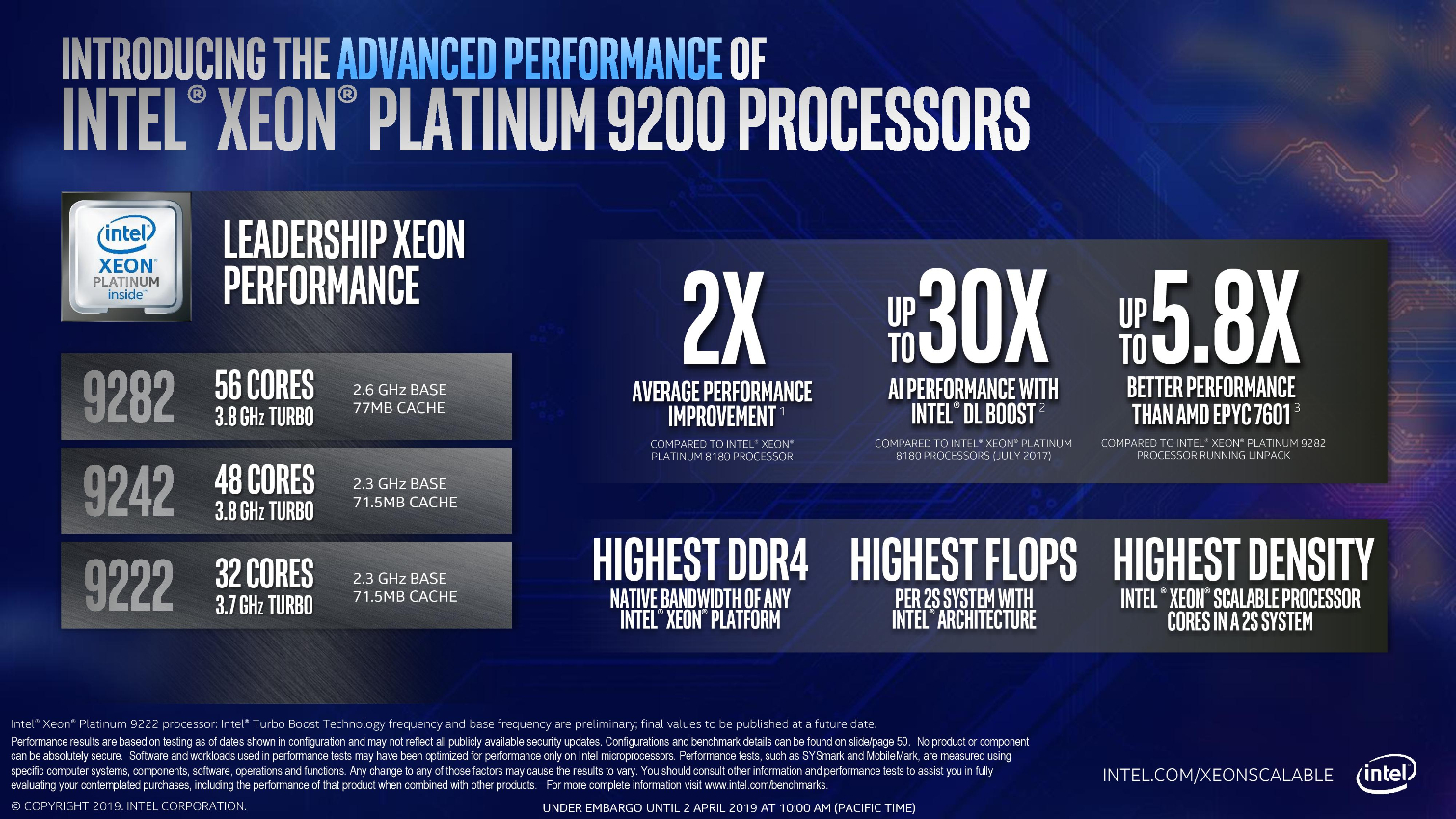

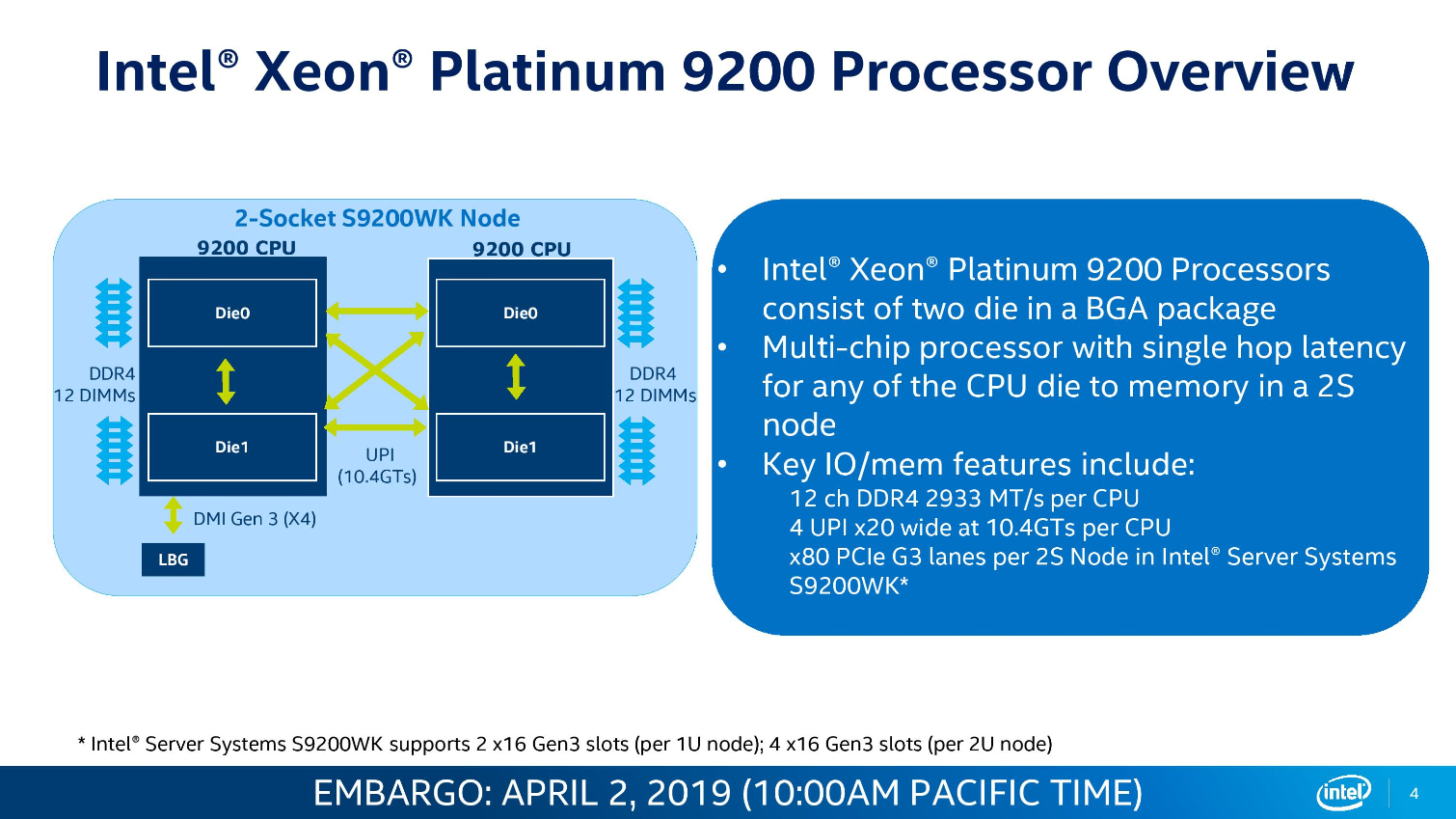

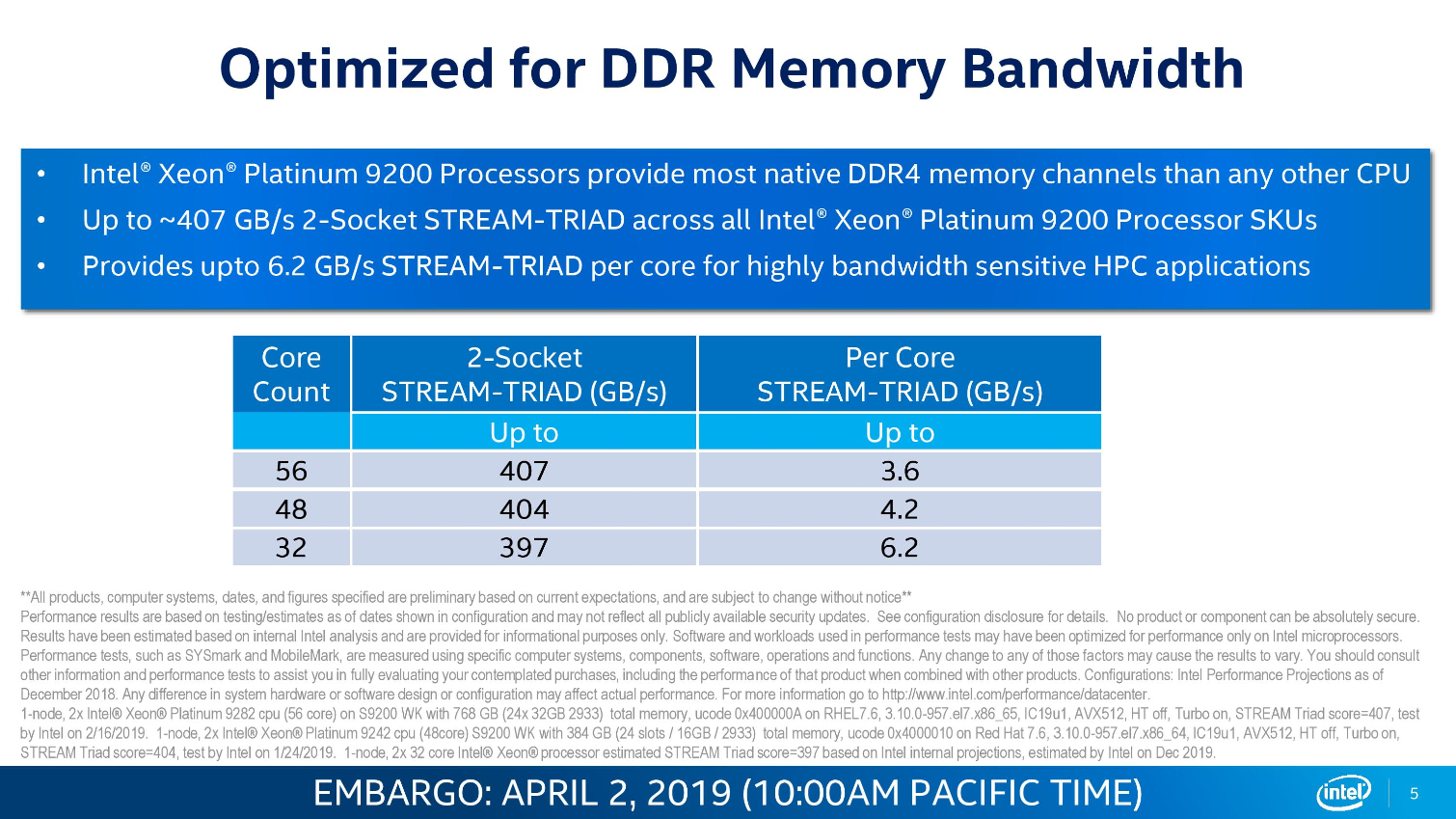

The existing 9000-series chips come packing up to 56 cores and 112 threads in a dual-die MCM (Multi-Chip Module) design, meaning that two die come together to form a single chip. The processors offer the most memory channels (12), and thus access to the highest memory bandwidth, of any data center processor. The current-gen models support 12 channels of DDR4-2933 memory, providing up to 24 memory channels and 3TB of DDR4 memory in a two-socket server. That combo provides up to 407 GB/s of memory throughput for a two-socket server equipped with the 56-core models.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

| Row 0 - Cell 0 | Cores / Threads | Base / Boost Freq. (GHz) | L3 Cache | TDP |

| Xeon Platinum 9282 | 56 / 112 | 2.6 / 3.8 | 77 MB | 400W |

| Xeon Platinum 9242 | 48 / 96 | 2.3 / 3.8 | 71.5 MB | 350W |

| Xeon Platinum 9222 | 32 / 64 | 2.3 / 3.7 | 71.5 MB | 250W |

| Xeon Platinum 9221 | 32 / 64 | 2.1 / 3.7 | 71.5 MB | 250W |

The current 9200-series comes in three flavors with 56-, 48-, and 32-core models, and we can expect similar core counts from the new socketed Cooper Lake models.

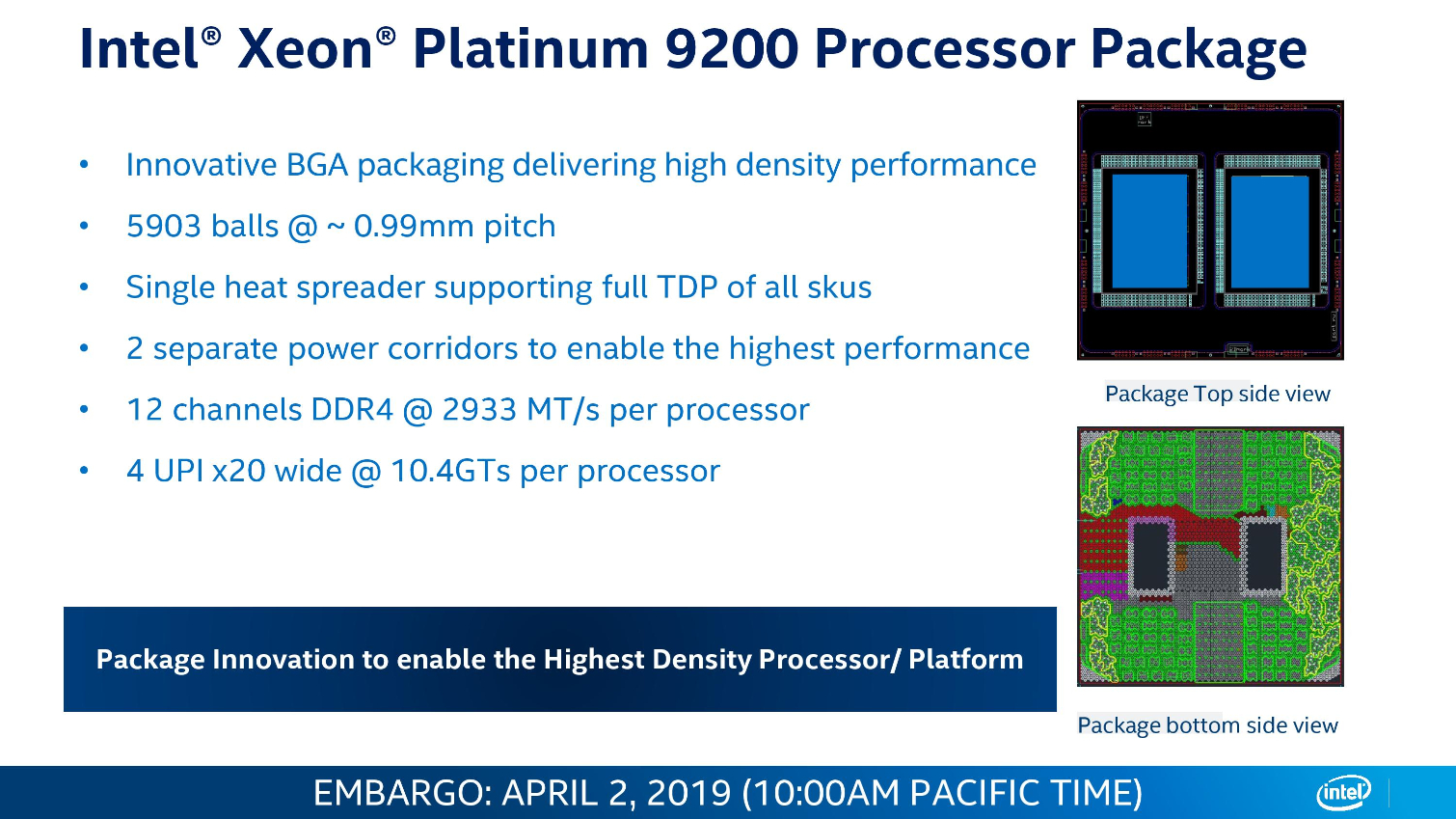

Instead of being socketed processors, the 9200-series processors come in a BGA (Ball Grid Array) package that is soldered directly to the host motherboard via a 5903-ball interface. The 9200-series chips also expose up to 40 PCIe 3.0 lanes per chip, for a total of 80 lanes in a dual socket server.

Intel is holding the details of the architecture close to its chest, but we'll learn more at the official launch. For now, Intel just wants to remind you that it has a game plan to tackle AMD's EPYC Rome, which will certainly make for an interesting year in the data center space. Intel says the new processors will arrive in the first half of 2020.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

Isn't Intel expected to utilize the LGA 4189 socket for Cooper Lake, also offering compatibility with both Cooper Lake and the company's future Ice Lake processors ??Reply

-

jmcgaw Reply

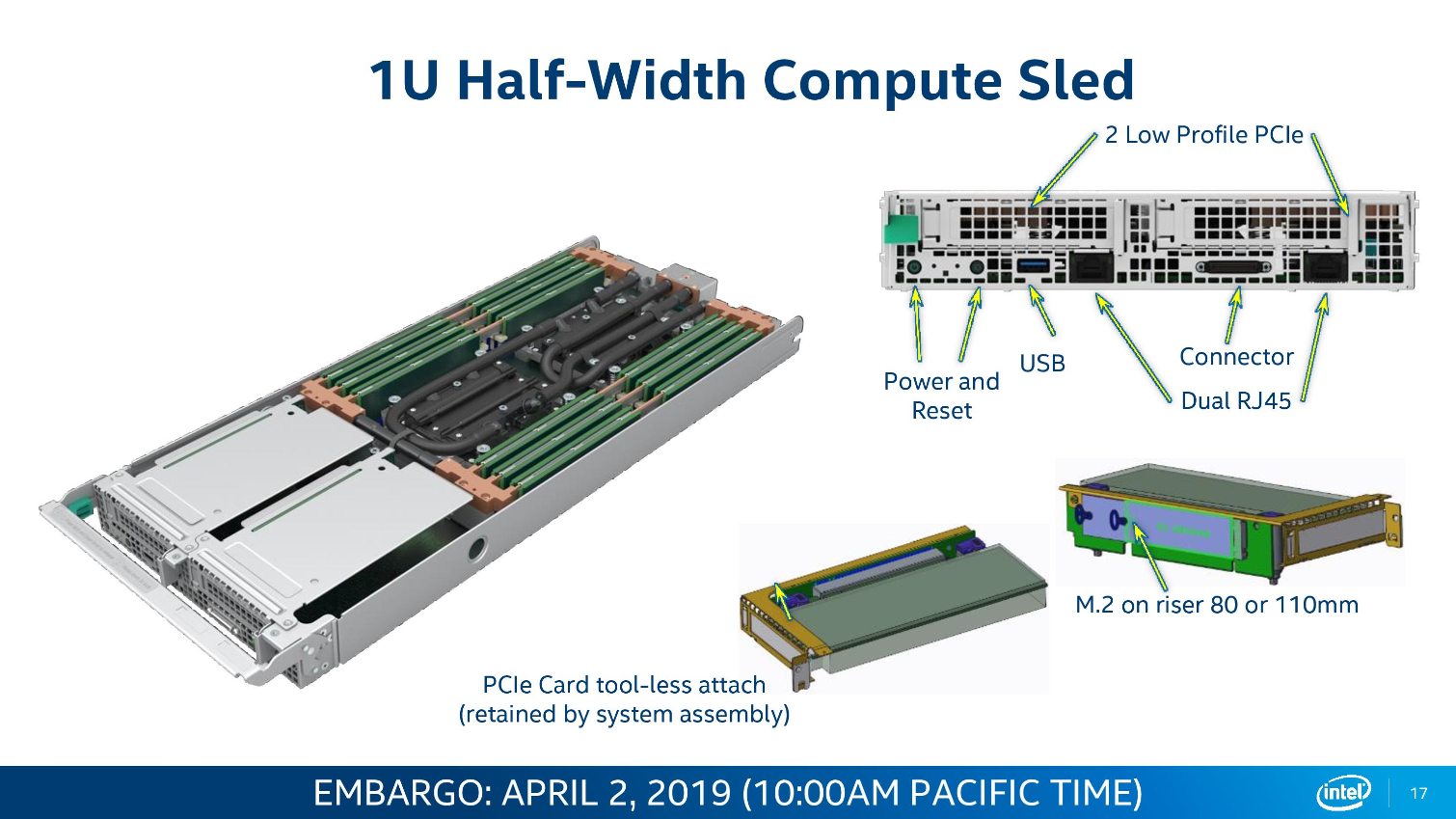

This will reveal my ignorance, but how does one cool a 400W processor? I'm thinking that some sort of massive copper block with large volumes of refrigerated water might just do it. I can't imagine any sort of air cooling doing the job.admin said:Intel tries to upstage AMD's EPYC Rome announcement with its new 56-core processor that comes in a socketed form factor.

Intel Announces Socketed 56-Core Cooper Lake Processors : Read more -

bit_user Reply

Well, if you can cool a 2-slot 275 W GPU with a single blower, then attaching a taller heatsink via a vapor chamber might work.jmcgaw said:This will reveal my ignorance, but how does one cool a 400W processor? I'm thinking that some sort of massive copper block with large volumes of refrigerated water might just do it. I can't imagine any sort of air cooling doing the job.

I've long thought it'd be cool if they used a vapor chamber as the actual heatspreader, integrated into the packaging.

The other thing to consider is that water cooling is becoming more common, in high-performance servers. And consider that water cooling a GPU dissipating 400 W is nothing new or particularly hard. -

bit_user ReplyIntel says the new processors will arrive in the first half of 2020.

Wow. Talk about FUD - this announcement is little more than a transparent ploy to undermine Rome! -

hannibal Heh! AMD in near having its upgrade to Rome at that time :)Reply

Well, competition is good! -

hotaru251 only be interested in these if i was sure they had baked in fixes and i wont lose performance later on.Reply