Intel and Synopsys Demonstrate Xeon ‘Sapphire Rapids’ PCIe 5.0 Interoperability

Intel’s ‘Sapphire Rapids’ platform verified with PCIe IP from Synopsys

Intel and Synopsys have announced that they had successfully demonstrated interoperability between Intel’s next-generation Xeon Scalable ‘Sapphire Rapids’ processors and Synopsys’s PCIe 5.0 controller and physical interface (PHY). The successful validation of Synopsys’s PCIe 5.0 IP with Intel’s upcoming processor has two important implications: the CPU and PCIe 5.0 IP work as planned at a 32 GT/s data transfer rate.

The Demonstration

The demonstration of interoperability between Intel’s upcoming Xeon Scalable ‘Sapphire Rapids’ and Synopsys’s DesignWare IP for PCIe 5.0 is a testament that both the CPU and the PCIe 5.0 solution work as planned. This indicates that upcoming chips supporting a PCIe 5.0 interface using technologies from Synopsys — such as SSD controllers, network adapters, and various accelerators — will work fine with Intel’s 4th Generation Xeon Scalable processor.

"Achieving successful interoperability between Synopsys' DesignWare IP for PCIe 5.0 and Intel Xeon Scalable processors validates that the IP functions as intended with Intel's industry-standard PCIe 5.0 products, accelerating the path to first-silicon success with less risk," said John Koeter, senior vice president of marketing and strategy for IP at Synopsys.

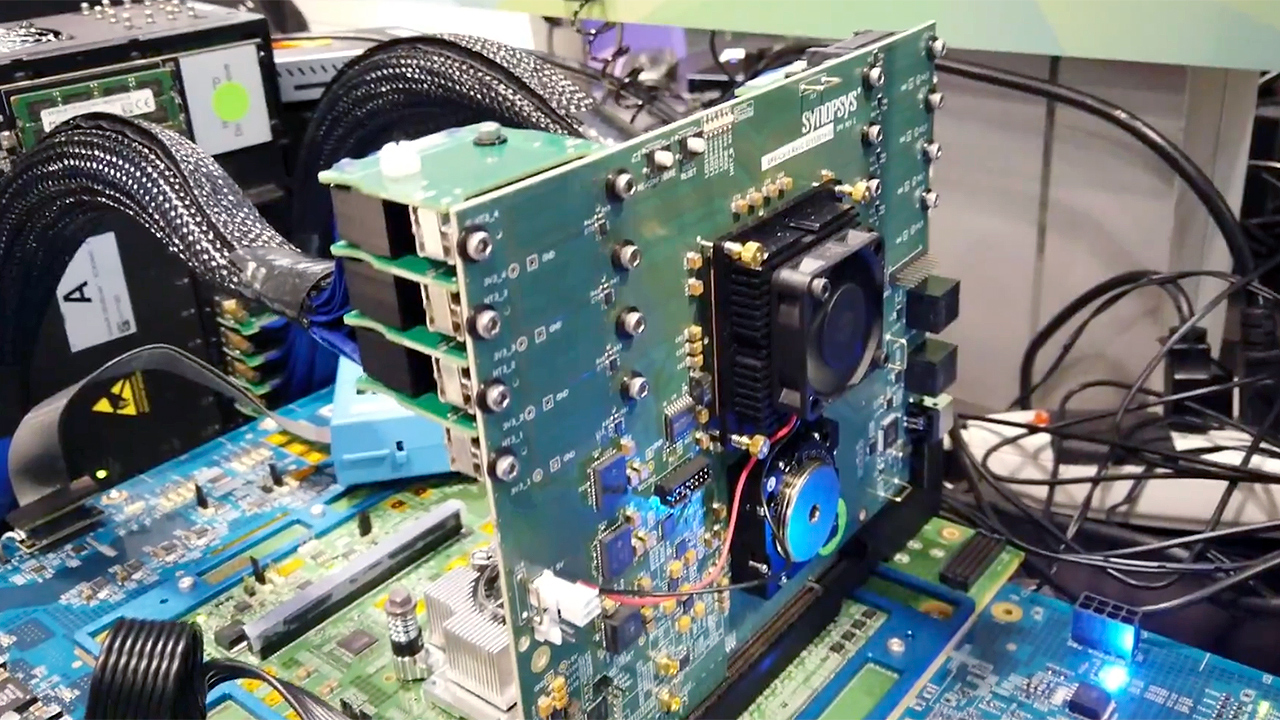

Article continues belowLast year Synopsys demonstrated its CXL over PCIe 5.0 as well as CCIX over PCIe 5.0 solutions using silicon implementations of its PCIe 5.0 with CXL or CCIX controller and appropriate physical interface (PHY) as well as IP prototyping kits. It also demonstrated PCIe 5.0 interoperability between its test chip and an Intel test chip (pictured above). Typically, such demonstrations are enough for system-on-chip (SoC) designers to verify that everything works and start licensing appropriate IP and PHY packages from companies like Synopsys. In fact, Synopsys’s DesignWare IP for PCIe 5.0 has been licensed over a hundred of times already, so there is over a hundred of PCIe 5.0-enabled designs incoming.

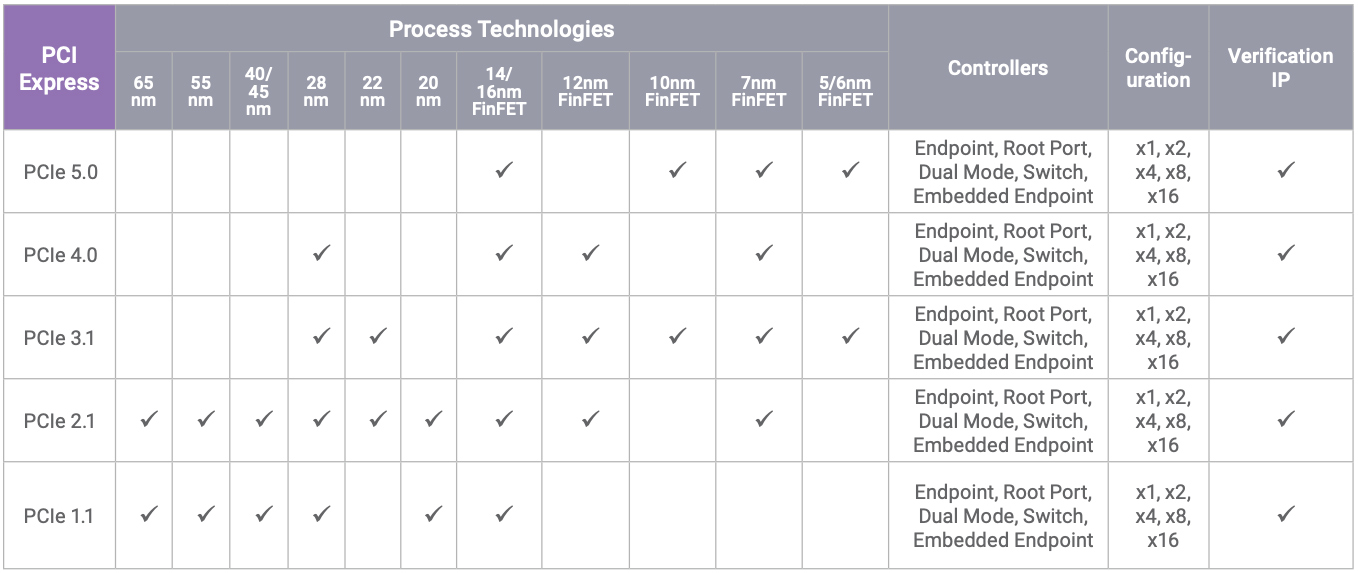

Synopsys currently has DesignWare controller, PHY, and verification IP for PCIe 5.0 in a variety of FinFET fabrication technologies from 16-nm to 5-nm.

An Important Platform

Intel’s codenamed ‘Sapphire Rapids’ CPU, which was first powered on in mid-2020 and is due in late 2021 supports not only the PCIe 5.0 technology, but also the CXL 1.1 protocol. Therefore, it is a bit surprising that Intel and Synopsys did not test CXL 1.1 in addition to PCIe 5.0 at this time

Intel’s next-generation Xeon Scalable ‘Sapphire Rapids’ is a particularly important server platform for the company as it brings not only higher performance enabled by a higher core count and boosted frequencies, but a host of new technologies, including an eight-channel DDR5 memory interface, a PCIe 5.0 interface, the CXL 1.1 protocol, Intel’s Data Streaming Accelerator (DSA) technology, Intel’s Advanced Matrix Extensions (AMX), and AVX512_BF16 as well as AVX512_VP2INTERSECT instructions.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

JayNor A recent notebook check article reports a leak saying Alder Lake-S will have 16 PCIE5 lanes. Looks like Intel has big plans for PCIE5, or maybe for CXL. Have there been any announcements for PCIE5/CXL GPUs other than their supercomputer GPU?Reply