Overclocker Takes DDR5 to 9058 MHz on Ryzen 7000 With Latest Firmware

Zen 4's memory controller is just as capable as Intel's — if not more so.

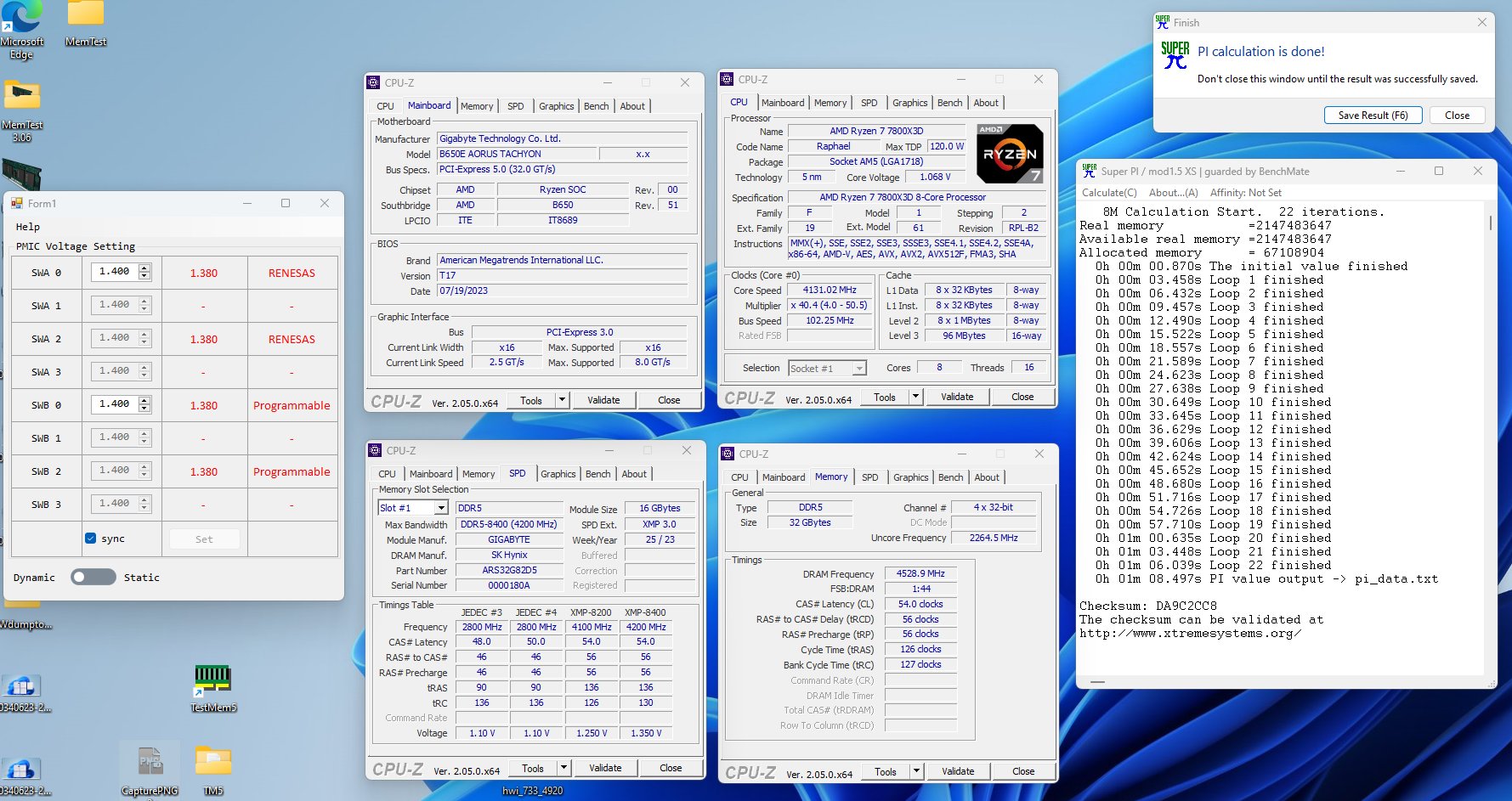

Just days after AMD released its new memory-enhancing AGESA 1.0.0.7b update, HiCookie, one of the world's best-known overclockers, has managed to hit over 9000 MHz on one of his DDR5 memory kits operating on a Ryzen 7 7800X3D system.

This is one of the fastest DDR5 overclocks we've seen to date on any DDR5-supported platform, demonstrating that AM5 has a lot more DDR5 overclocking potential than initially expected. At this rate, we could see 10,000 MHz overclocks in no time — and we might even see Ryzen 7000 systems actively beating Intel's best Alder Lake/Raptor Lake CPUs in memory overclocking for the first time ever.

The overclock was achieved with Gigabyte DDR5-8400 modules on a B650E Aorus Tacyon motherboard with a Ryzen 7 7800X3D CPU. The DDR5 modules were overclocked to 9058 MHz with slightly tighter 54-56-56-126 timings compared to the module's default XMP configuration.

The new AGESA 1.0.0.7b update is arguably the most impactful AMD microcode update we've seen on the AM5 platform to date. The new patch substantially increases memory support (and memory stability, by the looks of it), allowing most Ryzen 7000 CPUs to hit 7000 - 8000 MHz regularly and 6400 MHz in a 1:1 UCLK:MEMCLK ratio, which is optimal for gaming and other latency-sensitive tasks. This is a substantial change from previous patches, where 6000 MHz was the peak most Ryzen 7000 chips could hit stably. Anything beyond 6000 MHz was completely unpredictable.

The new update has a lot of new features that enhance memory stability and boost frequency support, but the primary change that improves higher-frequency DDR5 functionality is a new set of previously-hidden timing parameters that control the Ryzen 7000 memory controller. These settings were hidden from the user in the past — and possibly motherboard manufacturers as well — but now they have opened them up to users and BIOS developers to alleviate any bottlenecks the memory controller might be responsible for.

If overclockers continue to push memory overclocks like this with AMD's new AGESA microcode update, this may be the first real competition we've seen from AMD regarding memory overclocking. Past AMD Ryzen architectures have always had inferior memory overclocking performance, due to the hardware limitations of their memory controllers, compared to Intel. But now it seems like the tables may be turning, and AMD may even have the better-performing memory controller. We'll know this soon enough if memory overclockers start breaking DDR5 frequency world records on AMD hardware.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Aaron Klotz is a contributing writer for Tom’s Hardware, covering news related to computer hardware such as CPUs, and graphics cards.

-

kerberos_20 usualy higher clocks supported means lower bandwith then previous agesa at same clock as something had to be loosened up...saw that few times on AM4, first bios releases had almost 95% bandwith efficiency vs later upgrades lowering it by quite a bitReply -

TechieTwo Unless there is a tangible system performance gain by running the more expensive higher frequency DRAM most users will be better served using a 1:1 UCLK:MEMCLK ratio at 6400 MHz.Reply -

abufrejoval Reply

Me, I mostly bought a 5800X3D, because its V-cache eased my "pain" of ECC modules not going beyond DDR4-3200 and 22 timings.Admin said:An overclocker has pushed one of his DDR5 kits to over 9000MHz on an AMD AM5 system, thanks to the new memory capabilities afforded by the new AGESA 1.0.0.7b microcode update.

Overclocker Takes DDR5 to 9058 MHz on Ryzen 7000 With Latest Firmware : Read more

And with billiong bits (128GB) the chances of a flip seemed to get too big on a 24x7 system without ECC.

The total inability to overclock anything on that platform, gave me a strange peace of mind and a rock stable platform.