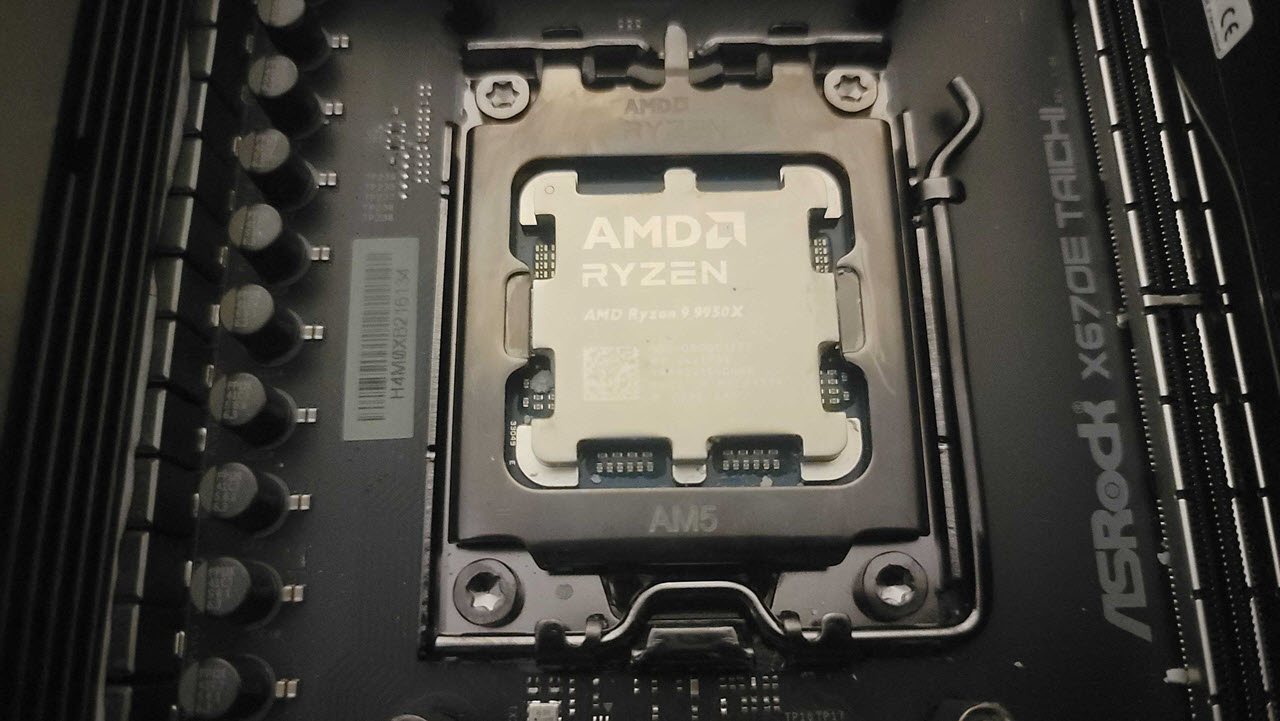

AMD microcode improves cross-CCD latency on Ryzen 9000 CPUs — Ryzen 9 9900X and Ryzen 9 9950X cross-CCD latency cut in half to match previous-gen models

Cross-CCD on Zen 5 dual-CCD CPUs is now in line with Zen 4 chips.

Ryzen 9000 launched with unexpectedly high cross-CCD latency on the dual-CCD models — Ryzen 9 9900X and Ryzen 9 9950X. However, AMD has now rectified the issue with a new AGESA microcode update that cuts the Ryzen 9 9900X and Ryzen 9 9950X's cross-CCD latency in half. User domdtxdissar on the Overclock forums discovered that AGESA microcode update 1.2.0.2 improves performance and cross-CCD latency from 180 ns to 75 ns.

The new microcode update lowers Ryzen 9000's cross-CCD latency to almost identical latencies as the previous generation Ryzen 9 7950X and Ryzen 9 7900X. It is unknown how precisely this change will improve performance, but the Overclock forum user reported that it does improve performance in some form. Inevitably, this change will enhance the performance of latency-sensitive applications that take advantage of multiple CPU cores on Ryzen 9000 chips with a dual-CCD configuration.

This change will most likely not affect gaming because AMD has implemented the same scheduling driver on its Ryzen 7950X3D and 7900X3D chips to its Ryzen 9 9950X and 9900X CPUs. This scheduler will prevent games from utilizing both CCDs simultaneously to maximize performance and minimize system latency.

Multiple outlets discovered Zen 5's oddly long cross-CCD latency when the Ryzen 9 9950X and 9900X first launched. Sister site AnandTech was entirely surprised when it found significantly higher multi-CCD latencies than Zen 4, noting that nothing changed in the architecture to warrant such behavior—Ryzen 9000 uses the same IOD and Infinity Fabric configuration as Ryzen 7000.

However, these latency changes were not created without cause. According to Y-Cruncher author Alexander Yee (sourced from Reddit), one of AMD's architects revealed that the high latency regression in Zen 5 resulted from new tuning parameters they implemented to help boost performance in workloads the company was testing against. The only problem with AMD's tuning was that it did not reportedly account for synthetic benchmarks, which created the high core-to-core latencies seen on latency-sensitive benchmarks.

Zen 5's cross-CCD latency optimizations also reportedly took a long time to develop due to testing and validation, which is why we only see them now. Thankfully, it appears AMD's latency problems were mostly related to synthetic benchmarks, so there's a good chance we won't see significant performance variance with this new AGESA update in regular multi-threaded workloads.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Aaron Klotz is a contributing writer for Tom’s Hardware, covering news related to computer hardware such as CPUs, and graphics cards.

-

phxrider I thought I remembered reading cross CCD communication was supposed to be improved over Zen 4 somewhere?Reply -

helper800 Reply

Did they change the I/O die or infinity fabric speed? I think that is determinative of the latency, no? To be clear I am more of a layman with the minutia of CPU architecture.phxrider said:I thought I remembered reading cross CCD communication was supposed to be improved over Zen 4 somewhere? -

The Historical Fidelity Reply

It could be as simple as the data taking the scenic route between the CCDs lol.helper800 said:Did they change the I/O die or infinity fabric speed? I think that is determinative of the latency, no? To be clear I am more of a layman with the minutia of CPU architecture.

On a serious note, it could be that, due to the particular internal test load they were tuning for, it improved performance to sacrifice latency for increased bandwidth. Some workloads prefer large packets of data getting there at the same time than small bits of data getting there really fast then having to wait until the entire data set arrives. But I could be way off. -

bit_user Reply

Um... what?The article said:one of AMD's architects revealed that the high latency regression in Zen 5 resulted from new tuning parameters they implemented to help boost performance in workloads the company was testing against. The only problem with AMD's tuning was that it did not reportedly account for synthetic benchmarks, which created the high core-to-core latencies seen on latency-sensitive benchmarks.

Zen 5's cross-CCD latency optimizations also reportedly took a long time to develop due to testing and validation, which is why we only see them now. Thankfully, it appears AMD's latency problems were mostly related to synthetic benchmarks, so there's a good chance we won't see significant performance variance with this new AGESA update in regular multi-threaded workloads.

They're saying they tuned some low-level parameters to optimize real workloads, and not bother about synthetics. How can you then conclude that (apparently) reverting the changes to optimize synthetics won't affect performance on real workloads???

The only scenario I see where we don't see a regression in real workload performance is if the synthetics were hitting some corner case they could handle in relative isolation. That seems a little unlikely, but perhaps we'll find out. On that front:

"Users are reporting that they are getting up to 400-600 points improvement in Cinebench R23. A few users who own the Ryzen 9 9950X also report that both CPU-z and 3DMark CPU benchmarks have seen noticeable uplifts and the best part is that the BIOS runs flawlessly without issues."

Source: https://wccftech.com/amd-agesa-1-2-0-2-bios-improves-inter-core-latency-zen-5-ryzen-9000-cpus-major-performance-increases/

So, it does sound all-around positive. I'm hoping Phoronix will run a broad test suite, where I expect we'll probably see at least a few regressions. -

Replybit_user said:"Users are reporting that they are getting up to 400-600 points improvement in Cinebench R23. A few users who own the Ryzen 9 9950X also report that both CPU-z and 3DMark CPU benchmarks have seen noticeable uplifts and the best part is that the BIOS runs flawlessly without issues."Source: https://wccftech.com/amd-agesa-1-2-0-2-bios-improves-inter-core-latency-zen-5-ryzen-9000-cpus-major-performance-increases/

Interesting. My R23 multicore score was 43,323 the other day. Will run again once I get this update and see what kind of improvement I get. MSI is only showing 1.2.0.1 update and it's a trial mode beta version. -

Mama Changa Reply

No they did not. That's coming in Strix Halo )new 3nm IO die) and Zen 6. Zen 6 apparently finally fixes the issues caused by having two ccd's and slow IF.helper800 said:Did they change the I/O die or infinity fabric speed? I think that is determinative of the latency, no? To be clear I am more of a layman with the minutia of CPU architecture. -

usertests Reply

There's no more pretending that Ryzen 9000 wasn't broken at launch.Bikki said:This sounds more like bug fix after rushed release than optimizaton. -

bit_user Reply

No, "broken" means it flatout doesn't work correctly. I think it's more accurate to say it was launched prematurely and without adequate testing & tuning.usertests said:There's no more pretending that Ryzen 9000 wasn't broken at launch.

Let's not forget that AMD just concurrently launched a new desktop & laptop CPU for the first time! They also added the new Strix Halo product tier, that teams are also working on. They sort of had this tier before, with Dragon Range, but this time it's more than just a desktop CPU in a BGA package.

Also, AMD made two versions of both Zen 5 and Zen 5C cores, this time: one for laptops and one for servers. In the case of the server Zen 5C cores, it seems like they're fabbing them on TSMC N3.

My point is that AMD appears to adding product lines and diversifying the underlying technology at a pretty rapid pace. I think what we're seeing is an effect of that, with some resources being stretched thin. Hopefully, they'll be able to pick up some good talent from Intel, with the layoffs and others' stock options underwater.