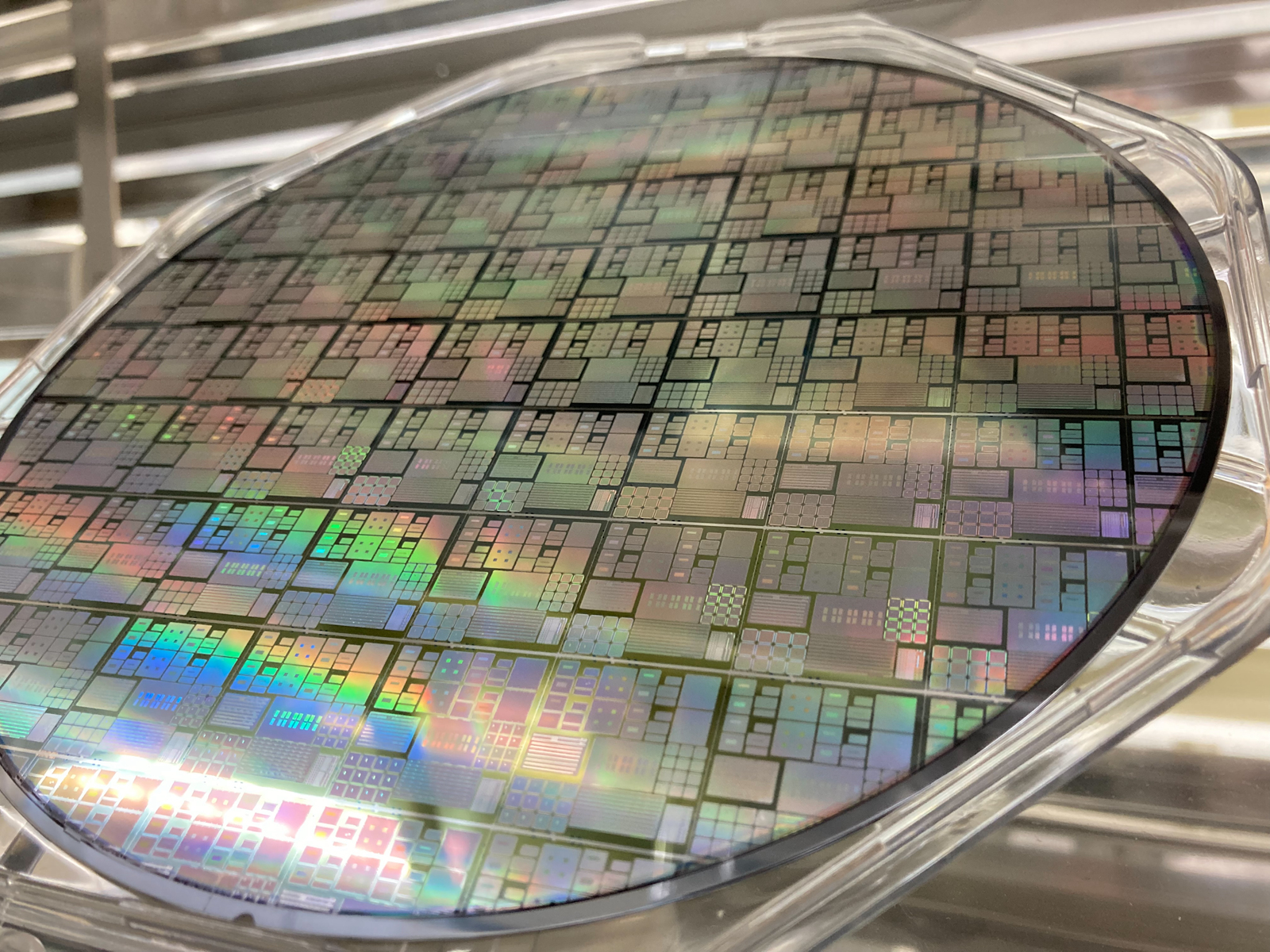

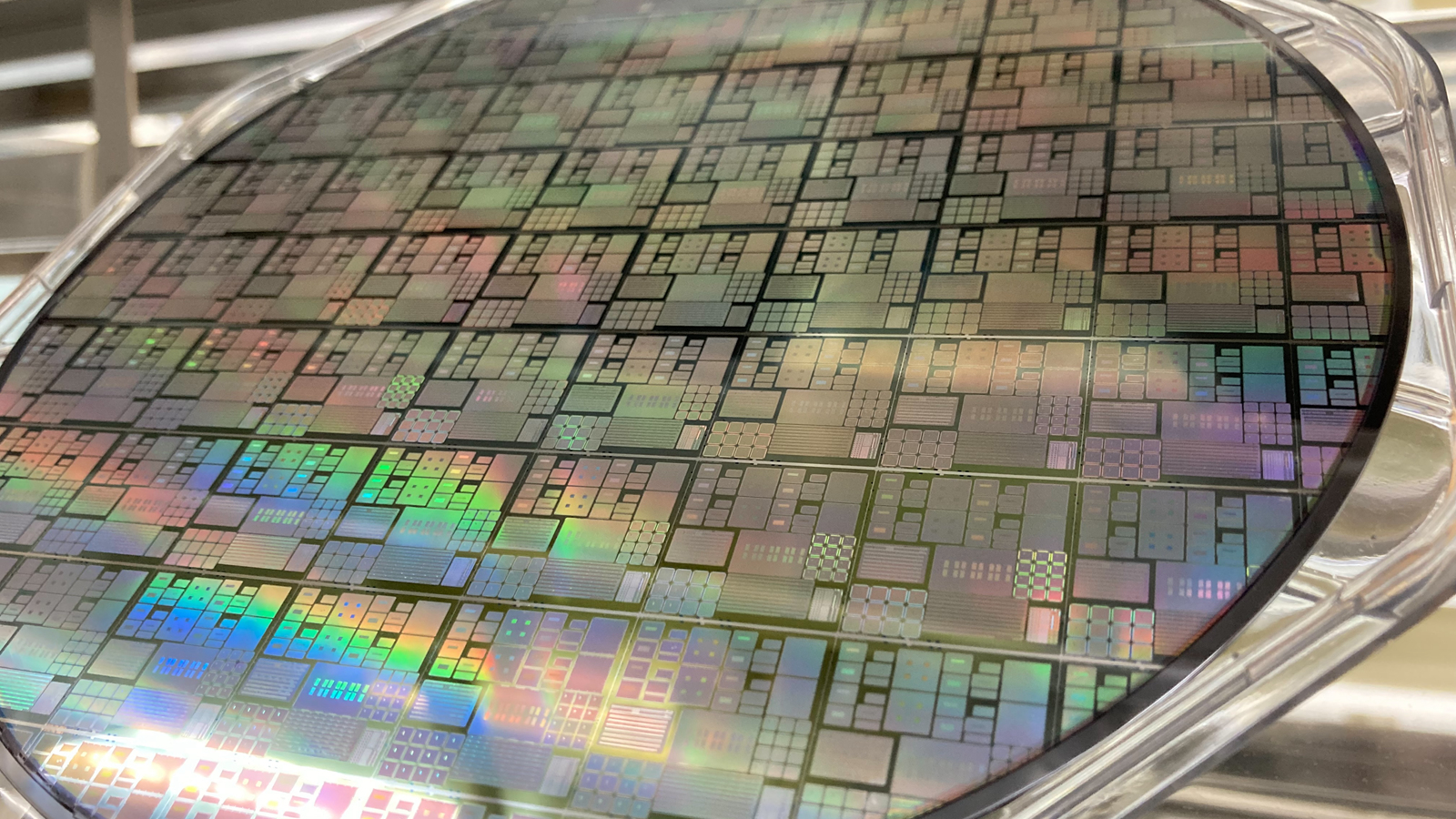

TSMC tandem builds exotic new MRAM-based memory with radically lower latency and power consumption

TSMC and ITRI tout SOT MRAM for in-memory computing applications.

TSMC and Taiwan's Industrial Technology Research Institute (ITRI) on Thursday announced that they had jointly developed co-developed a spin-orbit-torque magnetic random-access memory (SOT-MRAM) array chip, the result of a joint development program the tandem announced in 2022. The memory device can be used for computing in memory architectures and last-level cache, boasting non-volatility, low latencies, and power consumption that is 1% of that of spin-transfer torque (STT) MRAM.

In theory, SOT-MRAM has numerous advantages that make it usable for caches and in-memory applications. SOT-MRAM can potentially offer higher density than SRAM, which barely scales with the latest production technologies. Being non-volatile, it also consumes no power when not in use (unlike SRAM), which is beneficial both for data center and battery-power applications. SOT-MRAM is theoretically capable of latencies up to 10ns, which is certainly slower compared to SRAM (read and write latency of SRAM is typically in the range of 1-2ns), but is slightly faster than DRAM (DDR5 has latency around 14ms) and considerably faster than 3D TLC NAND (which has read latencies between 50 and 100 microseconds).

"This unit cell achieves simultaneous low power consumption and high-speed operation, reaching speeds as rapid as 10ns," said Dr. Shih-Chieh Chang, General Director of Electronic and Optoelectronic System Research Laboratories at ITRI. "Its overall computing performance can be further enhanced when integrated with computing in memory circuit design. Looking ahead, this technology holds the potential for applications in high-performance computing (HPC), artificial intelligence (AI), automotive chips, and more."

Spin-orbit-torque magnetic random-access memory (SOT-MRAM) and spin-transfer torque (STT) MRAM are types of non-volatile memory technology that uses magnetic states to store data. In both SOT and STT MRAM, the memory cell relies on a structure called a magnetic tunnel junction (MTJ) that comprises a free and a fixed thin magnetic layer (e.g., CoFeB) stacked vertically with a very thin dielectric layer (e.g., MgO) sandwiched between them, and an additional 'heavy metal' (e.g., Tungsten) layer adjacent to one of the magnetic layers.

Data is written to the memory cell by changing the magnetization in the free layer (which acts as the 'storage' layer in the MRAM bit cell) by passing a current through the heavy metal layer, which generates a spin current and injects it into the adjacent magnetic layer, switching its orientation and thus changing its state. Reading data involves assessing the magnetoresistance of the MTJ by directing a current through the junction. The main difference between STT- and SOT-MRAM resides in the current injection geometry used for the write process, and apparently, the SOT method ensures lower power consumption and device longevity.

While SOT-MRAM offers lower standby power than SRAM, it needs high currents for write operations, so its dynamic power consumption is still quite high. Furthermore, SOT-SRAM cells are still larger than SRAM cells, and they are harder to make. As a result, while the SOT-SRAM technology looks promising, it is unlikely that it will replace SRAM any time soon. Yet, for in-memory computing applications, SOT-MRAM could make a lot of sense, if not now, but when TSMC learns how to make SOT-MRAM cost-efficiently.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

usertests ReplySOT-MRAM is theoretically capable of latencies up to 10ns, which is certainly slower compared to SRAM (read and write latency of SRAM is typically in the range of 1-2ns), but is slightly faster than DRAM (DDR5 has latency around 14ms) and considerably faster than 3D TLC NAND (which has read latencies between 50 and 100 microseconds).

DRAM = 14 nanoseconds (not milliseconds). The rest look fine. -

user42 Reply

That makes WAY more sense! 14ms is nearly forever compared to 10-14ns.usertests said:DRAM = 14 nanoseconds (not milliseconds). The rest look fine. -

bit_user Reply

I wonder where that number is from. I think the best we've seen in PC benchmarks is somewhere in the realm of 70 ns.usertests said:DRAM = 14 nanoseconds (not milliseconds).

Uh, not NAND.usertests said:The rest look fine.

3D TLC NAND (which has read latencies between 50 and 100 microseconds)

Not according to this:

That's 11-15 microseconds from the time a CPU sends a read request to the SSD's controller, and when it receives back 4 kiB of data. So, the raw latency of 3D TLC NAND is definitely in the lower single digit numbers of microseconds, if that. -

TJ Hooker Reply

If I had to guess, maybe from CAS latency at JEDEC standard timings? It's usually around 14-16 ns.bit_user said:I wonder where that number is from. I think the best we've seen in PC benchmarks is somewhere in the realm of 70 ns. -

bit_user Reply

But that's not a full access (CAS = Column Address Strobe), right? To provide comparable figures, you want to look at the amount of time for a random access to get the actual data.TJ Hooker said:If I had to guess, maybe from CAS latency at JEDEC standard timings? It's usually around 14-16 ns. -

thestryker MRAM has been the next big thing for like 40 years so I'll believe it when it gets into a production unit.Reply -

TJ Hooker Reply

Oh, yeah, I don't think using CL provides an apples to apples comparison, just speculating on where the number may have come from.bit_user said:But that's not a full access (CAS = Column Address Strobe), right? To provide comparable figures, you want to look at the amount of time for a random access to get the actual data. -

d0x360 "jointly developed co-developed a spin-orbit-torque magnetic random-access memory (SOT-MRAM) array chip, the result of a joint development"Reply

So you're saying it was developed in cooperation with another company?

Seriously who wrote this? So from 4 years ago? A single CO developed there is no hyphen btw, would have been sufficient but this sounds like it was written by a 5th grader who doesn't understand what they are saying. -

subspruce Reply

DRAM latencies used to go down to 6ns in the DDR3 days.usertests said:DRAM = 14 nanoseconds (not milliseconds). The rest look fine.