Inside the future of 3D NAND: The roadmap to 500 layers

By 2027, 4800 MT/s speeds and 500-layer stacks could be a reality

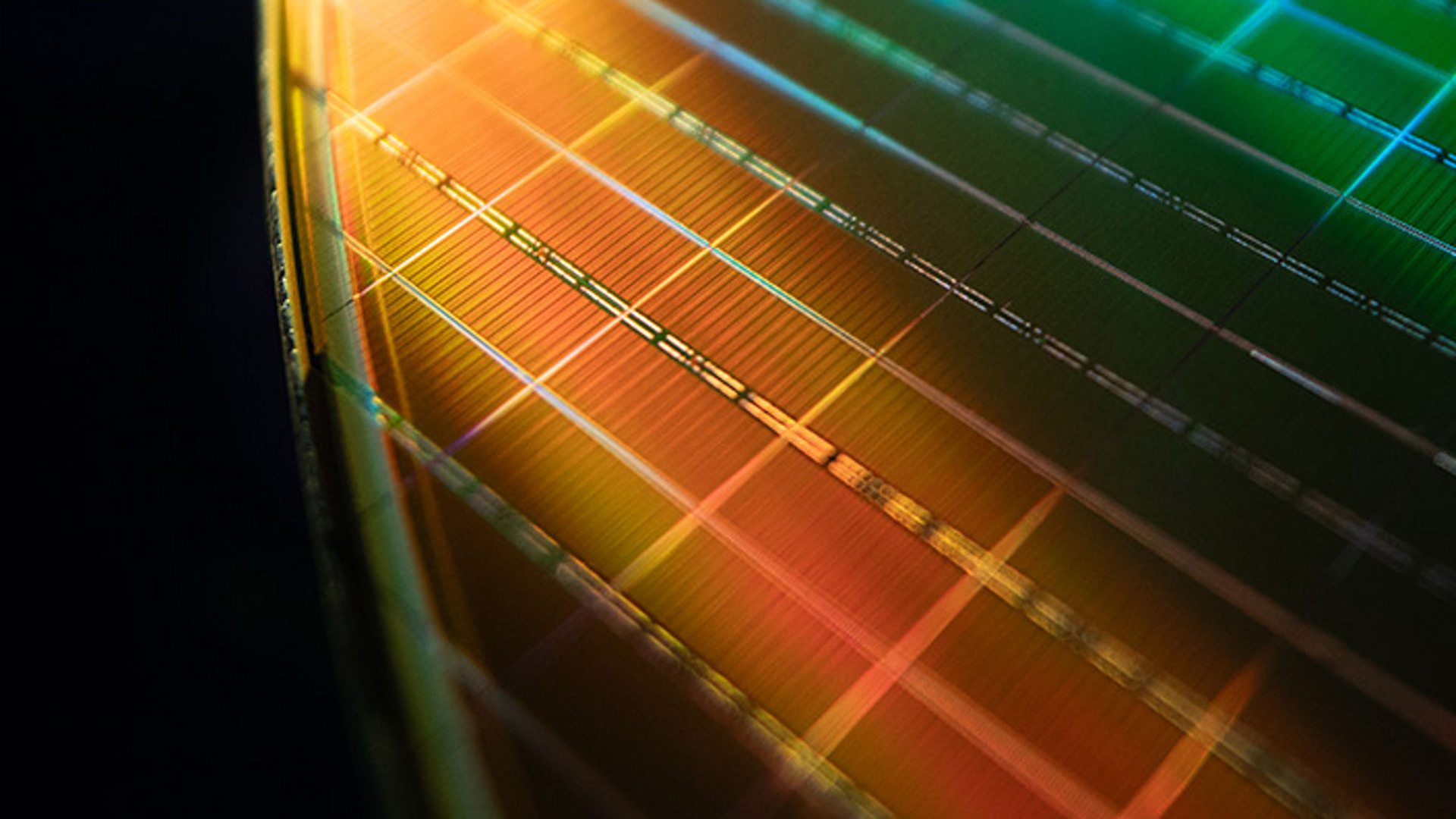

Decades of evolution have made NAND flash memory both cheap and incredibly sophisticated. No matter what modern device you pick up, the likelihood is that it will use some kind of NAND, which has become ubiquitous in both consumer products and data centers. If you cast your mind back several decades, NAND was expensive, despite its capability to be faster than spinning disks. As the technology has matured, its use has grown exponentially. But what's next?

In the coming years, we're going to see cheaper, more advanced non-volatile flash memory inside our devices. Those 3D NAND devices will be built from over 500 layers and boast interface speeds of up to 4800 MT/s. This blistering speed may pave the way to all-new kinds of devices with significantly increased performance compared to today's best SSDs.

The next step

Like other technologies, 3D NAND develops in multiple directions. End users demand higher capacity, higher performance, lower power, compact dimensions, and lower cost. Manufacturers themselves want to earn money, so while meeting demand, they try to cut costs by making smaller memory devices. Given the current state of industry development, the best way to keep the size of 3D NAND dies in check is to increase the number of layers and decrease the size of the actual data storage location — the memory cell itself. This practice is commonplace among memory makers today.

Leading makers of 3D NAND memory, including Kioxia, Micron, Samsung, SK Hynix, and YMTC, have all developed multiple 3D NAND generations, consistently increasing layer counts while reducing cell sizes. For now, the majority of 3D NAND-based devices, including SSDs and smartphones, rely on memory with 2xx layers, with each layer holding an incredible number of memory cells for data storage.

This might be 218-layer 3D NAND from Kioxia, 232-layer 3D NAND from Micron, or 286-layer 3D NAND from Samsung.

The pace at which manufacturers adopt new layer counts and boost transfer rates varies across the industry, making things difficult to track. So let's examine where we were in 2023, how it's going, and where we might be in 2027. Just as a reminder: Kioxia also has a close production partnership with Western Digital's flash division, which also owns SanDisk as a subsidiary. Within this article, we'll refer to the duo as Kioxia / Western Digital.

Manufacturer | Date | Product | Type | Layers | Speed | Capacity |

|---|---|---|---|---|---|---|

Kioxia / Western Digital | 2023 H1 | BiCS 6T | TLC | 162 | 2400 MT/s | - |

Micron | 2023 H1 | B58 | QLC | 232 | 2400 MT/s | - |

SK hynix | 2023 H1 | V7Q | QLC | 176 | 2000 MT/s | - |

YMTC | 2023 H1 | X3-9060 | TLC | - | 2400 MT/s | - |

Kioxia / Western Digital | 2023 H2 | BiCS 6Q | QLC | 162 | 2400 MT/s | - |

Samsung | 2023 H2 | V8T | TLC | 236 | 2400 MT/s | - |

Samsung | 2023 H2 | V7Q | QLC | 176 | 2000 MT/s | - |

SK hynix | 2023 H2 | V8T | TLC | 238 | 2400 MT/s | - |

YMTC | 2023 H2 | X3-6070 | QLC | - | 2400 MT/s | - |

Micron | 2024 H1 | N58 | QLC | 232 | 2400 MT/s | - |

YMTC | 2024 H1 | X4-9060 | TLC | 128 | 3600 MT/s | - |

Kioxia / Western Digital | 2024 H2 | BiCS 8T | TLC | 218 - 232 | 3600 MT/s | - |

Micron | 2024 H2 | B68S | TLC | 276 | 3600 MT/s | - |

Samsung | 2024 H2 | V9T | TLC | 286 | 3000 MT/s | - |

YMTC | 2024 H2 | X3-9070 | TLC | 232 | 3600 MT/s | - |

Samsung | 2025 H1 | V9Q | QLC | 286 | 3600 MT/s | 1 Tb |

SK hynix | 2025 H1 | V9T | TLC | 321 | 2400 MT/s | - |

YMTC | 2025 H1 | X4-6080 | QLC | - | 3600 MT/s | - |

Kioxia / Western Digital | 2025 H2 | BiCS 8Q | QLC | 232 | 3600 MT/s | 1Tb |

Micron | 2025 H2 | N69 | QLC | - | 3600 MT/s | - |

SK hynix | 2025 H2 | V9T | QLC | 321 | 3600 MT/s | - |

SK hynix | 2025 H2 | V9Q | QLC | - | 3200 MT/s | 2 Tb |

Kioxia / Western Digital | 2026 H1 | BiCS 8Q | QLC | 232 | 3600 MT/s | 2 Tb |

YMTC | 2026 H1 | X5-9080 | QLC | - | 4800 MT/s | - |

Samsung | 2026 H2 | V9Q | QLC | 286L | 3600 MT/s | 2 Tb |

YMTC | 2026 H2 | X5-6080 | QLC | - | 4800 MT/s | - |

Kioxia / Western Digital | 2027 H1 | BiCS 9T | TLC | >300 | 4800 MT/s | - |

Micron | 2027 H1 | B78 | TLC | - | 4800 MT/s | - |

Samsung | 2027 H1 | V10T | TLC | >400 | 4800 MT/s | - |

SK hynix | 2027 H1 | V10T | TLC | 500 | 4800 MT/s | - |

SK hynix | 2027 H1 | V10Q | QLC | 500 | 4800 MT/s | - |

YMTC | 2027 H1 | X5-9070 | TLC | - | 4800 MT/s | 1 Tb |

Micron | 2027 H2 | N79 | QLC | - | 4800 MT/s | - |

Samsung | 2027 H2 | V11T | TLC | - | 4800 MT/s | - |

In recent years, the industry faced significant challenges in building an SSD with a PCIe 5.0 x4 interface that would fully saturate that interface. ICs with a high-performance interface that could fully saturate the lane using an eight-channel controller (e.g., 2400 MT/s) are rare. Instead, ICs that supported lower speeds are much more common.

By early 2023, all three major NAND vendors — Kioxia / Western Digital, Micron, and Samsung — had established 2400 MT/s as the baseline interface speed across TLC products. Kioxia's BiCS 6T and 6Q nodes, Micron’s B58, and Samsung’s V8T are representative of these tiers as a mainstream standard, and perhaps this reflects a consistent performance scaling for both consumer and enterprise storage segments.

In 2024, Samsung took the next incremental step by introducing its V9T TLC at 3000 MT/s. This intermediate speed tier, not shared by other vendors in the roadmap, highlights Samsung’s focus on being a vertically integrated company that focuses mainly on its own-brand products, like smartphones and SSDs.

Kioxia / Western Digital reached 3200 MT/s in the second half of 2024, with its 8th Gen BiCS 3D TLC, followed by QLC (BiCS 8Q) products in 2025 H2. However, Kioxia / Western Digital has not mentioned using 7th Gen products at all, skipping it entirely.

This reflects a general push to align both TLC and QLC offerings on higher-performance platforms. Notably, Kioxia / Western Digital is the only vendor explicitly listed in the roadmap as deploying 3200 MT/s in both cell types, showing a strong commitment to QLC performance uplift.

In 2024, Micron came to leadership with its B68S IC, sporting a 3600 MT/s data transfer rate. By the second half of 2025, the company’s QLC roadmap plans to catch up with Samsung via the N69 generation. This highlights Micron’s early adoption of faster interfaces for high-end products, but since it's yet to be released, its impact and uptake remain to be seen. Kioxia/Western Digital also lists its BiCS 8Q QLC reaching 3600 MT/s in 2025 H2, indicating a broader QLC performance push across the industry.

All vendors eventually converge at 4800 MT/s by 2027, which becomes the high-performance standard. Kioxia/WD reaches this milestone with BiCS 9T TLC in 2027 H1, Micron with B78 TLC and N79 QLC in 2027 H1–H2, and Samsung with its 11th generation of V-NAND.

Performance headwinds

Manufacturing high-speed NAND flash (3600 MT/s and higher) requires a more expensive logic process technology, which drives up production costs and inflates flash memory prices.

An increase in 3D NAND data transfer rates will have a very practical implication on how devices like SSDs or smartphones are built.

To fully saturate a PCIe 5.0 x4 interface — which provides up to 15.75 GB/s of effective bandwidth — a modern NAND flash setup requires an SSD controller with eight channels at 2400 MT/s, six channels at 3600 MT/s, or just four channels at 4800 MT/s. In a year or two, PCIe 5.0 SSD controllers won't require eight channels to fully saturate the hungry interface.

For PCIe 6.0 x4, which doubles throughput to around 31.5 GB/s effective (after protocol overhead), the number of required channels increases 16 at 2400 MT/s, 12 at 3600 MT/s, and eight at 4800 MT/s. As NAND I/O performance approaches these thresholds, high-end SSDs can exploit PCIe 6.0 capabilities with eight high-speed NAND devices. However, it remains to be seen whether PCIe 6.0 x4 SSDs will be a reality for consumer storage devices within the next few years.

Die capacities

Based on the roadmap data that we have collated, leading 3D NAND makers will converge, landing with 1 Tb and 2 Tb die capacities by around 2026 - 2027, particularly for 3D QLC products. While there are some 2Tb QLC NAND devices announced as of May 2025, none of them are actually on the market yet.

Micron, Kioxia/Western Digital, Samsung, SK Hynix, and YMTC all plan to offer 3D QLC devices reaching 2 Tb capacities, typically paired with interface speeds of 3200MT/s – 4800 MT/s over the next few years. Despite the significantly increased layer count, 3D NAND manufacturers are not jumping to capacities higher than 2Tbs per device for the time being, perhaps due to cost concerns.

Rising layer counts: How does each company stack up?

Kicking off with Kioxia and Western Digital, this duo's 3D NAND roadmap featured BiCS 6 with 162 layers across both TLC and QLC variants in the first half of 2023. BiCS 6 represents a mature and commercially proven node, used in mainstream SSDs and enterprise storage. This generation aligns with the industry’s transition toward high-density vertical stacking, while supporting a 2400 MT/s interface speed.

Kioxia and Western Digital didn't stop there, and in the second half of 2024, these companies introduced BiCS 8 in both TLC (BiCS 8T) and QLC (BiCS 8Q) forms, now featuring between 218 and 232 layers. This generation continues to rely on 2400 MT/s – 3600 MT/s interfaces, marking both vertical and performance scaling. Also, it demonstrates Kioxia’s intent to advance QLC’s competitiveness in both storage density and performance.

BiCS 8 will be a fairly long-standing node for Kioxia and Western Digital, as it will be replaced in the first half of 2027. BiCS 9T is set to replace it, boasting a layer count of greater than 300, representing quite an aggressive step forward. This milestone puts Kioxia in alignment with other vendors’ 3D NAND scaling targets, while also introducing 4800 MT/s interface speeds.

Micron’s lineup includes the now legendary B58 IC with 232 layers and a 2400 MT/s data transfer rate. But its 1st Gen ICs featured a lower rate; its full speed was only achieved sometime in the first half of 2023. Nevertheless, the B58 gave Micron an early lead in vertical scaling versus competitors still shipping 162–192 layer products.

In the second half of 2024, Micron advanced to the B68S IC, increasing the layer count to 276. This generation pairs higher density with elevated performance (3600 MT/s), making it a major step in Micron’s 3D NAND roadmap, and making the company one of the leading makers of enthusiast-grade SSDs with the model 4600.

In the first half of 2027, Micron is expected to introduce its B78 3D TLC NAND ICs, with a 4800 MT/s interface. However, the exact layer count is not known. Given the trend from B58 (232L) to B68S (276L), it is reasonable to expect B78 to reach well beyond 300 layers, likely on par with Kioxia’s and Samsung’s leading nodes. However, there are no official materials on exact layer counts, so this remains speculation.

When it comes to 3D NAND makers, Samsung is a rare animal. All producers of flash memory prefer to sell their chips as parts of their own devices, such as SSDs, and to that end, Micron works closely with Silicon Motion and Phison to optimize controllers for its memory and drives. In a similar vein, Kioxia works with Phison. Unlike its rivals, Samsung has its own 3D NAND and controllers to build its SSDs and other products using NAND flash memory. The company also sells its 3D NAND ICs on the open market as an additional boon.

Samsung offered its V8T IC in 2023 H2 with 236 layers, placing it alongside Micron’s B58 and slightly ahead of Kioxia’s BiCS 6. This node continues to be Samsung’s workhorse today.

By the second half of 2025, Samsung is set to mass produce V9T, scaling to 286 layers — a 50-layer jump over V8T. This milestone indicates V9T’s interface speed remains at 3600 MT/s, indicating a controlled ramp before moving to more aggressive performance targets.

Looking ahead to 2026 H1, Samsung’s roadmap lists V10T IC with an expected layer count of over 400, representing the most ambitious vertical target. While this node’s interface speed is also pegged at 4800 MT/s, its standout feature is the sheer layer height, suggesting multi-tier stacking and next-gen integration techniques, such as string stacking and hybrid bonding. However, Samsung has not officially announced that it is using any of those specific techniques quite yet.

SK hynix’s current product lineup includes the V8T IC with 238 layers, a 2400 MT/s interface, and has been available since the second half of 2023, marking their entry into late-Gen 3D NAND scaling. The next major leap occurs with V9T, reaching 321 layers in the first half of 2025, and then increasing interface performance to 3600 MT/s by the second half of 2025.

This shows a rapid vertical scaling effort while improving I/O bandwidth. The company's most ambitious node, V10T, is set to debut in 2027 H1, with 500 layers and a 4800 MT/s interface — matching top-tier bandwidth targets from other vendors, and surpassing them in vertical stack height. The roadmap extends further to V11T (4800 MT/s), though its layer count is not explicitly known.

On the QLC side, SK hynix’s roadmap begins with V7Q in the first half of 2024 at 176 layers, then it extends to V9Q, which delivers 3200 MT/s performance and a 2 Tb die capacity — implying a 300L+ stack. By the first half of 2027, QLC products are also expected to adopt the 500-layer structure (V10Q) at 4800 MT/s, mirroring TLC’s configuration.

When it comes to layer counts, China-based YMTC is not a leader, but its 3D NAND development shows a clear trajectory from mid-tier to high-tier stacking. YMTC’s 3D TLC product (X4-9060) features 128 layers and a 3600 MT/s interface, and was followed quickly by X3-9070 in the second half of 2024. X3-9070 jumped to 232 layers while maintaining the same data transfer rate. This indicates a rapid scaling of vertical density — despite sanctions by the U.S. government. This is likely enabled by the company’s proprietary Xtacking architecture, which separates logic and memory layers to simplify integration. However, no QLC-specific layer counts are known for now.

By 2026 – 2027, YMTC’s roadmap aims to enter the high-performance class of its competitors. The X5-9080 and X5-9070 3D TLC NAND products operate at 4800 MT/s, and the latter is explicitly listed as a 1 Tb die, suggesting a likely move to 300+ layers, although exact counts are not known. Meanwhile, the company’s 3D QLC line (e.g., X4-6080, X5-6080) appears on the roadmap in parallel, also reaching 4800 MT/s by the second half of 2026, hinting at comparable architectural advances.

YMTC’s roadmap outlines a fast-paced rise from 128L to 232L and potentially 300L+ stacking within three years—driven by a balance of aggressive layer scaling and interface speed improvements across both TLC and QLC products.

What's next for 3D NAND?

The future of 3D NAND is defined by fairly aggressive vertical scaling, faster interfaces, and a push toward higher per-die capacities, which will enable products that will enable faster, denser, and more cost-efficient storage across consumer and enterprise segments. To make that happen, all major vendors are set to converge at a 4800 MT/s interface speed and 300–500-layer stacks by 2027.

However, this progress is not without complexity. Vertical scaling introduces new challenges in terms of yield, while higher speeds now also require logic process nodes, which raises manufacturing costs. Eventually, when everyone in 3D NAND manufacturing converges at hybrid bonding (which YMTC already uses, while sporting one of the industry’s widest patent portfolios). These techniques will add another layer of complexity, and companies will require some time to get used to these new processes.

In any case, the future of 3D NAND is bright, as the industry races towards faster speeds, higher stacks, and more complex manufacturing technology.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.