IDF Spring 2006: Will Intel's Core Architecture Close the Technology Gap?

Advanced Smart Cache

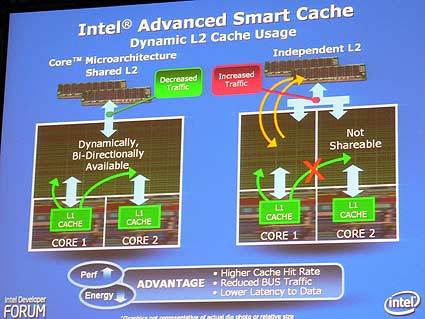

The unified L2 cache probably is the feature that is mentioned first. It allows for a large L2 cache to be shared by two processing cores (2 MB or 4 MB). Caching can be more effective because data is no longer stored twice into different L2 caches any more (no replication). The full L2 cache is highly dynamic and can adapt to each core's load, which means that one single core may allocate 100% of the L2 cache area dynamically if this is required (on a line by line basis).

Sharing data also is more efficient now, because no front side bus load is generated while reading or writing into the cache (which is the case with the Pentium D), and there is no stalling when both cores are trying to access it. A good example that shows the advantages in multi-threaded environments is one core writing data into the cache, while the other may read something else at the same time. Cache misses are reduced, latency goes down, and access by itself also is faster now, because the Front Side Bus definitely was a limiting factor.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: Advanced Smart Cache

Prev Page Advanced Digital Media Boost Next Page Smart Memory Access

Patrick Schmid was the editor-in-chief for Tom's Hardware from 2005 to 2006. He wrote numerous articles on a wide range of hardware topics, including storage, CPUs, and system builds.