IDF Spring 2006: Will Intel's Core Architecture Close the Technology Gap?

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

The Memory Controller Question

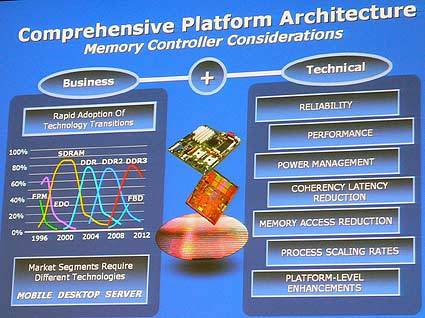

Having gone through the key features of Intel's upcoming Core micro architecture, some people, especially at AMD, may still complain that there will still be the front side bus, and there will still be the memory controller within the Northbridge, a long data path away from the processor, with higher latency, etc. AMD's memory controller, which is part of the Athlon 64 processor, scales beautifully with processor clock speeds and provide enough bandwidth at DDR400 speeds to compete against conventional platforms with DDR2-667 memory.

However, the approach that Intel takes equally makes sense: Why should it integrate the memory controller if it can achieve even better overall performance by applying other techniques? Intel's line of arguments is that a Northbridge memory controller is more flexible: Platform and processor architecture may be updated independently from one another. At the same time, integrated graphics controllers (which are used in the majority of systems sold today) still benefit from memory being "local" in the Northbridge.

As systems scale up to two or more processor sockets, memory coherency between several memory controllers will require much design effort, while the complete memory management is done by one single memory unit in Intel systems. Power saving could be another issue: With integrated controllers, it is impossible to move the CPU to lower power states as long as the memory needs to be active.

At this point, we should also mention Intel's upcoming I/O Acceleration Technology (IOAT), which is designed to move I/O data directly into the memory, while bypassing the processor. This could not be done without creating a system traffic FSB if the memory controller were integrated.

This discussion can go on for a long time, but at the end of the day most users won't care about how their systems actually work, but how efficient they are.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: The Memory Controller Question

Prev Page Intelligent Power Capability Next Page There Is More To Save

Patrick Schmid was the editor-in-chief for Tom's Hardware from 2005 to 2006. He wrote numerous articles on a wide range of hardware topics, including storage, CPUs, and system builds.