The Panther stalks: Intel’s Panther Lake CPUs set to take off in Oregon, company reveals, and cutting-edge 18A process is on track

18A is in the middle of the yield ramp curve.

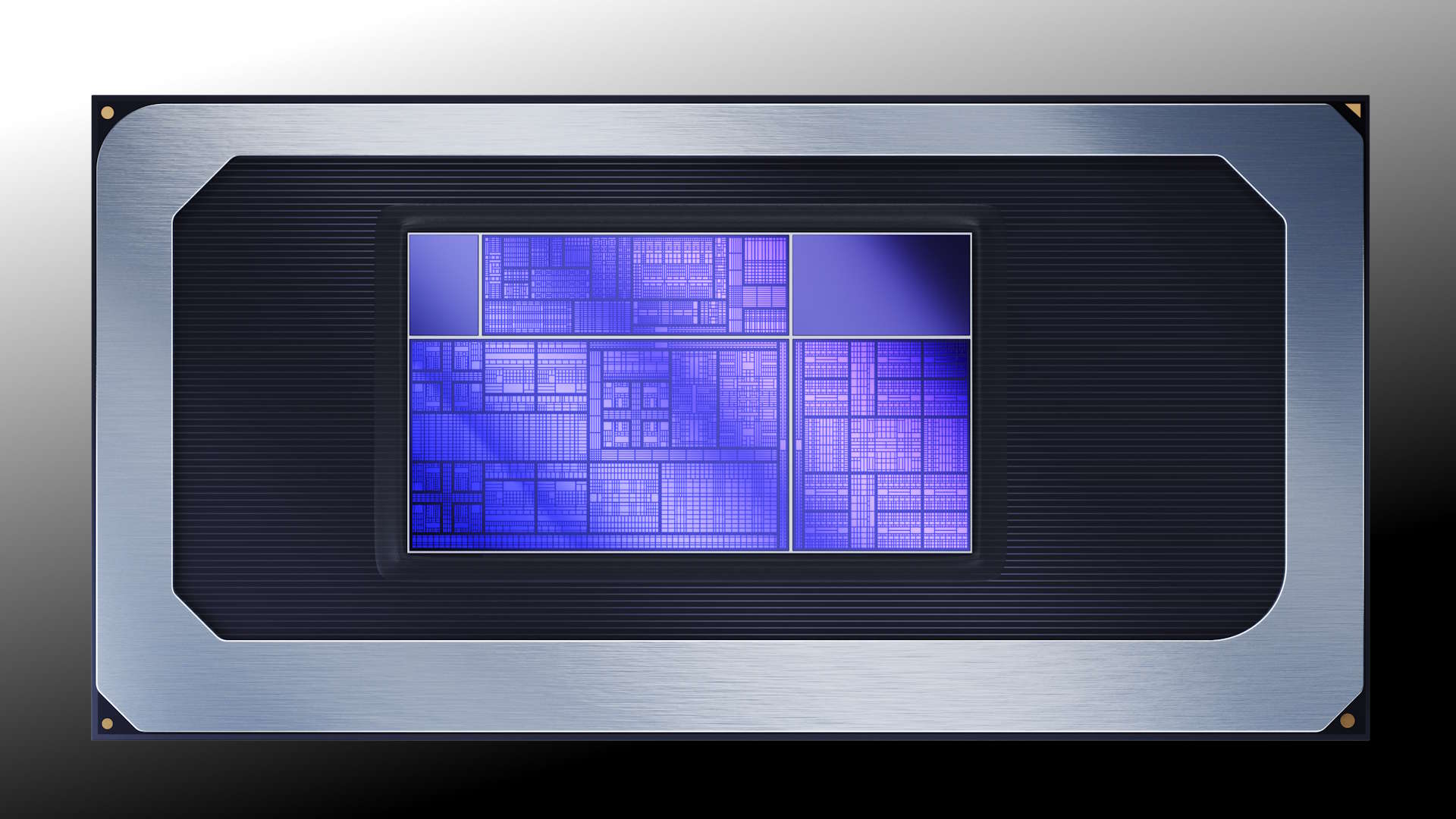

Intel faces serious threat in the laptop market, not just from its nemesis AMD but also Qualcomm and Apple, thanks to the arrival of high-performance, highly efficient ARM cores that have forced the chipmaker to up every part of its game to compete. With 50% more oomph and 30% less power draw, the Core Ultra 3-series 'Panther Lake' processor is a robust response to those rivals — and at a financial event on Tuesday, Intel announced enormous progress toward delivering the goods.

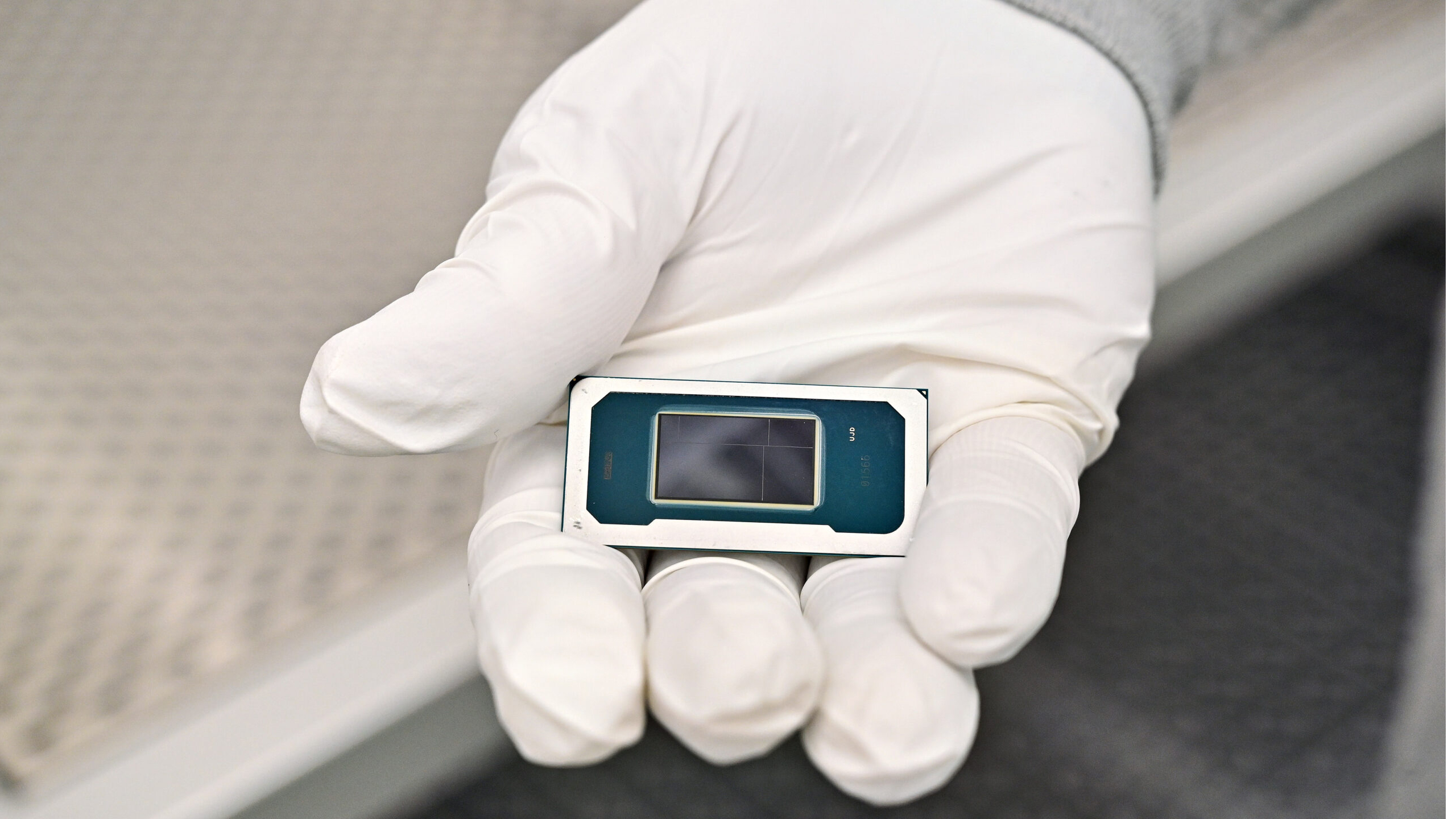

When Intel announced mass production of Panther Lake about a month ago, the company openly admitted that all wafers for the initial CPUs would be made at pilot production lines in Oregon; the new Arizona fabs built on CHIPS ACT money would catch up later. Later means Q1, apparently, and the Arizona fabs should ramp up, the company said. This means costs might stay low, and crucially, yields will grow quickly (though likely remain low in 2026), all of which spells good news for anyone considering a new laptop.

“We now have a predictable path for yield improvement,” said John Pitzer, corporate vice president of corporate planning and investor relations at Intel.

Panther Lake is one of the first products to be fabricated on Intel's leading-edge 18A node, likely the industry's first high-volume process to incorporate two major innovations meant to enable future scaling and power efficiency gains: gate-all-around (GAA) transistors, which Intel calls RibbonFETs, and a backside power delivery network, which Intel calls PowerVia.

Efficient, cutting edge, and on time? For Intel, Panther Lake may be a rare animal indeed.

Low yields, high costs, but a good improvement pace

"Initially on any new process, we take wafers from Oregon," said John Pitzer, corporate vice president of corporate planning and investor relations at Intel, at RBC Capital Markets Global Technology, Internet, Media & Telecommunications Conference 2025. "Oregon is where we do all of our technology development and then move into quasi high-volume manufacturing."

"Those wafers tend to be pretty expensive. Most, if not all, of the Panther Lake wafers this year are coming from Oregon. As we transition into Q1, you will start to see wafers coming in from Arizona [which] has a much better and different cost structure, and that ramps throughout the year," Pitzer said.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Most likely, Intel has not yet initiated mass production of Panther Lake's compute tiles using its 18A process technology at Fab 52 in Arizona due to low yields. The company wants to achieve the highest yield possible on its pilot lines at the D1X fab in Ohio, where developers of the production nodes and process engineers are, and only then transfer the recipe to its production facility in Arizona. As a result, Intel is poised to use low-yield, high-cost wafers for the initial batches of Panther Lake, which is not good news for its costs – but a normal situation in the chip-making world.

There’s good news here about Intel's 18A yields: They are finally increasing at a predictable pace of 7% per month, which is common for the middle phase of every process ramp. Intel does not divulge whether these are functional or parametric yields, which somewhat devalues the claim, but it still reflects Intel's vision about the progress of its 18A node.

"I think one of the things that has changed dramatically over the last seven or eight months, is, we now have a predictable path for yield improvement," Pitzer said. "We have [said] in the past that the industry average yield improvement on a new ramp is about 7% per month and we are now on that curve for Panther Lake, which is giving us some confidence as we launch the product this quarter."

18A is on the right curve, but Panther Lake will be a rare animal

When a new leading-edge production technology like 18A enters volume production, yields typically rise by a predictable improvement curve every month. A 7% yield improvement per month is normal for the middle phase of the ramp, though it is generally lower in the early and late phases as yield-curves tend to be S-shaped.

Intel says that 18A is now following this exact 7% trend for Panther Lake, which is important because past Intel nodes failed to do so and demonstrated chaotic yield improvements or even drops. This is famously why Intel cancelled 20A a little over a year ago; using chips with such a risky yield meant the product schedule was insecure. Hitting the 'industry-normal' yield ramp means the process is stable, and Intel can predict where it is going to be with Panther Lake yields a quarter or two down the road.

An avid reader might ask why Intel measures yield improvement per month, while modern process technologies (e.g., TSMC N3 or Intel 18A) have cycles that are around 120 days long. This actually happens because fabs track the defect density (D0) and process quality at the moment wafers enter the line, not when they finish.

Chipmakers tend to implement fixes — lithography tuning, etch-uniformity adjustments, systematic-defect removal — that immediately change defect density and the projected final yield of wafers started that month, even though those wafers will not complete for another three or four months. Since these changes reduce defects continuously, chipmakers can calculate the expected yield right away using standard yield models. Hence, once Intel's models show continuous improvements for 18A in general and Panther Lake compute tile in particular, the company can safely launch the CPU commercially.

Of course, when we talk about any yield-improvement curve, an elephant in the room is the starting point. If we start from 25% and improve yields by 7% per month, we reach an industry normal 85% good die yield in 8.5 – 9 months, sometime in early fall 2026. Meanwhile, Intel itself claims that 18A will reach industry standard yields in early 2027, which means that for now, yields are probably 10% to 15%.

Costly at first, but for whom?

Starting quasi volume production with low yields at a development fab is a good way to skyrocket costs; D1D's pilot lines are designed not for efficiency but rather for maximum flexibility, to maximize yields. Intel notes that it will start making compute tiles for Panther Lake in early 2026 at Fab 52, which given the S-shaped good-die yield curve, will be around the time when PNL's GDY hits stable 20% – 25%.

While initiating mass production with such a yield means high costs, retaining production at pilot lines is still more expensive, so moving production of Panther Lake's compute tiles to Arizona makes great sense for Intel. Furthermore, high-volume fabs tend to reveal systematic issues that occur with a process technology, which lets the company perform continuous process improvements to ramp yields and lower performance variations through statistical process control, something impossible to do at pilot lines.

Of course, using a high-volume fab with low yields will hit Intel's bottom line heavily, but this is inevitable.

Follow Tom's Hardware on Google News, or add us as a preferred source, to get our latest news, analysis, & reviews in your feeds.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

Gururu Reply

I thought so at first then he went and joined Gloo, which changed my mind.ezst036 said:Intel fired Pat Gelsinger way too soon. -

ottonis "With 50% more oomph and 30% less power draw"So, is it 50% faster while drawing 30% less power than its predecessor, or does it draw 30% less power only whn it operates at the same speed as the comparison model?Reply -

thestryker Reply

l believe the statement is conflating this from the PTL announcement information:ottonis said:"With 50% more oomph and 30% less power draw"So, is it 50% faster while drawing 30% less power than its predecessor, or does it draw 30% less power only whn it operates at the same speed as the comparison model?

The multi-threaded performance story for Panther Lake is a bit muddier. Intel claims that Panther Lake can deliver 50% more performance at similar power to Lunar Lake, or 30% lower power for multi-threaded performance similar to Arrow Lake-H.

Effectively as efficient as LNL but as powerful as ARL which is an impressive feat, if it proves true, since it has 8 E-cores and LNL had none (4P/8E/4LPE vs 4P/4LPE). -

thestryker This would explain the late volume ramp: Oregon doesn't have the capacity to do a full OEM ramp so I'm guessing we'll see the highest margin parts and they'll sit on those binned for the lower until Arizona is running volume.Reply

I'm also not really sure that the PTL yields are as bad as the article surmises. There's no doubt that they're low, but the die should be rather small which will improve yield rates. When they're talking about industry acceptable levels in 2027 that undoubtedly refers to external margins which realistically Intel doesn't have to worry about.

A handful of mistakes in the article:

The company wants to achieve the highest yield possible on its pilot lines at the D1X fab in Ohio

Oregon

D1D's pilot lines are designed not for efficiency but rather for maximum flexibility

D1X

around the time when PNL's GDY hits stable 20% – 25%.

Pretty sure this is supposed to be PTL.