TSMC begins quietly volume production of 2nm-class chips — first GAA transistor for TSMC claims up to 15% improvement at ISO power

As planned.

TSMC has quietly revealed that it had commenced volume production of chips using its N2 (2nm-class) fabrication process. The company did not issue a formal press release notifying about the production start, but the firm had said multiple times that N2 was on track for volume manufacturing in Q4, so the plan has been fulfilled.

"TSMC’s 2nm (N2) technology has started volume production in 4Q25 as planned," a statement at TSMC's web page dedicated to 2nm Technology reads.

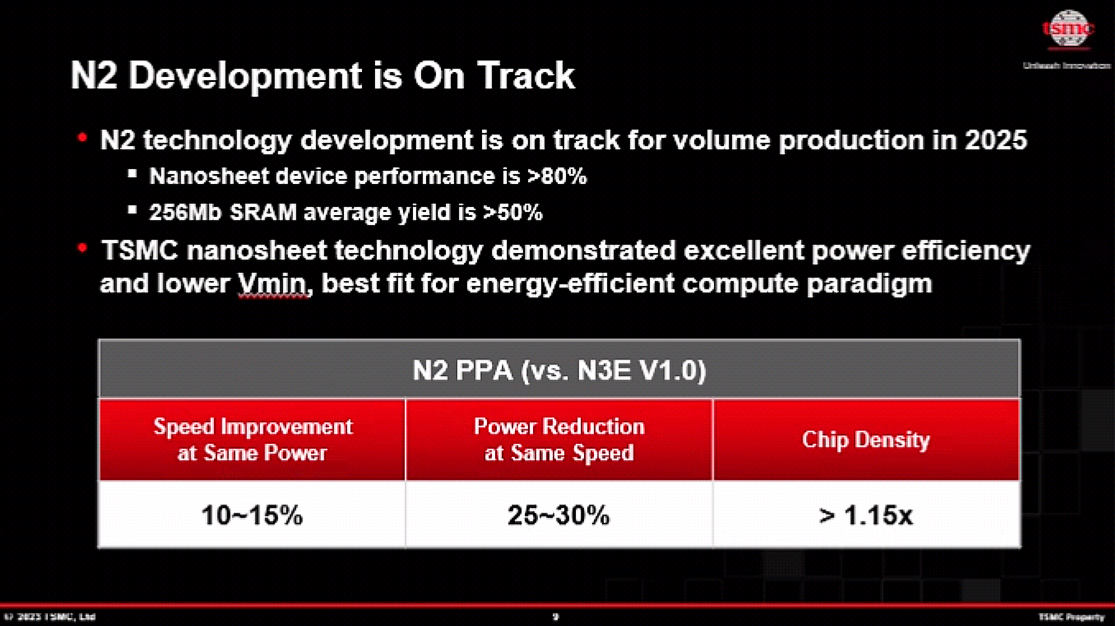

From an improvement standpoint, N2 is designed to deliver a 10%–15% performance gain at the same power, a 25%–30% reduction in power at the same performance, and a 15% increase in transistor density compared to N3E for mixed designs that include logic, analog, and SRAM. For logic-only designs, transistor density is up to 20% higher than N3E.

| Row 0 - Cell 0 | N2 vs N3E | N2P vs N3E | N2P vs N2 | A16 vs N2P | N2X vs N2P |

Power** | -25% ~ -30% | -36% | -5% ~ -10% | -15% ~ -20% | lower |

Performance*** | 10% - 15% | 18% | 5% - 10% | 8% - 10% | 10% |

Density* | 1.15x | 1.15x | ? | 1.07x - 1.10x | ? |

Transistor | GAA | GAA | GAA | GAA | GAA |

Power Delivery | Front-side w/ SHPMIM | Front-side w/ SHPMIM | Front-side w/ SHPMIM | SPR | Front-side w/ SHPMIM (?) |

HVM | H2 2025 | H2 2026 | H2 2026 | H2 2026 | 2027 |

*Chip density published by TSMC reflects 'mixed' chip density consisting of 50% logic, 30% SRAM, and 20% analog.

**At the same speed.

***At the same power.

TSMC's N2 is the company's first process node to adopt gate-all-around (GAA) nanosheet transistors, where the gate fully surrounds the channel formed by stacked horizontal nanosheets. This geometry improves electrostatic control, reduces leakage, and enables smaller transistors without sacrificing performance or power efficiency, ultimately increasing transistor density. In addition, N2 also adds super-high-performance metal-insulator-metal (SHPMIM) capacitors to the power delivery network. These offer more than twice the capacitance density of the prior SHDMIM design and cut both sheet resistance (Rs) and via resistance (Rc) by 50%, which improves power stability, performance, and overall energy efficiency.

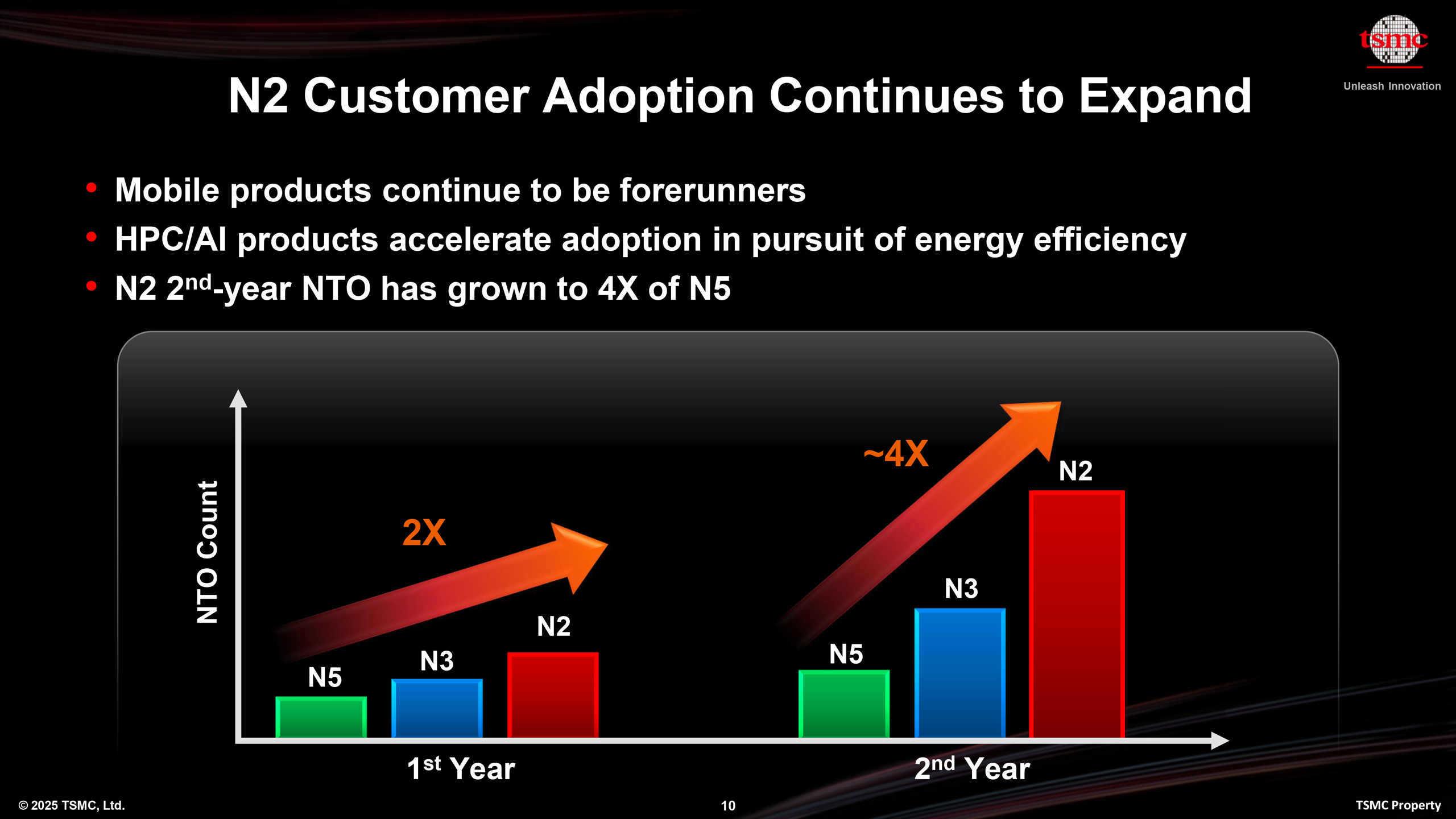

"N2 is well on track for volume production later this quarter, with good yield," said C.C. Wei, chief executive of TSMC, during the company's earnings call in October. "We expect a faster ramp in 2026, fueled by both smartphone and HPC AI applications."

What is interesting is that the company began to make 2nm-class chips at its Fab 22, which is located near Kaohsiung, Taiwan. Previously it was expected that TSMC would begin ramping up N2 production at Fab 20 (near Hsinchu, Taiwan), which is adjacent to its new global R&D center, where N2-series fabrication technologies were developed. Fab 20 will likely commence mass production a bit later.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

TSMC will be ramping up mass production of N2-based chips at brand-new fabs, which is always a bit tricky. What is noteworthy is that the company will ramp production of both smartphone and larger 'AI' and 'HPC' designs at new fabs (note that HPC is a vague term that describes everything from game console SoCs all the way to heavy-duty server CPUs), which will add some additional complexities. Normally, TSMC ramps new nodes with mobile and small consumer designs.

Ramping up two N2-capable fabs at once is a result of strong interest for the new process technology by a variety of TSMC partners, so it needs to offer decent capacity for all of them. Furthermore, starting late 2026, both fabs will be used to build chips on N2P, a performance-enhanced version of N2, and A16, a version of N2P with the Super Power Rail backside power delivery that is aimed at complex AI and HPC processors.

"With our strategy of continuous enhancements, we will also introduce N2P as an extension of our N2 family," Wei added. "N2P features further performance and power benefits on top of N2 and volume production scheduled for second half 2026. We also introduced A16 featuring our best-in-class Super Power Rail, or SPR. A16 is best suited for specific HPC products with complex signal routes and dense power delivery networks. Volume production is on track for second half 2026."

Follow Tom's Hardware on Google News, or add us as a preferred source, to get our latest news, analysis, & reviews in your feeds.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.