AMD's Ryzen 7 7800X3D Has Already Been Overclocked to 5.4 GHz

External Clock Generators to the rescue!

Asus overclocker SkatterBencher published a new video today where he was able to overclock AMD's best CPU for gaming, the Ryzen 7 7800X3D to 5.4GHz, despite the chip's overclocking limitations. He successfully bypassed AMD's 5 GHz ceiling by using external clock generators to overclock the CPU cores.

AMD's Ryzen 7 7800X3D is the new gaming champion among PC processors, delivering blisteringly fast gaming performance with the help of 3D V-Cache technology. However, the thermal limitations of the 3D stacking tech have forced AMD to disable manual overclocking on the chip, with the exception of Precision Boost Overdrive or PBO and AMD's Curve Optimizer.

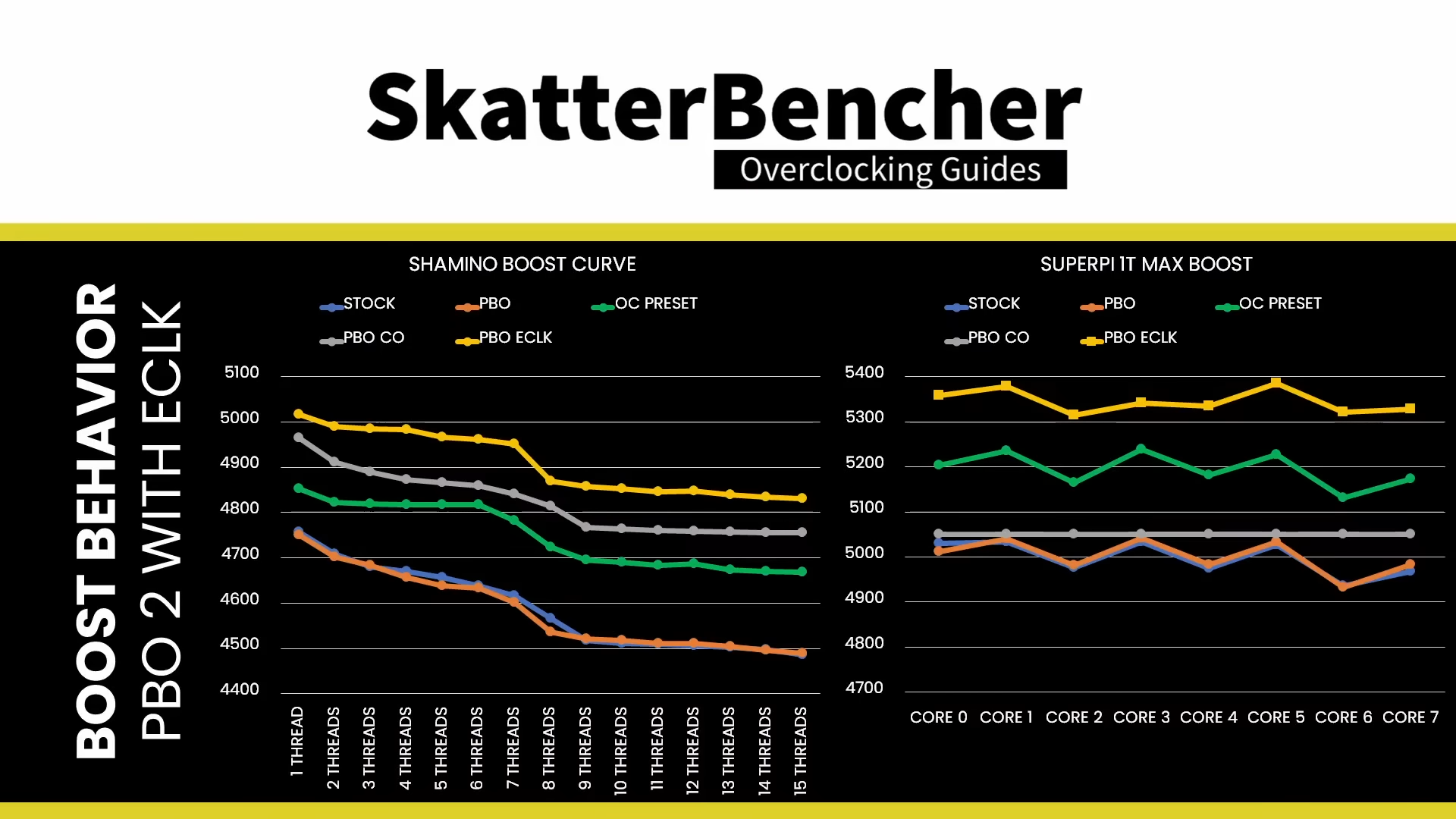

SkatterBencher was able to get around this problem with the help of an Asus ROG Crosshair X670E Hero that has not one, but two external clock generators to aid in overclocking. To achieve 5.4GHz, SkatterBencher used a unique combination of multiple features, including the external clock generator, Precision Boost Overdrive, and AMD's Curve Optimizer to boost clock speeds.

This overclocking strategy is complicated, but the execution is very effective. Precision Boost Overdrive is used to prevent power limitations from occurring on the chip. The external clock generator is used to physically boost clock speeds, and the curve optimizer is used to — not undervolt — but overvolt the chip beyond stock voltages to keep clocks stable.

This led to a 5.4 GHz peak boost on a single core, with a 4.85 GHz boost clock on all eight cores at voltages well under 1.2v. This represents a 7.7% boost to boost frequencies and a 10% boost to single-core clocks compared to stock frequencies.

The overclock is very impressive and shows how much headroom is actually available in some of these chips. Only time will tell how quickly the 7800X3D will degrade with the overvolt applied, but the overclock is impressive nonetheless. With a clock of 5.4 GHz, you effectively have the same compute performance as a standard Ryzen 7 7700X with the additional L3 3DV-Cache to boost gaming performance.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Aaron Klotz is a contributing writer for Tom’s Hardware, covering news related to computer hardware such as CPUs, and graphics cards.

-

Rico Ismail ReplyAdmin said:AMD's "locked" Ryzen 7 7800X3D has been overclocked to 5.4 GHz with the help of PBO, AMD's curve optimizer, and external clock generators.

AMD's Ryzen 7 7800X3D Has Already Been Overclocked to 5.4 GHz : Read more

There three big mistakes AMD has made on this CHIP

Placing L3 cache to expensive 5nm silicone makes Ryzen chip more expensive

Placing 3D stacked cache die on top of CCD die and makes more thermal and overclocking issues

Making multiple CCD instead single 16 core CCD makes in some cases 8 cores perform better than 12 or 16 cores due to communication between cores in different CCD

The disadvantages of placing 3D V-cache on top of CCD

The X3D model need watercooling because its cannot go over 89 celcius or performance is reduced for saving its life

The 3D stacked cache can be die if v-core voltage is set too high, or chip will die and cannot boot again

TDP Limitation, thermal limitation, overclocking limitation make this cip just run at low performance level

Solution :

Place 3D stacked cache on top of IOD

Use infinity cache for ceapest way to remove L3 from 5nm silicon CCD

Use single 16 core CCD without L3 cache but 1,5 MB L2 each core due to L3 cache location is now far away

Idea :

Making a CCD consist of 16 Zen 4 cores, without L3 cache on 5nm silicon, make it more cheaper. But increase L2 to 1.5 MB each or 2MB due to far L3 location

Makes 64MB of L3 infinity cache to replace expensive L3 cache on 5nm CCD

For X3D model, place the 3D Stacked Cache on TOP OF IOD since IOD will stay cool

Benefit :

Removing 64MB L3 cache from 5nm silicone will make PRICE CUT over ryzen CPU, and make AMD Ryzen price per performance ratio better again than competitor(Blue team).

CCD can reach its maximum clockspeed and reach highest TDP available without disturbing 3D stacked cache, since 3d stacked cache placed on top of IOD. Making overclocker feel more happy.

No lag communication between cores in different CCD, since they placed 16 cores into one CCD and it also makes better multicore performance.

When 6 cores, 8 cores model access same level of 64MB infinity cache, it will make performance boost over previous models with twice of L3 cache size.

On 3D model they use both 64MB L3 infinity cache + 64MB stacked 3D cache placed on top of IOD so they will be 128MB total L3 cache, bigest mainstream L3 cache on market and also overclock capabilities rather than placed 3d stacked cache on top of CCD. -

tamalero Reply

You really have no idea what was Ryzen's history of success at all. Do you?Rico Ismail said:There three big mistakes AMD has made on this CHIP

Placing L3 cache to expensive 5nm silicone makes Ryzen chip more expensive

Placing 3D stacked cache die on top of CCD die and makes more thermal and overclocking issues

Making multiple CCD instead single 16 core CCD makes in some cases 8 cores perform better than 12 or 16 cores due to communication between cores in different CCD

The disadvantages of placing 3D V-cache on top of CCD

The X3D model need watercooling because its cannot go over 89 celcius or performance is reduced for saving its life

The 3D stacked cache can be die if v-core voltage is set too high, or chip will die and cannot boot again

TDP Limitation, thermal limitation, overclocking limitation make this cip just run at low performance levelSolution :

Place 3D stacked cache on top of IOD

Use infinity cache for ceapest way to remove L3 from 5nm silicon CCD

Use single 16 core CCD without L3 cache but 1,5 MB L2 each core due to L3 cache location is now far awayIdea :

Making a CCD consist of 16 Zen 4 cores, without L3 cache on 5nm silicon, make it more cheaper. But increase L2 to 1.5 MB each or 2MB due to far L3 location

Makes 64MB of L3 infinity cache to replace expensive L3 cache on 5nm CCD

For X3D model, place the 3D Stacked Cache on TOP OF IOD since IOD will stay coolBenefit :

Removing 64MB L3 cache from 5nm silicone will make PRICE CUT over ryzen CPU, and make AMD Ryzen price per performance ratio better again than competitor(Blue team).

CCD can reach its maximum clockspeed and reach highest TDP available without disturbing 3D stacked cache, since 3d stacked cache placed on top of IOD. Making overclocker feel more happy.

No lag communication between cores in different CCD, since they placed 16 cores into one CCD and it also makes better multicore performance.

When 6 cores, 8 cores model access same level of 64MB infinity cache, it will make performance boost over previous models with twice of L3 cache size.

On 3D model they use both 64MB L3 infinity cache + 64MB stacked 3D cache placed on top of IOD so they will be 128MB total L3 cache, bigest mainstream L3 cache on market and also overclock capabilities rather than placed 3d stacked cache on top of CCD.

The usage of smaller chiplets is what gave AMD a HUGE advantage in costs and scalability.

And why make 16 core ccds when the mainstream users do not use more than 8?

Also the 7800X does not have "multiple ccds". It has only a single 8 core ccd. So you're confusing the 7950X 3d and 79003d with this one. -

-Fran- Yeah, I'm getting the impression AMD is either being WAY too conservative with the Zen4 VCache siblings or they're holding them back on purpose...Reply

I mean, I can see why they have to be careful, don't get me wrong as the VCache is, indeed, super sensitive to voltages and heat, but the temperatures these CPUs reach is laughably low and there's room still, temperature wise. Not sure voltage wise, but it seems there's also some room voltage wise.

Oh welp, I hope I'm flat out wrong.

Regards. -

P1nky Reply-Fran- said:Yeah, I'm getting the impression AMD is either being WAY too conservative with the Zen4 VCache siblings or they're holding them back on purpose...

I mean, I can see why they have to be careful, don't get me wrong as the VCache is, indeed, super sensitive to voltages and heat, but the temperatures these CPUs reach is laughably low and there's room still, temperature wise. Not sure voltage wise, but it seems there's also some room voltage wise.

Oh welp, I hope I'm flat out wrong.

Regards.

Somebody didn't watch the video. -

-Fran- Reply

Uh... What did I miss from the video in my comment?P1nky said:Somebody didn't watch the video.

Regards. -

Wrss ReplyRico Ismail said:

Solution :

Place 3D stacked cache on top of IOD

Use infinity cache for ceapest way to remove L3 from 5nm silicon CCD

Use single 16 core CCD without L3 cache but 1,5 MB L2 each core due to L3 cache location is now far away

You propose a way bigger mistake. Infinity Fabric 2.0 bandwidth ceiling is <100 GB/s. Zen 4 3D cache bandwidth on a single CCD is 600+ GB/s. Regular L3 cache on a single CCD is 800+ GB/s. This is measured by AIDA64.

The bandwidth is what makes games more fluid while not helping with most apps. You're better off not paying for any 3D cache on the IOD, as it has barely more bandwidth to the CCD than DDR5 can provide itself. It's the same reason Intel with the monolithic DDR5 controller is smoother in games than the non-3D cache Zen 4's. Better bandwidth to the DDR5 itself when not having to go across IF 2.0. -

Rico Ismail Replytamalero said:You really have no idea what was Ryzen's history of success at all. Do you?

The usage of smaller chiplets is what gave AMD a HUGE advantage in costs and scalability.

And why make 16 core ccds when the mainstream users do not use more than 8?

Also the 7800X does not have "multiple ccds". It has only a single 8 core ccd. So you're confusing the 7950X 3d and 79003d with this one.

They need to remove 32MB or 64MB (on two CCD) from expensive 5nm pricey silicon to cutting cost, place it on Infinity Fabric and/or Placing 3D stacked cache on top OF IOD. AMD usually go for right silicon on right usage, such 6nm for IOD, 7nm for stacked cache, fast and expensive 5nm on CPU Cores but not for large cache like L3.

Do you think every 7600X, 7700, or 7800X3D just only have one CCD? Although they only have 8 or 6 cores, sometimes they have two CCD on placed CHIP, but one of them are Not USED (Disabled). They Called this -- To maximize its production resources--. Source : https://www.tomshardware.com/news/amd-recycles-dual-chiplet-ryzen-7000-as-ryzen-5-7600x-cpus

So why not using CHEAP ONE CCD (without L3 cache) consist of 16 cores rather than disabling one expensive CCD consisct 32MB L3 cache on the 7600X or 7700X or 7800X3D? When using only ONE CCD, they will perform better on 12 and 16 cores since all cores is placed on same die -

Rico Ismail ReplyWrss said:You propose a way bigger mistake. Infinity Fabric 2.0 bandwidth ceiling is <100 GB/s. Zen 4 3D cache bandwidth on a single CCD is 600+ GB/s. Regular L3 cache on a single CCD is 800+ GB/s. This is measured by AIDA64.

The bandwidth is what makes games more fluid while not helping with most apps. You're better off not paying for any 3D cache on the IOD, as it has barely more bandwidth to the CCD than DDR5 can provide itself. It's the same reason Intel with the monolithic DDR5 controller is smoother in games than the non-3D cache Zen 4's. Better bandwidth to the DDR5 itself when not having to go across IF 2.0.

Infinity fabric 2.0 is an old way, now AMD says infinity fabric 3.0 has peak 800GB/s so it's fast enough to placing 3D stacked cache on it. source -- https://www.amd.com/en/technologies/infinity-architecture -- but infinity link on RX 7900 XTX have 5.3 TB/s bandwidth between MCD and GCD. So why not using infinity link instead infinity fabric on Ryzen, epyc, and Threadripper? But i have no idea how fast infinity cache is(128 MB on RX6900XT).

You right, i think placing 3D stacked cache on fabric link maybe a better idea than on IOD, if only using slow infinity fabric 3, but not if using fast infinity link.

I think Game Lagging on non 3D model happen because low bandwidth speed on infinity fabric between IOD and CCD when L3 cache is full. Why not using 5.3TB/s infinity link like Navi 31 rather than 800GB/s infinity fabric 3.0 ? -- https://videocardz.com/newz/amd-radeon-rx-7000-rdna3-infinity-links-operate-at-9-2-gb-s-10x-higher-bandwidth-density-than-ryzen-infinity-fabric -

tamalero Reply

infinity fabric speed is no where near the speed of cache. You're gimping expensive Cache with infinity fabric. And the point of cache was that.. alleviate the issues done with infinity fabric..Rico Ismail said:They need to remove 32MB or 64MB (on two CCD) from expensive 5nm pricey silicon to cutting cost, place it on Infinity Fabric and/or Placing 3D stacked cache on top OF IOD. AMD usually go for right silicon on right usage, such 6nm for IOD, 7nm for stacked cache, fast and expensive 5nm on CPU Cores but not for large cache like L3.

Do you think every 7600X, 7700, or 7800X3D just only have one CCD? Although they only have 8 or 6 cores, sometimes they have two CCD on placed CHIP, but one of them are Not USED (Disabled). They Called this -- To maximize its production resources--. Source : https://www.tomshardware.com/news/amd-recycles-dual-chiplet-ryzen-7000-as-ryzen-5-7600x-cpus

So why not using CHEAP ONE CCD (without L3 cache) consist of 16 cores rather than disabling one expensive CCD consisct 32MB L3 cache on the 7600X or 7700X or 7800X3D? When using only ONE CCD, they will perform better on 12 and 16 cores since all cores is placed on same die