Intel's Patent Details Meteor Lake's 'Adamantine' L4 Cache

Intel's Adamantine L4 cache tile will rival AMD's 3D V-Cache tile.

Unofficial information that Intel's upcoming codenamed Meteor Lake processor is set to feature L4 cache has been floating around for some time now. Now, a new Intel patent found by VideoCardz indicates that Intel has prepped a codenamed Adamantine L4 cache tile that it may use for some CPUs. This IC could compete against AMD's 3D V-Cache in certain applications, but the chiplet will not be used solely as a performance booster.

Typically, caches serve to increase the performance of the memory subsystem by rapidly providing compute cores with necessary data. But there are other use cases too, as large caches can store a lot of data. The patent suggests that Intel's Adamantine (or ADM) cache can improve communication not only between the CPU and memory but also between the CPU and security controller. For example, the L4 can be used to improve boot optimization and even preserve data from caches at reset to improve loading times.

Windows 10 and Windows 11 loading times are fairly quick on Intel's platforms even today. But Intel believes that with memory available at reset, faster and more efficient BIOS solutions can be developed for modern devices like car infotainment systems and household robots. Automotive and robotic designs closely link SoC security with firmware phases, ensuring platform security. Failing to follow recommendations stops the platform from booting to the OS, thus reducing attack risks and protecting confidential blocks, which is crucial for cars and robots.

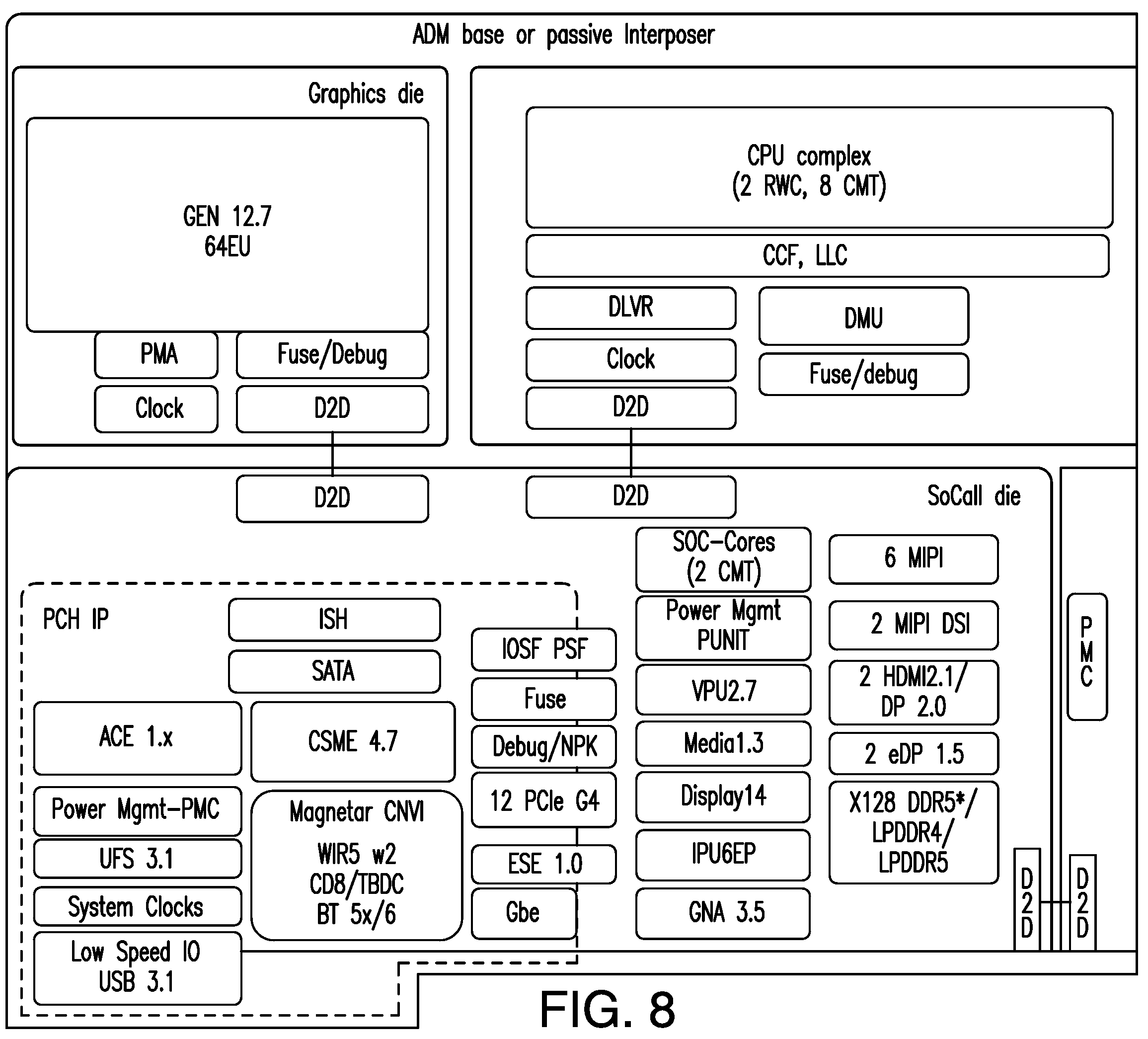

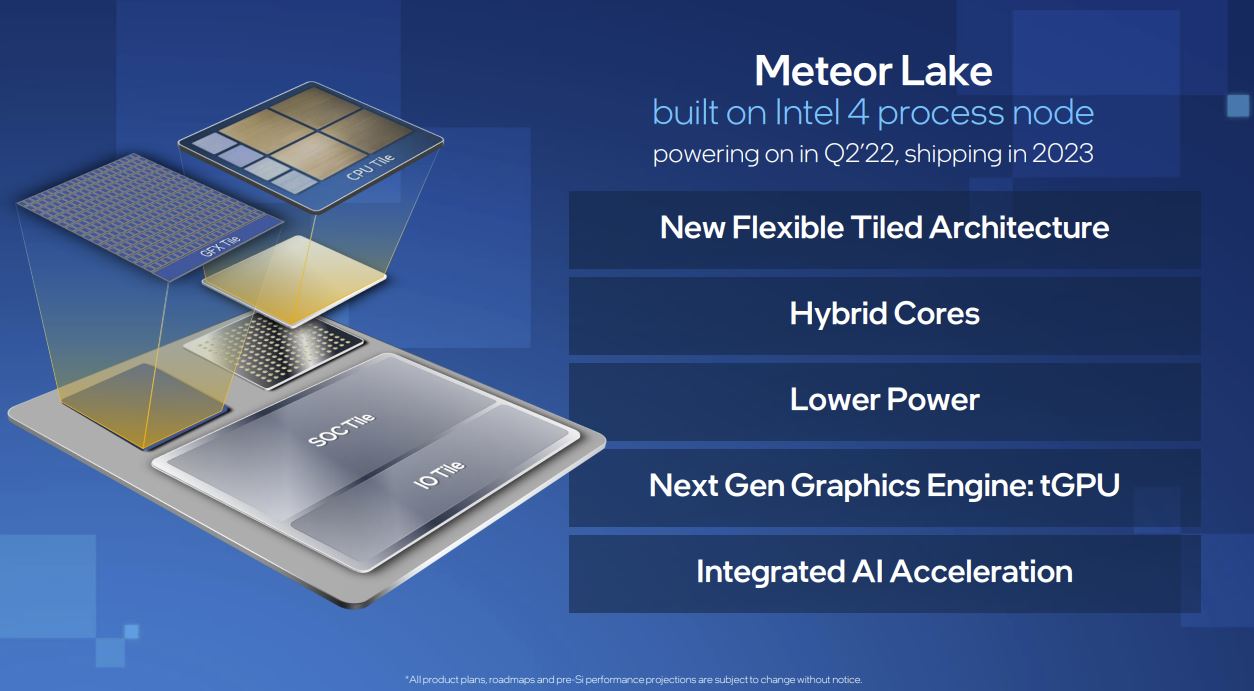

While the patent itself does not mention Meteor Lake, images supplied with it clearly demonstrate a processor with two high-performance Redwood Cove and eight energy-efficient Crestmont cores on one tile produced on Intel 4 fabrication process, a graphics chiplet based on Intel's Gen 12.7 architecture (Xe-LPG), an SoC tile containing two more Crestmont cores, and an I/O chiplet interconnected using Intel's Foveros 3D technology. The description corresponds to that of Intel's Meteor Lake processor. Meanwhile, the Adamantine L4 cache can be used for a wide array of applications beyond Meteor Lake.

Here is Intel's description of Adamantine:

Next generation client SoC architectures may introduce large on-package caches, which will allow novel usages. Access time for the L4 (e.g., "Adamantine" or "ADM") cache may be much less than the DRAM access time, which is used to improve host CPU and security controller communications. Embodiments help to protect innovations in boot optimization. Value is added for high end silicon with higher pre-initialized memory at reset, potentially leading to increased revenue. Having memory available at reset also helps to nullify legacy BIOS assumptions and make a faster and efficient BIOS solution with a reduced firmware stage (e.g., pre-CPU reset stage, IBBL stage and IBB stage) for modern device use cases like Automotive IVI (in-vehicle infotainment, e.g., turn on rear view camera within 2 sec), household and industrial robots, etc. Accordingly, new market segments may be available. [0059] Embodiments are able to tightly couple SoC key security recommendations with firmware mandatory phases (e.g., IBBL and/or IBB) specially enfolded with SoC provided at the silicon initialization binary (e.g., FSP-M) to ensure that the platform is always adhering to SoC recommendations. Failures to do so by skipping FSP-M will not permit the platform to boot to the OS. Such an approach eventually reduces the attack surface and provides passive way to protect confidential functional blocks (e.g., intellectual property blocks/IPs).

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

The new cache seems to be targeted primarily at the Arc Xe-LPG GPU which is featured on the graphics tile, one of the many tiles on Meteor Lake GPUs.Reply

To be utilized by the Meteor Lake-M and Meteor Lake-P chips which target the mobility platform. Intel Arc Xe-LPG GPUs will be the main beneficiary of the Adamantine L4 cache IMO.

Actually in some of the recent patches, as discovered by Phoronix (can't find the proper link now), it was revealed that, unlike the previous designs, Intel Meteor Lake GPU cannot utilize the LLC on the chip which was previously shared by both the CPU and GPU.

As such, the Adamantine L4 cache will play a huge role to assist the performance of Meteor Lake chips in graphics workloads.

But of course, Adamantine L4 cache can also be used by the Compute Title (CPU Cores), which are made up of Redwood Cove (P-Core) & Crestmont (E-Core) hybrid configurations, leading to faster boot times and overall lower latencies compared to moving data to the primary DRAM. -

Geef A lot of people here might not have been around back in the day when boot times were calculated in minutes not seconds but its already massively fast now even with just any SSD. Not really a need for faster booting.Reply

As long as that is not all it helps then a L4 cache can be good -

JayNor The patent application mentions configuring the L4 as SRAM, I believe for use by its aux E-cores during boot.Reply -

InvalidError Reply

Depends on the application. With the IoT thing still in close to full swing, there will be a growing number of toasters, ceiling fans, lights and other stuff running full-blown Linux, BSD and other OS derivatives for which you may not want to wait for a 5s boot time every time you turn them on before you can set them to do whatever it is you want them to do.Geef said:A lot of people here might not have been around back in the day when boot times were calculated in minutes not seconds but its already massively fast now even with just any SSD. Not really a need for faster booting.

I never cared about my PC's boot time since I usually only reboot my PC once every 2-3 months. -

Kamen Rider Blade The days of SRAM based L4 Cache are here.Reply

With Intel bringing their implementation on the way, you can bet that AMD will have their implementation.

It's going to be a great day when everybody starts using L4$ SRAM to benefit their CPU's =D -

InvalidError Reply

Almost every mention of L4 in the patent are specific to boot-time initialization, management engine, secure firmware, secure engines and related stuff while a couple more claims focus on IGP/UMA graphics. Doesn't look like it is intended for CPU usage while running software. At least not in its first iteration. They even mention a flag to disable or "lock down" the "L4" before BIOS passes control over to the OS at claim #93.Kamen Rider Blade said:The days of SRAM based L4 Cache are here.

With Intel bringing their implementation on the way, you can bet that AMD will have their implementation.

It's going to be a great day when everybody starts using L4$ SRAM to benefit their CPU's =D -

rluker5 I hate to cast doubt on something that looks good, but there does seem to be a possible use of some hybrid aggressive sleep function to save power on idle and low use. Maybe even shutting down extensive parts of the system if they could be woken quickly enough. That and the security stuff to make a cold boot like waking from sleep. Could lead to some nice, yet boring benefits in the power savings area.Reply

On low power mobile the benefit the iGPU would get is just not worth all of this silicon. (for example Xe > Broadwell iGPU. DDR5 has enough bandwidth for mobile stuff, you can see that with AMD's bigger iGPUs) Also without a dGPU the extra cache doesn't help that much.

For a low powered mobile part the extra cache for extra performance in things the chip won't be doing doesn't make much sense. Power savings does.

Some Arrow Lake or Lunar Lake desktop chip with faster P-cores and a 256MB L4 does sound pretty appealing though and if they have it in MTL, even if it isn't used the way I want, the manufacturing experience from making and using it will help reach the goal of using a large L4 properly. -

InvalidError Reply

The Crystal Lake eDRAM on Broadwell enabled massively improved integrated graphics performance (3-3.5X the performance for 2.4X the IGP size) and if Intel scales Meteor Lake's IGP is 128 EUs just like the A380, it'll certainly benefit from having access to a large scratchpad to offset having half as much memory bandwidth to share with the CPU.rluker5 said:On low power mobile the benefit the iGPU would get is just not worth all of this silicon. (for example Xe > Broadwell iGPU. DDR5 has enough bandwidth for mobile stuff, you can see that with AMD's bigger iGPUs) Also without a dGPU the extra cache doesn't help that much. -

bit_user OMG, that diagram is weird.Reply

The SoC die has 2 additional Crestmont cores, even though it's meant to be made on a larger process node!

The L4 cache die is off to the side of the SOC die, not directly connected to either the CPU or GPU tiles. I wonder if they at least put the tag RAM in the SoC tile.

This sentence strikes me as very odd:

"Value is added for high end silicon with higher pre-initialized memory at reset, potentially leading to increased revenue."

Do they literally mean "revenue" in the sense of better sales? Um, how exactly does "higher pre-initialized memory at reset" translate into that, and what does it have to do with the L4 cache?

Is this something to do with the boot phase before the DRAM controller is initialized? So, they want to rely on the L4 cache tile to hold the entire pre-boot firmware image, and that lets the offer better hardware security? -

bit_user Reply

https://www.phoronix.com/news/Linux-Patch-Intel-MTL-L4-CacheMetal Messiah. said:Actually in some of the recent patches, as discovered by Phoronix (can't find the proper link now), it was revealed that, unlike the previous designs, Intel Meteor Lake GPU cannot utilize the LLC on the chip which was previously shared by both the CPU and GPU.

I assume they're talking about the LLC of the CPU die.

I think there's a good chance that AMD will keep the GPU on its own Infinity Cache slice.Kamen Rider Blade said:With Intel bringing their implementation on the way, you can bet that AMD will have their implementation.

It's going to be a great day when everybody starts using L4$ SRAM to benefit their CPU's =D

That's an interesting point - they could power down the CPU tile and just run the Crestmont cores on the SoC tile. Likewise, they could power down the L4 tile - I know some phone SoCs power down parts of their cache hierarchy to save energy.rluker5 said:I hate to cast doubt on something that looks good, but there does seem to be a possible use of some hybrid aggressive sleep function to save power on idle and low use. Maybe even shutting down extensive parts of the system if they could be woken quickly enough. That and the security stuff to make a cold boot like waking from sleep. Could lead to some nice, yet boring benefits in the power savings area.

Disagree. A big part of Apple's power savings has been through more aggressive use of cache. When the system is running under high load, it's much more efficient to go to cache than DRAM.rluker5 said:On low power mobile the benefit the iGPU would get is just not worth all of this silicon. (for example Xe > Broadwell iGPU. DDR5 has enough bandwidth for mobile stuff, you can see that with AMD's bigger iGPUs) Also without a dGPU the extra cache doesn't help that much.

Also, I disagree on the bandwidth aspect, as iGPUs are famously bandwidth-limited. That's why AMD went from 11 CUs to 8, in more recent SoCs with Vega. If Intel is scaling up its iGPU past 96 EUs, then they'll need the additional bandwidth.