Intel 14th Gen Meteor Lake CPUs May Embrace An L4 Cache

It's no secret that Intel is preparing its 14th Generation Meteor Lake to rival the best CPUs. The chipmaker has already shared some feature sets for the upcoming Foveros-packaged chips. However, a new Linux patch implies that Meteor Lake will sport an L4 cache, which is infrequently used on processors.

The description from the Linux patch reads: "On MTL, GT can no longer allocate on LLC - only the CPU can. This, along with addition of support for ADM/L4 cache calls a MOCS/PAT table update."

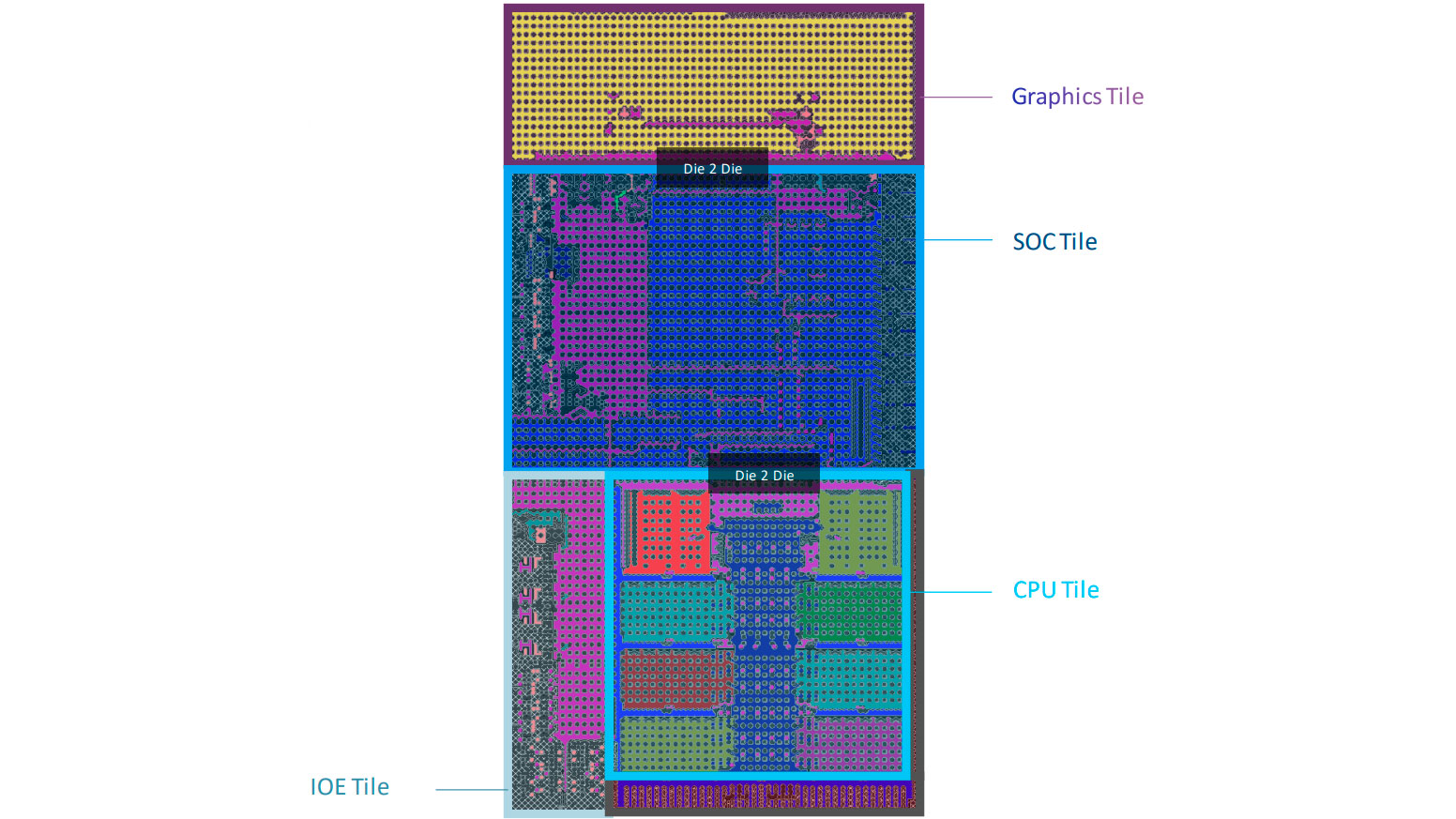

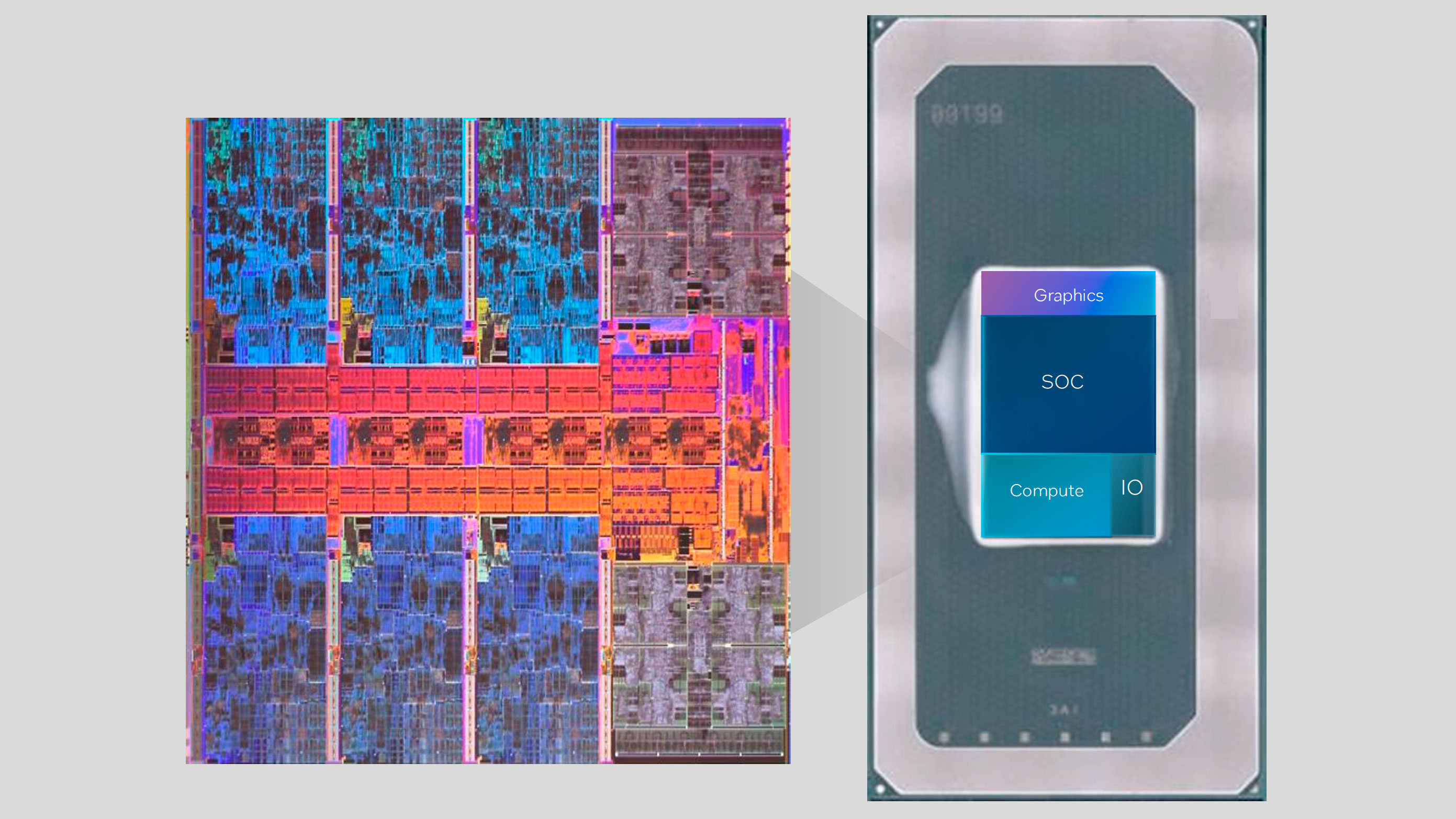

The patch didn't specify what "ADM" stands for. It could just be a fancy marketing name for the L4 cache. The code didn't expose the size of the ADM, either. Historically, Intel has used 64MB or 128MB for the eDRAM for Haswell through Coffee Lake. During its Hot Chips 34 presentation, Intel shared the schematics of the Meteor Lake chip, which comprises four different tiles: CPU tile, SoC tile, IO extender tile, and graphics tile. The quartet sits atop a large base tile that acts as an interposer.

Intel's first implementation of the eDRAM (embedded DRAM) was with Haswell and served as an L4 cache for the CPU and iGPU. The chipmaker would continue this practice until Coffee Lake. However, only a few selected desktop and mobile chips leveraged eDRAM over its short usage span. Broadwell was the most prominent architecture to feature eDRAM. Chipmakers typically shun the L4 cache from their designs because it's slower.

The cache hierarchy spans from L1 to L4, but most processors stop at L3 because speed decreases as you go down the ranks. Lower-level caches are larger and thus increasing the chances of a cache hit. The main problem is that accessing the lower caches, such as L3 or even L4 takes longer. So outside of feeding the integrated graphics, there are very few scenarios where the L4 cache helps in system performance. However, according to some Linux patches that Coelacanth's Dream has unearthed, the L4 cache could make a comeback with Meteor Lake.

The big question is where Intel will place the ADM/L4 cache. It's possible that Meteor Lake's base tile may house the L4 cache. For example, Ponte Vecchio's base tile carries 144MB of L2 cache, so there's precedent for it. Alternatively, the L4 cache may reside inside the SoC tile and would certainly explain its large landscape.

Another exciting discovery is that Intel has seemingly blocked Meteor Lake's iGPU from accessing the LLC (last level cache). As per the developer notes from the Linux patch, "On MTL, GT is no longer allocated on LLC, set has_llc=0."

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

LLC corresponds to the highest-numbered cache on the processor where it has to hit the memory. The L3 is typically the LLC in most modern processors, shared among the CPU cores and iGPU. For example, Intel's existing 13th Generation Raptor Lake chips arrive with up to 36MB of L3 cache, representing a 20% improvement over the last 12th Generation Alder Lake parts. However, the Linux patch states that only the CPU cores on Meteor Lake can tap into the LLC. The design is similar to AMD's Ryzen APUs, where CPU cores and iGPU don't share the same cache.

A 12-core Meteor Lake processor recently emerged on a benchmark website. Sadly, the chip's misreported clock speeds and results couldn't provide a concrete picture of how much performance uplift we can expect over Raptor Lake. So it's still unclear if Meteor Lake will stay mobile only, like Ice Lake or Tiger Lake, or whether it'll come to the desktop. On the other hand, there have been months-long rumors about a potential Raptor Lake Refresh, so the latter doesn't sound unlikely. An alleged Intel document only confirms that the marketing name for Meteor Lake is 14th Generation Core but doesn't exactly dispel the rumors.

Meteor Lake should hit the retail market in the second half of this year. After that, the 7nm chips will go up against some stiff competition from AMD, including Dragon Range (Zen 4 + RDNA 2), Phoenix (Zen 4 + RDNA 3), and the refreshed Rembrandt-R and Barcelo-R chips.

Zhiye Liu is a news editor, memory reviewer, and SSD tester at Tom’s Hardware. Although he loves everything that’s hardware, he has a soft spot for CPUs, GPUs, and RAM.

-

-Fran- Oh, if so, then they are definitely* preempting AMD and its VCache hitting the Laptop market.Reply

Interesting times ahead for Laptops!

Regards. -

JayNor ", Ponte Vecchio's base tile carries 144MB of L2 cache"Reply

each of the two base tiles... total 288MB SRAM on PVC in base tiles. see the Gomes presentation. -

Reply

Meteor Lake should hit the retail market in the second half of this year.

But only the MOBILE parts. Mobile chips might hit the retail first, since I think the desktop variants might even get canceled. Because we would rather get "Raptor Lake Refresh" as a stopgap before Meteor hits the market. MTL-S might get a 2024 release date, if Intel indeed has plans for a desktop variant, according to rumors.

FWIW, just recently Hardware Times actually shared what looks to be an official Intel slide that seems to confirm the whispers about Meteor Lake for desktops being canceled. The updated roadmap reveals that Intel might only be planning to launch Raptor Lake-S processors in 2023; all mentions of Meteor Lake seem to have been scrapped.

1606342626654896129View: https://twitter.com/OneRaichu/status/1606342626654896129 -

rluker5 It doesn't look like the old version of L4 to me.Reply

Those used a whole separate memory controller for the in package dram chip.

There were 2 concurrent controllers working and the combined latency was less than that of either.

Don't see another controller or a dram chip.

Maybe it is a big chunk of sram that can't be synced properly to work as L3. In this case it would be just a bit slower than regular L3.

And the application would be the same as the x3d, but without added thermal limitations. -

atomicWAR Reply

Exactly where my brain went too. Intuitive post as usual Fran. 😃-Fran- said:Oh, if so, then they are definitely* preempting AMD and its VCache hitting the Laptop market.

Interesting times ahead for Laptops!

Regards.

Its funny though now we're hitting sram scaling issues and cache has become the next big thing in processing with both Nvidia and AMD going all in with gpus and cpus in AMDs case... Now Intel is entering the fray. Interesting indeed. -

-Fran- Reply

Thanks!atomicWAR said:Exactly where my brain went too. Intuitive post as usual Fran. 😃

Its funny though now we're hitting sram scaling issues and cache has become the next big thing in processing with both Nvidia and AMD going all in with gpus and cpus in AMDs case... Now Intel is entering the fray. Interesting indeed.

I could add that, generally speaking, ML workloads benefit a lot with big cache sizes, so this may also be Intel experimenting with it on lower end product models?

Intel has put out some very interesting contraptions before, so they're no strangers to them, so this may well be a one-off model that got leaked or something.

That being said, I hope I'm wrong and we do get more cache on both camps for Laptops and other low power devices that could make good use of it; cough cough Steam Deck cough cough

Regards. -

bit_user Reply

L1 is special, because it's separated into code & data. I'm not exactly sure when that separation first came to x86 - maybe Pentium Pro? That's the first time I recall a x86 CPU having L2 cache, anyway.drtweak said:I remember when L2 was a new thing, then L3, and now L4? When L5 coming out? lol

L2 is usually single-core, but sometimes shared between a pair or quad of cores.

L3 is usually global, but I think the scope of AMD's L3 is limited to a single CCD chiplet, at least insofar as who writes it.

Beyond that, I think any further caching domain is either shared between multiple physical CPUs (IBM Z comes to mind, here) or between multiple IP blocks (e.g. CPU + NPU + iGPU) and sometimes called SLC (system-level cache). -

KyaraM Reply

L4 cache isn't exactly new, not even in consumer CPUs. Intel did that in the 4th generation iirc? Might have been fifth. Been a couple years in any case.drtweak said:I remember when L2 was a new thing, then L3, and now L4? When L5 coming out? lol -

bit_user Reply

The article does mention the eDRAM of certain Haswell & Broadwell SKUs. They also supported using the in-package HMC DRAM of Xeon Phi (KNL) as a cache. This is the first time I think they ever would be bringing L4 to truly mainstream models, however.KyaraM said:L4 cache isn't exactly new, not even in consumer CPUs. Intel did that in the 4th generation iirc? Might have been fifth. Been a couple years in any case.