PCI Express 7.0 Spec Targets 512 GB/s for x16 Slot in 2027

PCIe 7.0 version 0.3 is ready.

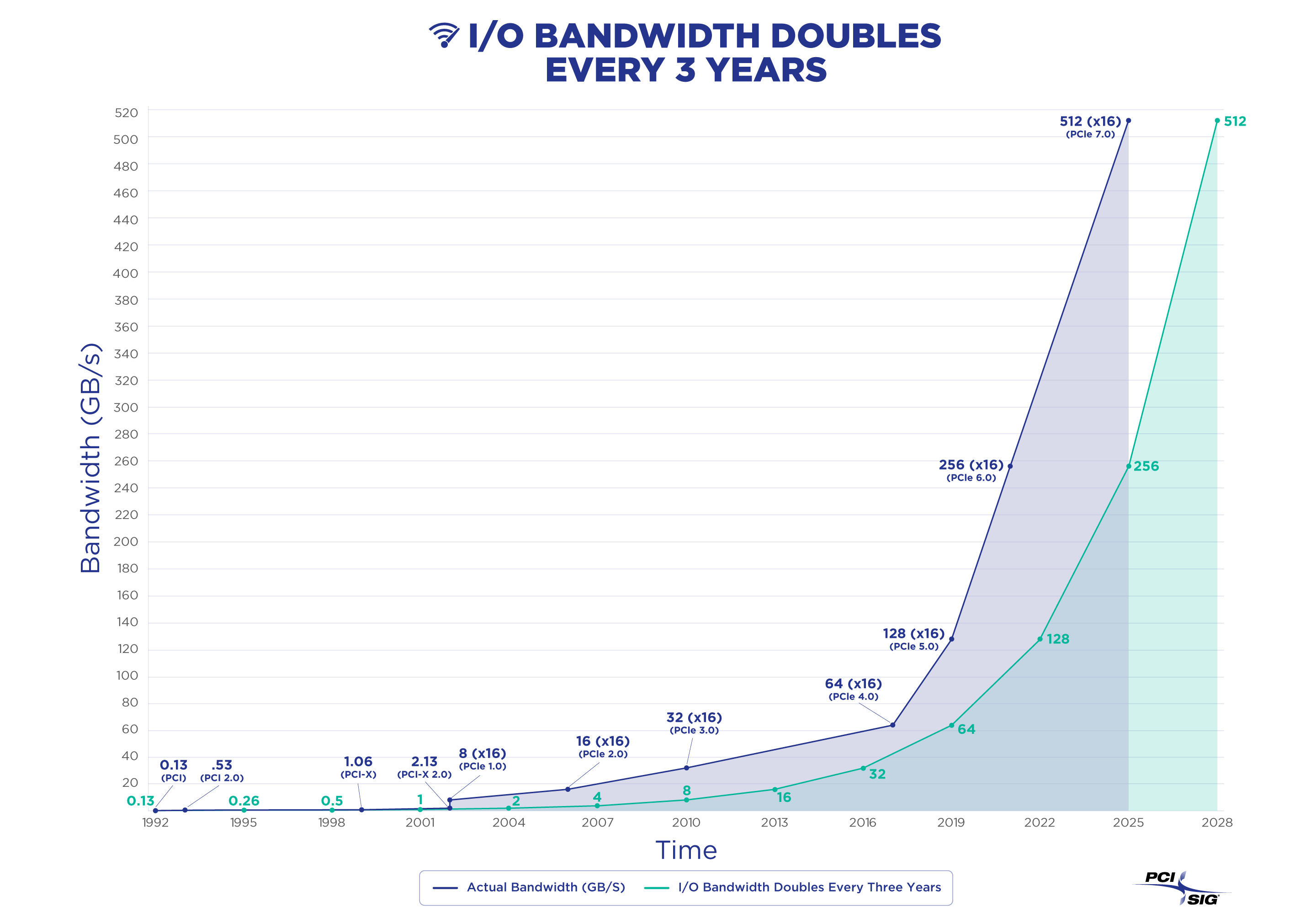

PCI-SIG on Tuesday published version 0.3 of the PCI Express 7.0 specification, marking a significant achievement for the technology that will increase the PCIe data transfer rate to 128 GT/s. This preliminary release indicates that members of the organization have agreed on the key features and architecture of the upcoming technology.

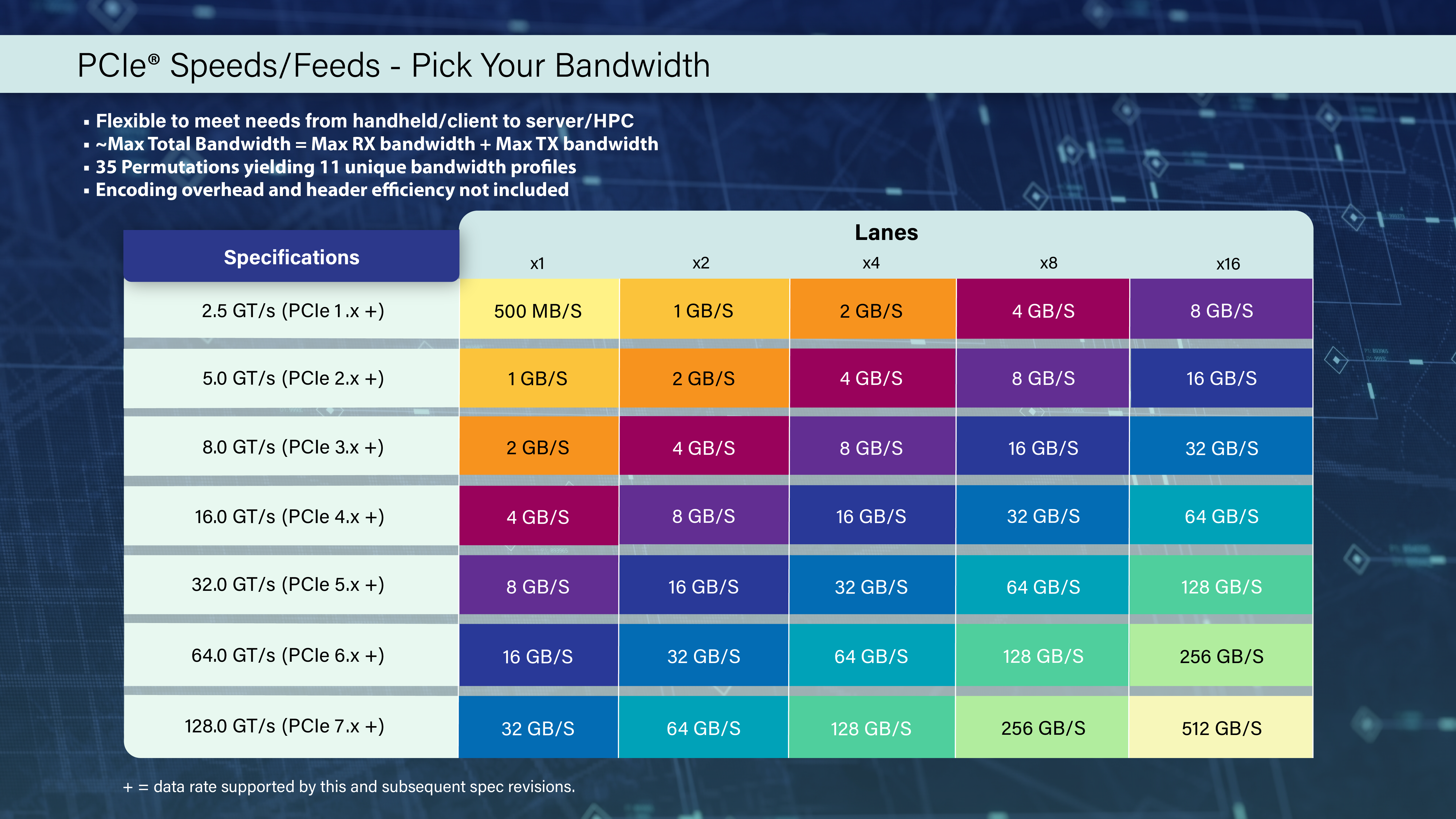

PCIe 7.0 is set to enhance the data transfer speed to 128 GT/s for each pin, substantially improving the 64 GT/s in PCIe 6.0 and the 32 GT/s in PCIe 5.0. This implies a 16-lane (x16) connection can support a bi-directional bandwidth of 512 GB/s before considering the encoding overhead. In a bid to increase data transfer rate and bandwidth, the PCIe Gen7 interface is set to use pulse amplitude modulation with four levels (PAM4) signaling, 1b/1b flit mode encoding, and forward error correction (FEC), which are features that the standard inherits from PCIe Gen6.

PCI-SIG has a very precise specification development process consisting of several releases/checkpoints. Version 0.3 typically lacks specifics, yet it provides an overview of the intended objectives and how to achieve them. Concerning PCIe 7.0, the primary targets include a data transfer rate of 128 GT/s and physical solutions that would ensure reliable and energy-efficient data transmission at this rate.

While we know the technology will rely on PAM4, flit mode, and FEC, specifics about PCIe Gen7 implementation look particularly interesting. The shift to PCIe 7.0, like previous transitions to PCIe 4.0 and 5.0, will necessitate shorter PCIe traces because of the increased signaling speeds. This will reduce the permissible distance between root and endpoint devices such as CPUs and expansion cards (graphics cards, accelerators, SSDs, network cards) without components like retimers. For now, we know that implementing PCIe Gen5 requires thicker PCBs and higher-quality materials, which means higher costs and prices. Yet, we have no idea about cost considerations for PCIe Gen7 in this regard.

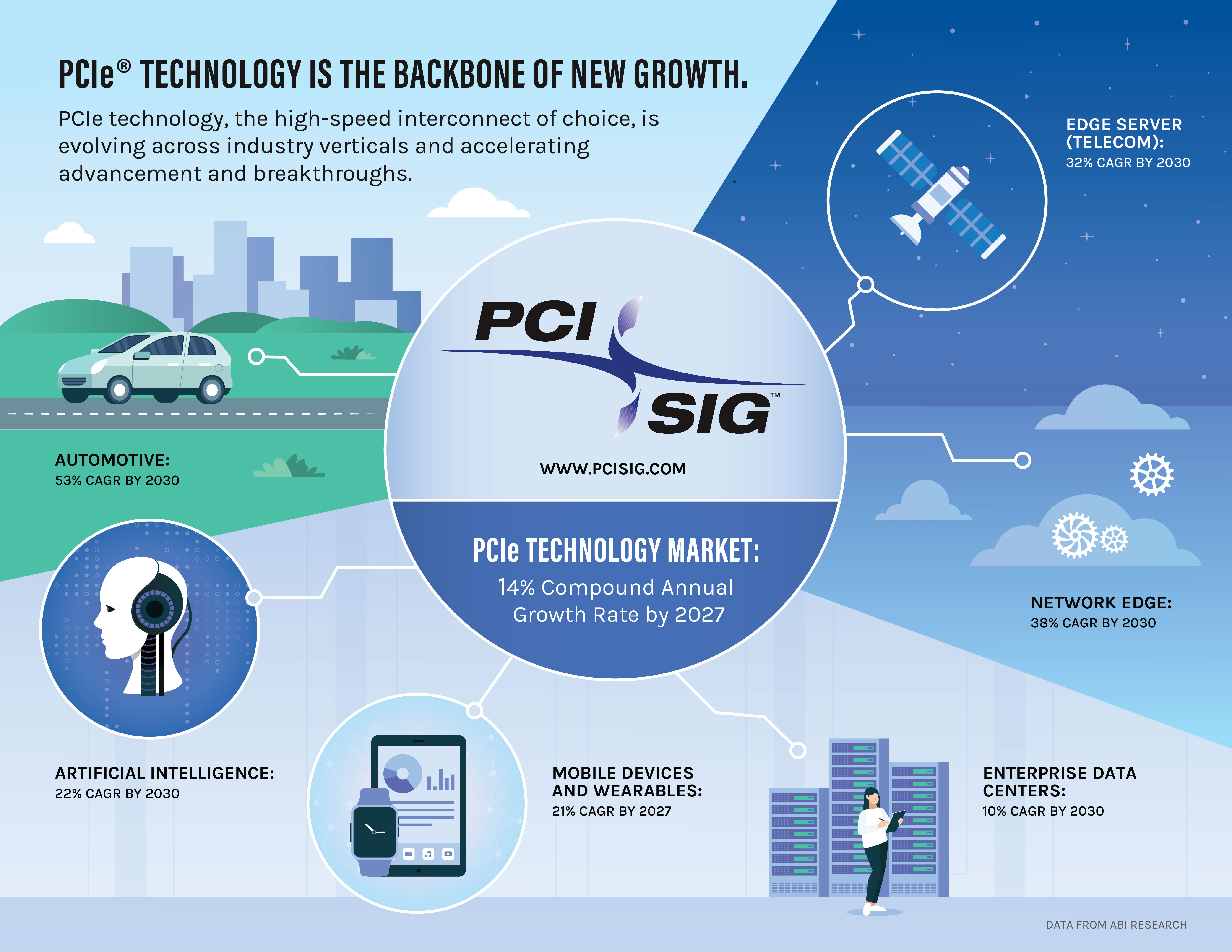

It should be noted that PCI-SIG itself clearly states that it is developing PCIe 7.0 to support such bandwidth-hungry applications as 800G Ethernet, AI/ML, cloud and quantum computing, hyperscale datacenters, HPC, edge, and aerospace/military. While we are sure that PCIe 7.0 will eventually end up in client PCs, PCI-SIG never mentions desktops or laptops.

"PCI Express technology leads the industry as a foundational I/O interconnect and can be found in everything from automobiles to data center servers," said PCI-SIG President Al Yanes. "As PCIe architecture speed increases, we will continue to expand our traditional verticals while expanding into exciting new verticals to meet the demand for a high-bandwidth, low-latency interconnect."

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

So based on the paper specs, even x1 PCIe 7.0 lane will be as fast as PCIe 4.0 x16 speeds (32 GB/s), so that most of the storage and other devices could be smaller and hog fewer resources.Reply

Or, we could have four NVME SSD drive slots with each using just 1 PCIe lane, and all of them would be twice as fast as a PCIe5 x4 NVMe slot. :smiley: -

peachpuff Can pci-sig take ethernet under its belt? We've been on 1gbps ports for two decades 😵💫Reply -

InvalidError Reply

I doubt that stuff is going to make it to the consumer space, at least not in AIB format. 128Gbps per pin is going to take some deep voodoo to get to work through board-to-board/chip sockets. It may get into the prosumer space and possibly get used as the off-the-shelf link between chiplets/tiles/whatever on multi-chip packages in the consumer space.Metal Messiah. said:So based on the paper specs, even x1 PCIe 7.0 lane will be as fast as PCIe 4.0 x16 speeds (32 GB/s), so that most of the storage and other devices could be smaller and hog fewer resources.

The TDP on the first few generations of these things is going to be brutal if the fist-gen 3.0-to-4.0 and 4.0-to-5.0 step as it currently stands are anything to go by. -

bit_user Reply

No, it's just an 8:1 ratio (2^3). If you look closely, you can see that each generation roughly doubles the previous one.Metal Messiah. said:So based on the paper specs, even x1 PCIe 7.0 lane will be as fast as PCIe 4.0 x16 speeds (32 GB/s),

I think what's confusing you is that they previously (?) specified unidirectional bandwidth and now they're summing them. I don't know why the change, unless it's to compete with Nvidia's messaging around NVLink, for instance.

It's rubbish, though. Because many I/O applications are asymmetrical in their bandwidth. For instance, games are overwhelmingly biased in the direction of sending data to the graphics card.

Look closely at the top of this chart:

My reference point has long been: PCIe 3.0 x1 = ~1 GB/s. Then, just double or halve your way from that. -

bit_user ReplyWhile we are sure that PCIe 7.0 will eventually end up in client PCs ...

I wouldn't be.

We saw backlash at the price increases of new motherboards, when Intel and AMD introduced PCIe 5.0 support. Given that PCIe 5.0 is still overkill for desktop PCs, I can't imagine Intel or AMD would want to go through another round of such complaints, for a feature with virtually no practical benefits to end users.

BTW, this is just a rehashing of what they already published an entire year ago:

https://www.businesswire.com/news/home/20220621005137/en

The press release they put out today was about "PCIe Technology TAM Expected to Reach $10 Billion by 2027", and only mentions PCIe 7.0 in passing.

https://www.businesswire.com/news/home/53418150/en

There's no actual news about PCIe 7.0, today. You've been click-baited. -

InvalidError Reply

There may be a benefit for the top-3%, though I doubt anything after 5.0 will go very far into the mainstream beyond the CPU-chipset link where the extra bandwidth could be necessary to feed downstream 5.0 devices with minimal uplink contention.bit_user said:Given that PCIe 5.0 is still overkill for desktop PCs, I can't imagine Intel or AMD would want to go through another round of such complaints, for a feature with virtually no practical benefits to end users.

I'm just impressed that they've managed to push a ~25 years old physical spec to from 1.3GHz to 60+GHz and get that to work reliably enough to be practical. That deep into microwave territory, signal integrity through the connector would likely benefit from a new interface with 2-3X the data pin pitch density. -

hotaru251 tbh for normal users this seems like just to increase price of MB's.Reply

even best gpu/ssd cant saturate 5.0 -

bit_user Reply

There are still no GPUs with PCIe 5.0 (not that I care - they don't need it).InvalidError said:There may be a benefit for the top-3%,

Yes, we finally got some PCIe 5.0 SSDs, in recent months, but they're hot, have enormous heatsinks, and I remain to be convinced they deliver user-perceivable benefits over fast PCIe 4.0 drives.

The irony of ironies is that one place where PCIe 5.0 could've actually delivered real value isn't something either Intel or AMD used it for!InvalidError said:I doubt anything after 5.0 will go very far into the mainstream beyond the CPU-chipset link where the extra bandwidth could be necessary to feed downstream 5.0 devices with minimal uplink contention.

Let's save the fanfare until PCIe 7.0 is finalized.InvalidError said:I'm just impressed that they've managed to push a ~25 years old physical spec to from 1.3GHz to 60+GHz and get that to work reliably enough to be practical.

Regardless, I think we're pretty close to the crossover point for optical, as a system interconnect medium*.

* For servers. -

InvalidError Reply

You don't need to "saturate" it. All you need to have an IO bottleneck with macroscopically observable symptoms is a couple of things attempting to do large IO at the same time, causing latency spikes from queue length spikes. You may only need 1% of the bandwidth on average but you still feel the lag when everything happens everywhere all at once every few seconds. The more spare bandwidth you have, the less likely that worst-case scenario is to happen and the less severe it gets.hotaru251 said:tbh for normal users this seems like just to increase price of MB's.

even best gpu/ssd cant saturate 5.0

To which I'll respond with the same thing as always: low-end GPUs stand to benefit the most from fast PCIe to give them faster access to system memory and offset their limited local memory pool. Ironically, GPU manufacturers won't give budget buyers that either.bit_user said:There are still no GPUs with PCIe 5.0 (not that I care - they don't need it). -

deesider Reply

I look forward to seeing optical lanes integrated into motherboards. There must be a point where it becomes cheaper than maintaining the integrity of so many tightly packed copper lanes.bit_user said:There are still no GPUs with PCIe 5.0 (not that I care - they don't need it).

Yes, we finally got some PCIe 5.0 SSDs, in recent months, but they're hot, have enormous heatsinks, and I remain to be convinced they deliver user-perceivable benefits over fast PCIe 4.0 drives.

The irony of ironies is that one place where PCIe 5.0 could've actually delivered real value isn't something either Intel or AMD used it for!

Let's save the fanfare until PCIe 7.0 is finalized.

Regardless, I think we're pretty close to the crossover point for optical, as a system interconnect medium*.

* For servers.