High-Density DDR3: Five Dual-Module 8GB Kits Compared

What Took So Long?

Power users have been maximizing memory almost since the beginning of personal computing, often attempting to make workstation-class programs run as well on home computers as they do on lab machines. Memory manufacturers gladly filled demand by producing non-ECC memory at server-sized capacities, easily reaching the 1GB per module capacity limit of DDR1 many years ago. That 1GB limit became the baseline for high-capacity DDR2 modules almost immediately after compatible platforms launched, and that technology’s 4GB per module limit was reached within a few years. With the trend set, many of us expected 4GB DDR3 performance modules to hit the market way back in 2007 and the maximum 16GB capacity to be reached soon. However, DDR3 capacities didn’t follow former trends.

We could speculate about how demand for increased capacities might have dropped off as user expectations reached a plateau with 1080p animations or 12 megapixel images, but that still doesn’t explain why, for nearly two years, DDR2 was the only option for most users who wanted really high memory capacities in their PCs. DDR3 users were forced to use four modules (dual-channel) or six modules (triple channel) to reach 8GB and 12GB capacities, and anyone who wanted 16GB or more had to wait over a year for the release of super-expensive 4GB DIMMs. Even as 4GB DDR3 modules for notebooks became common, desktop DDR3 users faced the fear of paying eight times as much to double their memory capacity.

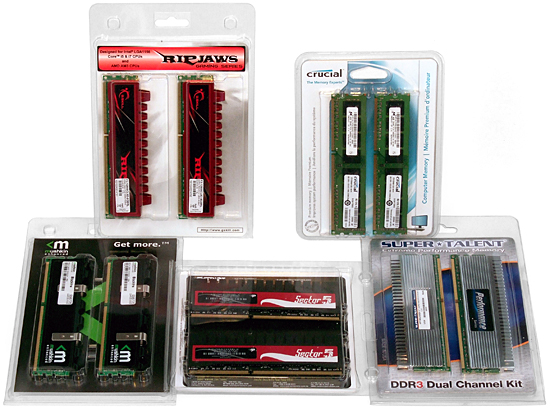

The breakthrough came late last fall, when G.Skill introduced several high-density kits priced “only” four times as high as similar parts half the size. Other manufacturers gradually followed, and today we finally have several 8GB two-module kits that most high-end builders can afford.

Rated at CAS 9 and priced between $400 and $500, manufacturer-approved data rates of 1,333 and 1,600 MHz appear to be the only noticeable difference between these modules. Curious to find the highest-performance parts within this budget range, we tested each set to find out the true limits of its stability, both at lower-latency and higher-frequency settings.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

-

liquidsnake718 At an average of $200 dollars a stick I can safely say I am not an "Enthusiast" even though I love computers, hardware, consoles, games, and talking about computers.Reply

However my next build has almost been conceptualized (waiting for certain parts and prices), so DDR3 here I come.

-

falchard Its about twice as much as getting 8GB off 2GB Modules. So the price increase isn't too bad considering 4GB ram sticks are the largest you can currently buy. I am still waiting for that to dip in price and for the more massive ram sticks to come along. We have been max 4GB for quite some time now.Reply -

arkadi 4 now i can live with 12gb limit on my x58 mb. But it is good to know that ppl that really need more then that can do it for affordable priceReply -

Only problem I have with the review is where is the same tests on a AMD platform for all us AMD users that will be or are already looking at AMD AM3/DDR3 builds.Reply

-

Crashman micky_lundouch 400+ for 8gb ram?Reply

Yeh, ouch, but can you imagine paying $800 for it last summer? Newegg still has one of those super-expensive kits. -

verrul dont expect more than 4gb anytime soon there really is no need in a system to run more than 4 to begin with you really dont see any speed improvements past 4 and no program is built to handle that size of memory block currently. Sure there are the occasional special systems that use more than 4gb but not for a single program. Besides that there is the TDP and FCC inforced efficiency ratings they have to come in under ram is an energy hog for an overclockerReply -

Crashman terrybearOnly problem I have with the review is where is the same tests on a AMD platform for all us AMD users that will be or are already looking at AMD AM3/DDR3 builds.Reply

Tom's Hardware has recently been getting very similar overclocking and timing results between AMD and Intel systems when using the same modules and DIMM voltage. That's why the high-end system for the last two System Builder Marathons used the same RAM both times. -

anamaniac What about 16GBm 1066MHz DDR3 DIMM's? Only $1,700 a piece. =DReply

Granted, however, it is server ECC memory, and was never designed to be in a desktop. (Would love a 2P rig running dual 4GHz sexacore Gulftowns with HT, with 9 DIMM's per socket, running (18 DIMMs x 16GB/DIMM) 288GB of RAM.)

http://www.amazon.com/HP-Memory-240-pin-PC3-8500-registered/dp/B002I8SHK2