Larrabee: Intel's New GPU

Fast Communication: The Ring Bus

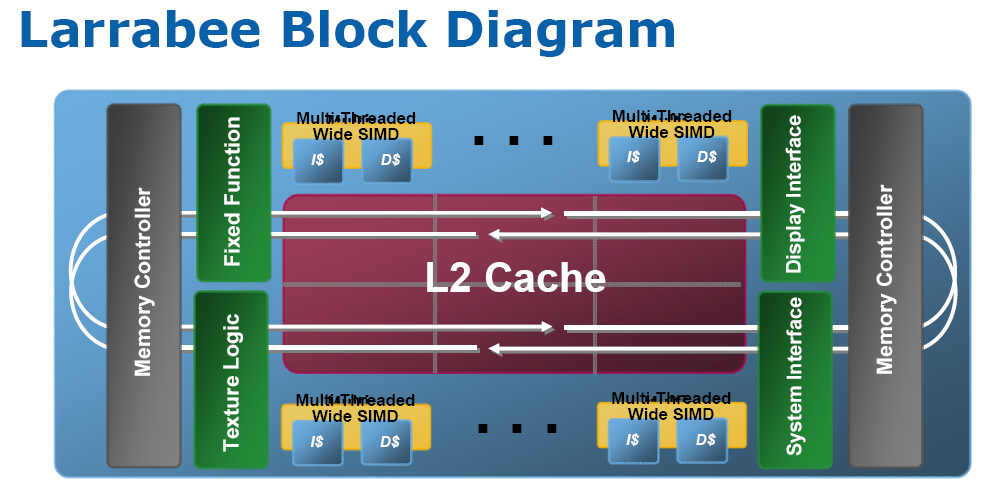

To manage cache coherence, communication between the different processors, and access to fixed units like the texture units, Intel has designed a fairly classic ring bus. This type of topology has become rather familiar recently, in the Cell processor and in certain AMD GPUs (X1800, X1900, etc.), for example, since it greatly simplifies the system of interconnections when the amount of data in the bus gets increases.

Intel has given Larrabee two 512-bit buses, one in each direction, to limit communication latency. However, that solution isn’t sufficient to avoid latency reaching problematic levels when the number of processors increases beyond a certain point, and so in Larrabee implementations using more than 16 cores, there are several, shorter ring buses (probably serving eight cores only).

We might point out in passing that Intel’s diagram of Larrabee is not quite exact. To avoid needless complication, Intel has put the memory controllers on either side of the chip, and all the texture units at the left. In practice, the texture units and memory controllers will be distributed around the periphery of the ring, rather then being all in the same place. Obviously, that’s to avoid problems with congestion with a configuration like the one shown in the diagram.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: Fast Communication: The Ring Bus

Prev Page The Vector Unit And Mask Register Next Page The Texture Units-

thepinkpanther very interesting, i know nvidia cant settle for being the second best. As always its good for the consumer.Reply -

IzzyCraft Yes interesting, but intel already makes like 50% of every gpu i rather not see them take more market share and push nvidia and amd out although i doubt it unless they can make a real performer, which i have no doubt on paper they can but with drivers etc i doubt it.Reply -

Alien_959 Very interesting, finally some more information about Intel upcoming "GPU".Reply

But as I sad before here if the drivers aren't good, even the best hardware design is for nothing. I hope Intel invests more on to the software side of things and will be nice to have a third player. -

crisisavatar cool ill wait for windows 7 for my next build and hope to see some directx 11 and openGL3 support by then.Reply -

Stardude82 Maybe there is more than a little commonality with the Atom CPUs: in-order execution, hyper threading, low power/small foot print.Reply

Does the duo-core NV330 have the same sort of ring architecture? -

"Simultaneous Multithreading (SMT). This technology has just made a comeback in Intel architectures with the Core i7, and is built into the Larrabee processors."Reply

just thought i'd point out that with the current amd vs intel fight..if intel takes away the x86 licence amd will take its multithreading and ht tech back leaving intel without a cpu and a useless gpu -

liemfukliang Driver. If Intel made driver as bad as Intel Extreme than event if Intel can make faster and cheaper GPU it will be useless.Reply -

phantom93 Damn, hoped there would be some pictures :(. Looks interesting, I didn't read the full article but I hope it is cheaper so some of my friends with reg desktps can join in some Orginal Hardcore PC Gaming XD.Reply