Intel's 12-Core Xeon With 30 MB Of L3: The New Mac Pro's CPU?

Results: Synthetics

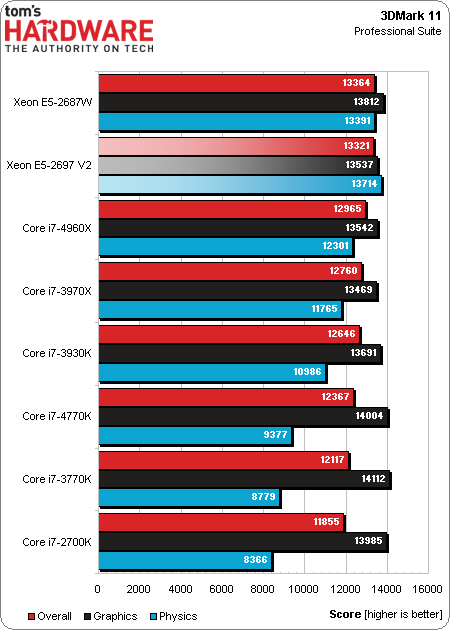

It goes without saying that a 12-core CPU isn’t necessary for gaming. Indeed, when it comes to 3DMark’s Graphics component, the quad-core Sandy Bridge, Ivy Bridge, and Haswell processors are all faster than Intel’s upcoming Xeon E5.

However, the physics test spawns threads for physical and logical cores. Despite its lower clock rate and thermal ceiling, the Xeon E5-2697 V2 pulls down the highest Physics score.

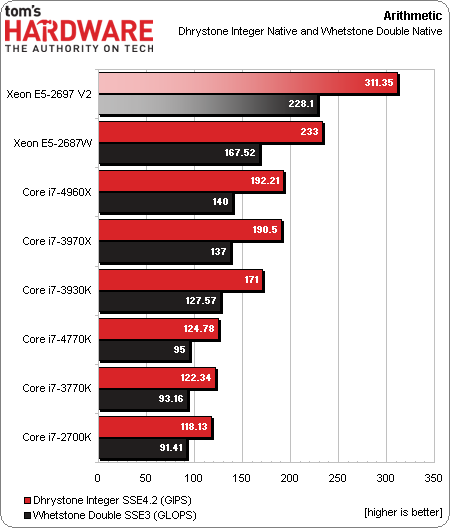

The Core i7-4960X sports the same core configuration as its predecessor. Moreover, the Ivy Bridge architecture didn’t incorporate any instruction set extensions beyond Sandy Bridge’s design. Consequently, the -4960X doesn’t demonstrate any more alacrity in Sandra’s Arithmetic module. The eight-core Sandy Bridge-EP and 12-core Ivy Bridge-EP processors, on the other hand, are quite a bit faster in this synthetic metric.

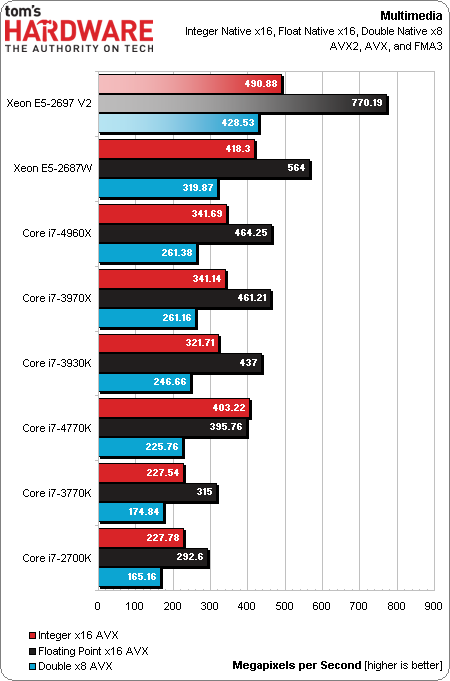

Article continues belowThe same applies to Sandra’s Multimedia test. Intel’s Haswell architecture fares well in the integer component thanks to its AVX2 support, even outperforming Core i7-4960X. However, more on-die resources give Intel’s eight- and 12-core CPUs an advantage. The floating-point tests are outright rocked by both of the Xeon processors.

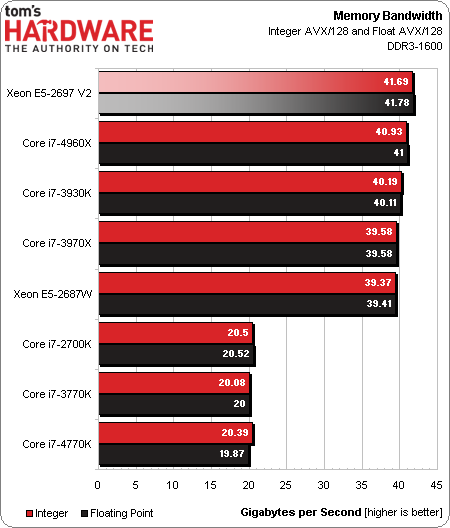

As with Ivy Bridge-E, Ivy Bridge-EP supports four channels of DDR3-1866 memory. There’s a bit of difference between the quad-channel configurations. But, in essence, you’re seeing the high-end platforms doubling the dual-channel mainstream systems.

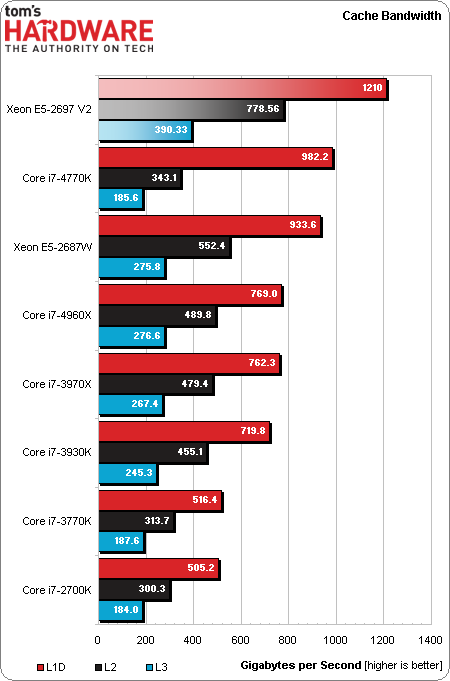

Intel’s Core i7-4770K came close, but we now have our first L1 data cache bandwidth result in excess of 1 TB/s. Of course, the Haswell architecture achieves its result through a doubling of L1 throughput compared to Ivy Bridge (this checks out; compare the Core i7-3770K).

The eight-core Sandy Bridge-EP-based Xeon E5-2687W comes close to matching Core i7-4770K by leveraging twice as many cores in this aggregate metric. Ivy Bridge-EP surpasses it with another four cores. Just imagine what a Haswell-based implementation could do!

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

L2 cache bandwidth aggregates as well, which is why Sandra measures almost 800 GB/s across all 12 cores. L3 is of course shared between the cores, though additional stops on the ring bus contribute to greater throughput in this case, too.

-

jimmysmitty Reply11342601 said:The 32-bit build of Geekbench uses x87 code

Typo, top of page two.

Where is the typo? Do you mean the x87? That's not a typo.

This is interesting but not uncommon. The server market needs the boosts while most consumer desktop CPUs are already faster than most software can go.

Of course in 5 years a SB i5 will be no longer relevant but until then it will serve just fine. Even a x58 i7 is still a viable option for a CPU and its been out for at least 4 years. -

vmem Interesting article. Must admit though, while the Mac Pro's performance is certainly impressive, the overall pace of development in the high-end has been rather boring for the past 2 years. can't wait to see what Haswell-E can do late next year.Reply

"Regardless of whether you love or hate the “wastebasket” design, the system’s specs are very impressive for the volume of space it occupies."

And this remark touches on the core of the problem. these are a specialized, niche market of professionals who're buying this uber-expensive desktop for PRODUCTIVITY. sure it should look nice, especially in the office of a professional designer. but must it be SMALL? honestly, build a giant aluminum bookshelf if you have to. make it look elegant and artistic, maybe give people some power to customize it's looks, but ultimately give people the ability to customize the machine and buy the level of productivity they need. Apple, you've done some great things, as well as some things that I don't particularly like. but watching you kill the freedom of the small group of designers who love your products is rather sad... -

Someone Somewhere Reply11342721 said:11342601 said:The 32-bit build of Geekbench uses x87 code

Typo, top of page two.

Where is the typo? Do you mean the x87? That's not a typo.

Hmm, on a quick Wikipedia read, x87 was the instruction set used for the floating point instruction sets in the 8087 and later FP co-processors. Interesting.

Oops... sorry. -

natoco In a years time with the haswell refresh and series 9 chipset it will still make everyone yawn even if it was this year. Everything has been going into mobile since Nehalem. On the bright side, phones and tablets will start slowing down very soon once they too reach the same manufacturing node as enthusiast pc's, since the node determines the power envelope achievable, thus mobile is about to hit the same wall.Reply -

CommentariesAnd More What I expected for the Mac Pro's CPU was a different CPU optimized for the Mac Pro. Would be surprised if the temps of made by this 12Core beast keep things cool. But hey , this isn't final , right ? Lets hope for the best ( and an affordable Mac Pro :) )Reply -

PreferLinux http://www.mouser.com/ProductDetail/Intel/CM8063501288843S-R171/?qs=sGAEpiMZZMvqxsBVy5ZiuowErqth9imUwPY6%2fY0Um1w%3dReply

Guess what?

"Description: CPU - Central Processing Units Xeon E5-2697v2 12 CR 2.7GHz FCLGA2011"

"Pricing (USD)

1: $3,249.19

2: $3,127.04" -

Someone Somewhere Reply11343328 said:What I expected for the Mac Pro's CPU was a different CPU optimized for the Mac Pro. Would be surprised if the temps of made by this 12Core beast keep things cool. But hey , this isn't final , right ? Lets hope for the best ( and an affordable Mac Pro :) )

Nobody optimizes CPUs for anything. The set up costs are ridiculous. The closest you'll get is a custom config, like a chip with (for example) both multi-socket support and overclocking or something, but you'd have to show up to intel with a truck full of cash. -

Duckhunt as usual the folk running intel have become lazy and stupid and the developments in the desktop have gone down the hole. They just add some extra cache and extra threads and then act like they did something.Wow. ( at the stupidity).Reply

Instead of pushing out code or getting the rest of the industry to use more threading applications and develop it to make it more stable and useable. Nothing.

I guess when we have a third world america. You might as well go back to a decade 1368x738 with it being the most popular in 2006. Who can afford it? It the retro push backward.

-

Someone Somewhere Intel can't really do much about forcing the industry to use more threaded apps.Reply

Not their job to write code, other than drivers. They do make x86 Android though, because the drivers are pretty much hardcoded.

Do agree on the 1366x768 though. It's the same number of lines as XGA, just with a few pixels on the side. Maybe Intel should have forced a PPI measurement on Ultrabooks - that might have helped.