OCZ's HSDL: A New Storage Link For Super-Fast SSDs

SATA 6Gb/s not fast enough? OCZ's new High-Speed Data Link serves up to 2 GB/s through a PCIe-like connection. Complementing the interface technology is a similarly-new 3.5" SSD called IBIS. Rated for up to 120,000 IOPS, enthusiasts should take note.

OCZ’s High-Speed Data Link

OCZ isn’t doing anything particularly tricky with its HSDL interface. Everything happening under the hood is very standardized—and OCZ is very forthcoming in describing the foundation on which HSDL is based. HSDL employs the same 8b/10b encoding scheme as PCI Express, SATA, HyperTransport, and USB 3.0. And once PCI Express 3.0 catches on, HSDL will even accommodate the 128b/130b encoding that interface specifies.

For the most part, PCI Express is the center of HSDL’s world.

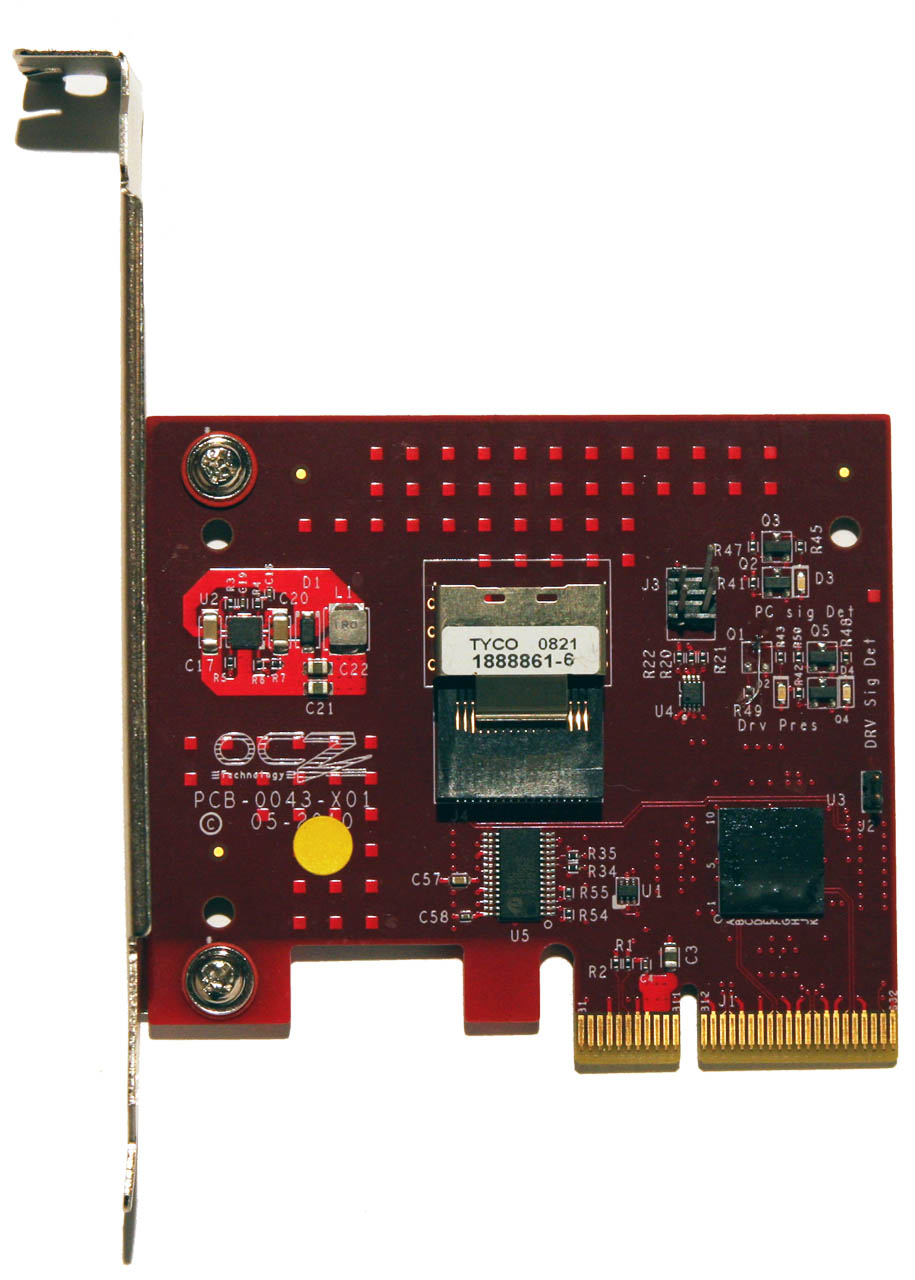

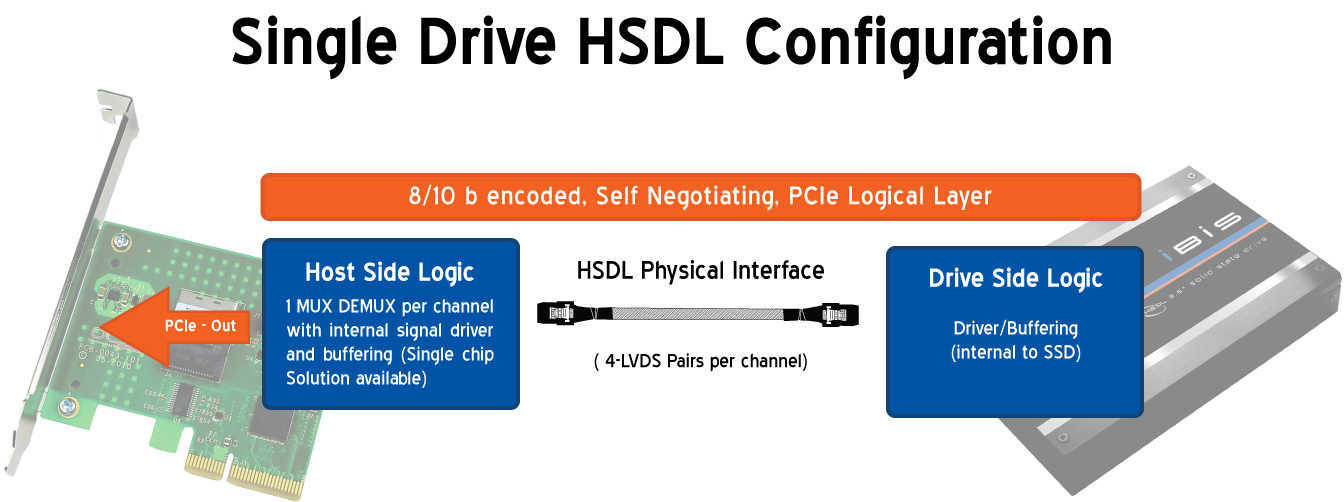

A single HSDL channel consists of four PCIe lanes bonded together, yielding predictable scaling. Right now, the company is offering its IBIS SSDs with single-channel adapter cards that (obviously) drop into a x4 motherboard slot. In the future, it plans to scale up to dual-channel cards that’ll drop into a PCIe x8 slot.

The math is easy. In a second-gen PCI Express x4 slot, HSDL serves up 2000 MB/s of throughput. In a x8 slot, a dual-channel card would push up to 4000 MB/s. Of course, the dual-channel card OCZ plans will also sport four ports, limiting cumulative throughput to roughly 1 GB/s per drive (still more bandwidth than a single first-gen drive can saturate).

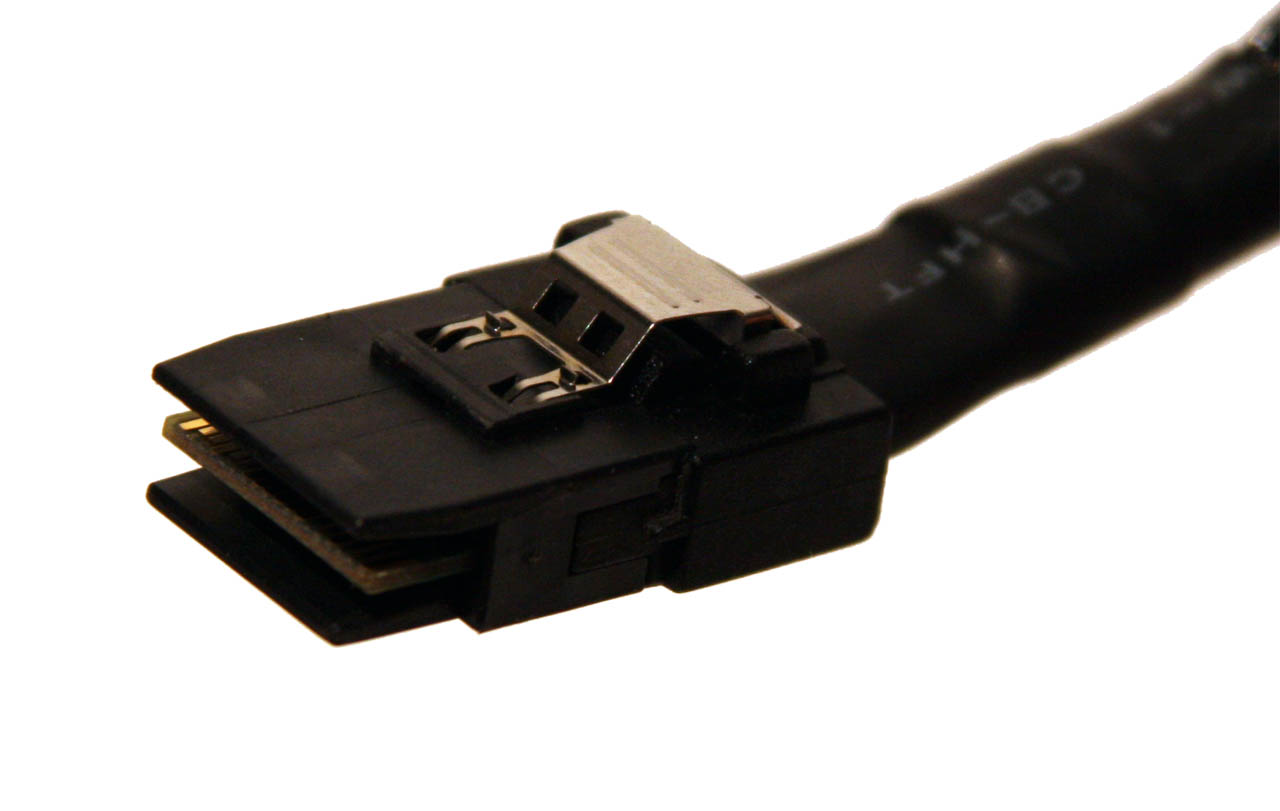

In between the controller and the drive, OCZ is using 4x SFF-8087 connectors. While it might seem a bit ironic to use SAS connectivity to outperform the SAS interface, OCZ says the four-channel connector gives it the number of LVDS pairs needed for HSDL. Each channel consists of four bi-directional pairs, correlating to the four bonded PCIe lanes.

The magic happens at each end of the cabled connection, where a logic chip serves as a signal driver and buffer. In the case of a dual-channel controller attached to a single drive, that piece of logic also multiplexes to create a single ultra-wide “PCIe x8” link. If you want to get a little more technical, OCZ is using the logical PCIe layer over the company’s own embedded physical layer. On the drive itself, you have a conversation chip that turns the SATA into a PCIe-type signal (Petersen specifies that it isn’t actually PCIe), which is serialized and re-buffered before getting sent out.

On the controller side, another chip serves as the basic physical protocol conversion to turn the physical layer into PCIe. Should a motherboard vendor wish to integrate HSDL support, it’d need the SAS connector and the conversion chip found on OCZ’s controller card—everything else is drive-focused. “The goal,” according to Petersen, “is to let motherboard vendors be able to implement HSDL at a five-dollar cost. If they can’t do it for less than $5, it’s a bad move for us to have the product.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Using this architecture, OCZ expects to see 500 MB/s per LVDS pair ramping up in the future. Of course, even with this first-generation implementation of the technology, HSDL is pretty much overkill—the performance of today’s controllers and NAND flash isn’t high enough to saturate a four-pair, 2 GB/s single-channel HSDL interface. OCZ’s Petersen teases that this will be addressed soon. With that said, the company expects today’s single-channel controller to handle the performance of first- and second-gen IBIS-style SSDs.

Three generations down the road, more throughput should start to become necessary (at least, that’s the game plan). When that happens, the company can start using standalone PCIe 3.0 transceivers and encoding chips (which are actually available right now) to adopt 128b/130b encoding, increasing throughput even more. There’s simply no need for that extra headroom today, given the available drive technology.

Current page: OCZ’s High-Speed Data Link

Prev Page The HSDL/IBIS One-Two Punch Next Page The IBIS SSD-

Randomacts *faints* I will never be able to afford these.Reply

Those HDDs cost more then my entire comptuer -

randomizer Chris I think I'll need to double-check your results. Better send the drive my way.Reply -

mianmian Optic link technology may be more exciting. Can't wait to see lightpeak or similar stuffs to become real.Reply -

First time saw those numbers, i gasped for air... OCZ, can you try to saturated with PCIe 2.0 x16 bandwidth? And can anyone tell me how much is it in Write and Read speeds at that bandwith?Reply

-

wribbs Very nice to see secondary storage tech at orders of magnitude beyond what we're used to. Can't wait for this type of tech to become mainstream.Reply -

compton Stuff like this makes me wish I was involved in an enterprise-class technology environment that could actually benefit from 130,000 IOPS in a package like this. I guess I don't need to ditch my Agility 60, but I like where OCZ is headed.Reply -

h8signingin Yet there are already drives that outperform these by a large margin available for a while now, like this:Reply

http://www.superbiiz.com/detail.php?name=RGS0256M&title=Super-Talent-RAIDDrive-GS-256GB-RAID0-PCI-Express-x8-Solid-State-Drive

Read 1.4GB/s, Write 1.2GB/s

At those speeds, it's like writing to RAM, only it's your hard drive.

There were also capacities up to 1TB that cost about $4,000. There were even SLC models (which cost 4x more, approx. $15,000) which are slightly faster still.

Personally, I wouldn't mind having 1TB of "slow" RAM as my hard drive, but it's just beyond my budget. -

cangelini h8signinginYet there are already drives that outperform these by a large margin available for a while now, like this:http://www.superbiiz.com/detail.ph tate-DriveRead 1.4GB/s, Write 1.2GB/sAt those speeds, it's like writing to RAM, only it's your hard drive.There were also capacities up to 1TB that cost about $4,000. There were even SLC models (which cost 4x more, approx. $15,000) which are slightly faster still.Personally, I wouldn't mind having 1TB of "slow" RAM as my hard drive, but it's just beyond my budget.Reply

Yup, check it out! =)

http://www.tomshardware.com/reviews/super-talent-raiddrive,2513.html