The OCZ Vertex 2 Conspiracy: Lost Space, Lost Speed?

Several readers contacted me in the past two weeks, complaining about OCZ's recent adoption of 25 nm NAND and its effect on the capacity and performance of certain SSDs that they expected to be both larger and faster. I bought my own drives to compare.

Benchmark Results: CrystalDiskMark Streaming Performance

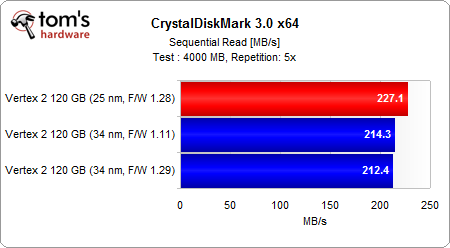

While not exact, CrystalDiskMark’s sequential read test comes close to confirming the results we got in Iometer using random data, going so far as to give the 25 nm NAND-based drive a small throughput advantage.

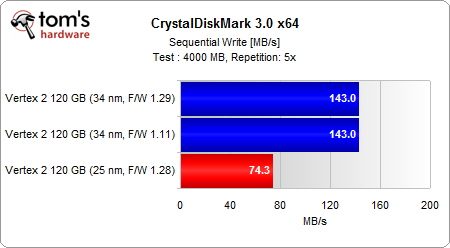

This very quickly evaporates when we start writing uncompressible random data to the two drives. And that, in a very easy-to-understand chart, is what the performance debate revolves around.

When it comes to optimization, SandForce’s architecture handles easily-compressible data best—we know this. On the previous page, you saw Iometer demonstrating even sequential read and write performance. That’s because our Iometer test isn’t using random data. It’s easily compressible. And from that angle, the 25 nm-based drives are exactly the same as their predecessors.

Present the drive with information that isn’t compressible and you end up with the chart above, though. OCZ’s contention is that this isn’t a representation of real-world data patterns. And while it’s easy enough to isolate one specific deficiency, translating to someone’s actual desktop shouldn’t impact actual performance. Keep this in mind once we hit the PCMark Vantage tests. OCZ isn't just trying to cover its butt here; there is some truth to its point.

Personally, I’d counter that this argument is a lot easier to make if we’re talking about dissimilar SKUs or generations of products. In the context of the OCZSSD2-2VTXE120G, a customer shouldn’t see that degree of performance variance between boxes taken off the shelf, even if the example is isolated.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: Benchmark Results: CrystalDiskMark Streaming Performance

Prev Page Benchmark Results: Iometer Streaming Next Page Benchmark Results: 4 KB and 512 KB Random Reads-

Mushkin.com have a letter posted on the website that they will not be going to 25nm as the drives life cycle is less than half that of a 3*nm drive. Also the performance is not there.Reply

-

cangelini LeekayMushkin.com have a letter posted on the website that they will not be going to 25nm as the drives life cycle is less than half that of a 3*nm drive. Also the performance is not there.Reply

Depending on supply of 34 nm NAND, that's probably not a sustainable position to take. IMFT isn't going to decide to shift back to 34 nm.

At the risk of contradicting myself, Intel will be using 34 nm NAND on its next-gen 6 Gb/s Elmcrest drives. It's not like the flash isn't disappearing entirely, but the vendors making the switch seem to be motivated largely by cost-cutting reasons. -

Nicely done Mr. Angelini; however, I still think OCZ pulled a nasty car-salesman tactic on their newest 25 nm NAND SSD products, and as such will be looking elsewhere to purchase any future SSD. Blaming resellers or other sources for the SKU is an incompetent way of deflecting fault and has made them look even more silly.Reply

-

cangelini Thanks radiovan. Like I mentioned in the story, we'll have to see if companies like Corsair and Patriot are able to get their upcoming renamed SKUs onto Newegg, Tigerdirect, Zipzoom, etc.Reply -

1.29 Firmware....how nice... pity that ocz only documents 1.28 for the moment.Reply

And then again why not update the 25nm to 1.29 too?

But I guess consistency is not always wished when trying to demonstrate something -

nebun binoyskiOk, but when will we be able to buy ssd's that are $100 @ 1TB capacity?in about 10 years or so....that's a very big maybeReply -

yose3 binoyskiOk, but when will we be able to buy ssd's that are $100 @ 1TB capacity?Reply

when you throw a shoes to bush again meaby lol

-

Reynod It is all about profit.Reply

The real reason is that going to cheaper flash with a 3000 cycle life to reduce the total cost of production (and therefore increase profit) means ... increasing the amount of redundant memory to replace the flash that dies due to wear ... and that process means better error correction is required to achieve that ... therefore performance is effected.

Chris ... I got it into one sentence ... albeit a horrible one.

Nice article mate.