Silicon Motion SM2256 Preview

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Four-Corner Performance Testing

Flash-based products pose more testing challenges than mechanical storage products. The workload you run before a test affects the results you see immediately after. In order to make true apples to apples comparisons between products, a strict benchmark regimen must be adhered to. With some products, the type of data used for testing, whether it's compressible or not, changes the performance story.

To read about our storage tests in-depth, please check out How We Test HDDs And SSDs. Four-Corner testing is covered on page six.

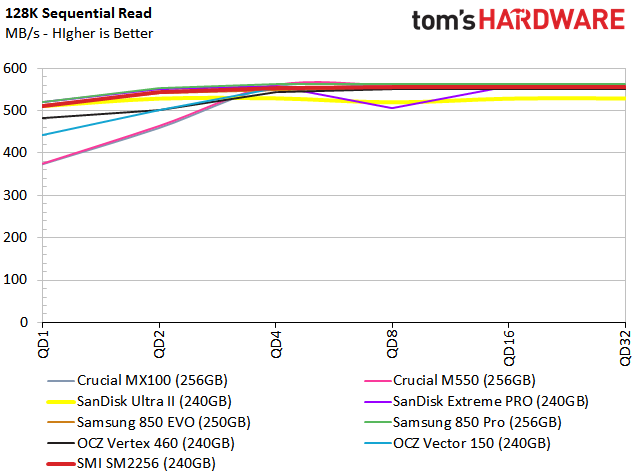

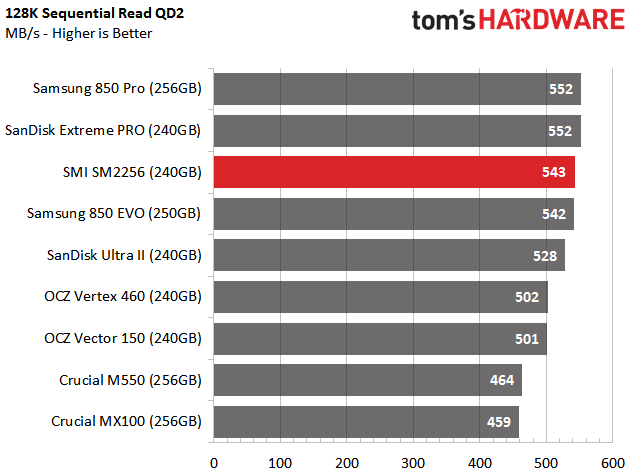

SMI's SM2256 hits the upper performance ceiling of SATA 6Gb/s surprisingly fast in our sequential read test. The SM2246 already used in several commercially available SSDs demonstrates the same high performance at low queue depths.

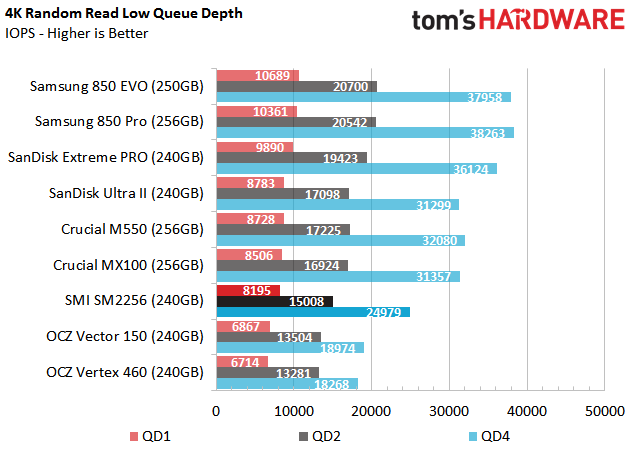

Article continues belowAt a queue depth of two, our SM2256 sample with Samsung flash falls slightly behind Samsung's own 850 Pro and SanDisk's Extreme Pro at the same capacity point.

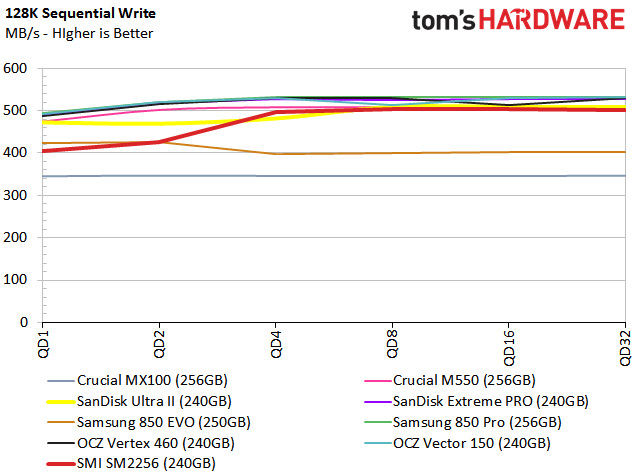

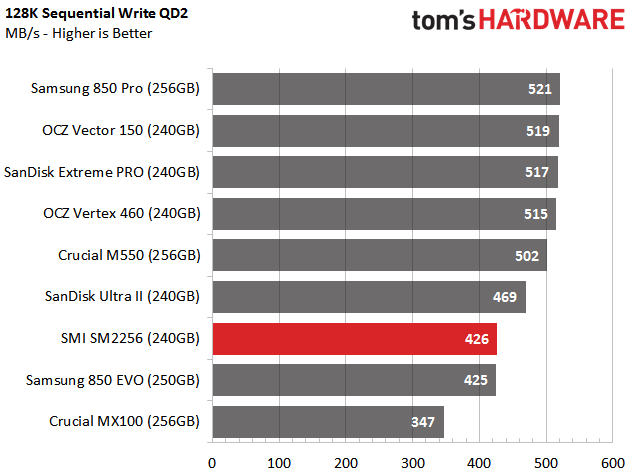

Going forward, the difference between value- and high-performance products will come down to write performance. Most companies already ship less expensive drives with 128Gb die, so each IC holds twice as much data as performance-oriented SSDs with lower-density flash. Why is this? The higher the die capacity, the fewer dies there are for parallelizing reads and writes. In short, the more dies you can write to at any given time, the faster that operation occurs.

The SM2256 is a four-channel controller, so it's already at a disadvantage compared to eight-channel designs. That's one reason we see this drive at the lower end of our sequential write test.

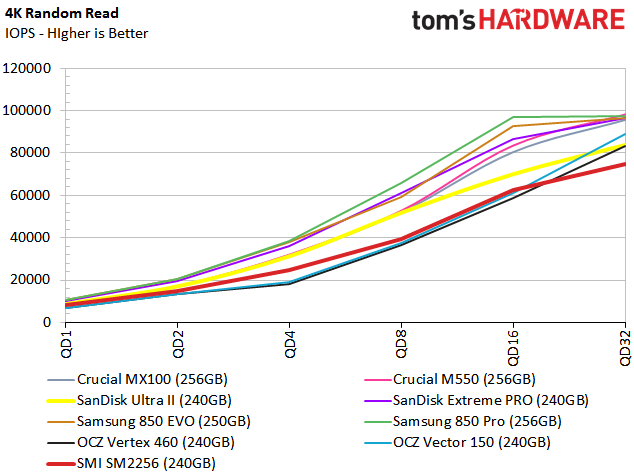

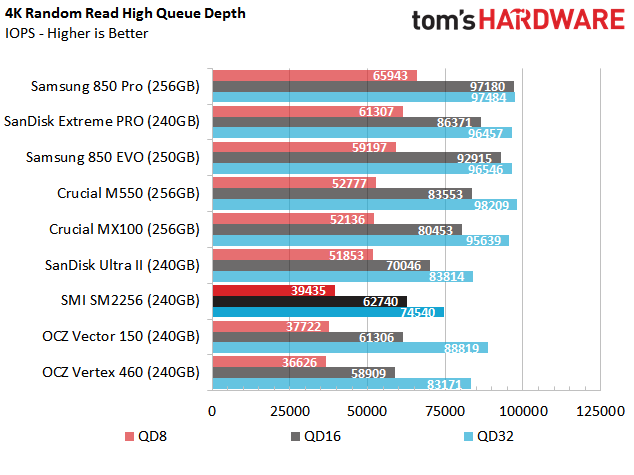

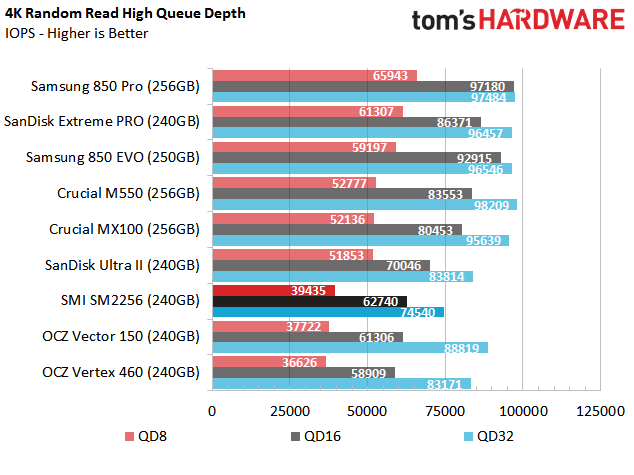

4KB Random Read Performance

The SM2256 ends up behind many of today's drives in measures of random read performance. What I'd really like to know is what will happen when read retries intensify towards the end of the drive's life cycle. Samsung 840 EVO owners are already dealing with these issues, despite the company's purported firmware fix. This is why LDPC is so important to the future of low-cost SSDs.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

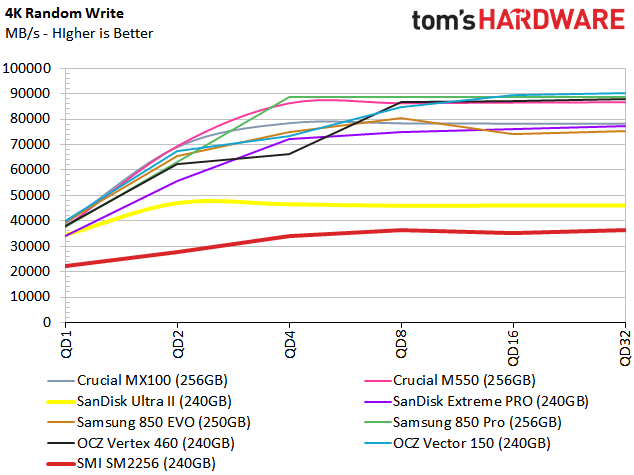

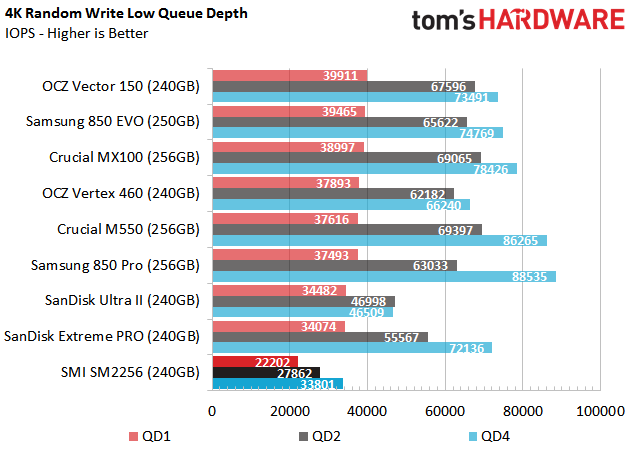

4KB Random Write Performance

Our sample also falls toward the bottom of our random write performance results.

Current page: Four-Corner Performance Testing

Prev Page A Closer Look At Silicon Motion's SM2256 Next Page Mixed Workload And Steady State Testing

Chris Ramseyer was a senior contributing editor for Tom's Hardware. He tested and reviewed consumer storage.

-

Maxx_Power I hope this doesn't encourage manufacturers to use even lower endurance NAND in their SSDs.Reply -

InvalidError Reply

It most likely will. Simply going from 20-22nm TLC to 14-16nm will likely ensure that with smaller trapped charge, increased leakage, more exotic dielectric materials to keep the first two in check.15495485 said:I hope this doesn't encourage manufacturers to use even lower endurance NAND in their SSDs. -

unityole this is the way where we are heading, only thing to get good grade SSD is probably to spend big. good grade as in HET MLC flash and pcie 3.0 performance.Reply -

alextheblue As long as they don't corrupt data, I'm not really freaking out over endurance. When a HDD died, that was a major concern. If an SSD that's a few years old starts to really reach the end of its useful life, as long as I can recover everything and dump it onto a new drive, I'm happy.Reply

If you have a really heavy workload though, by all means get a high-end unit. -

JoeMomma I am using a small ssd for Windows that is backup weekly. Saved my butt last week. Speed is key. I can provide my own reliability.Reply -

jasonkaler Here's an idea:Reply

While they're making 3d nand, why don't they add an extra layer for parity and then use the raid-5 algorithm?

e.g. 8 layers for data, adding 1 extra for parity. Not that much extra overhead, but data will be much more reliable. -

InvalidError Reply

SSD/MMC controllers already use FAR more complex and rugged algorithms than plain parity. Parity only lets you detect single-bit errors. It only allows you to "correct" errors if you know where the error was, such as a drive failure in a RAID3/5 array. If you want to correct arbitrary errors without knowing their location beforehand, you need block codes and those require about twice as many extra bits as the number of correctable bit-errors you want to implement. (I say "about twice as many" because twice is the general requirement for uncorrelated, non-deterministic errors. If typical failures on a given media tend to be correlated or deterministic, then it becomes possible to use less than two coding bits per correctable error.)15517825 said:Here's an idea:

While they're making 3d nand, why don't they add an extra layer for parity and then use the raid-5 algorithm?

e.g. 8 layers for data, adding 1 extra for parity. Not that much extra overhead, but data will be much more reliable.

-

jasonkaler Reply15519330 said:

SSD/MMC controllers already use FAR more complex and rugged algorithms than plain parity. Parity only lets you detect single-bit errors. It only allows you to "correct" errors if you know where the error was, such as a drive failure in a RAID3/5 array. If you want to correct arbitrary errors without knowing their location beforehand, you need block codes and those require about twice as many extra bits as the number of correctable bit-errors you want to implement. (I say "about twice as many" because twice is the general requirement for uncorrelated, non-deterministic errors. If typical failures on a given media tend to be correlated or deterministic, then it becomes possible to use less than two coding bits per correctable error.)15517825 said:Here's an idea:

While they're making 3d nand, why don't they add an extra layer for parity and then use the raid-5 algorithm?

e.g. 8 layers for data, adding 1 extra for parity. Not that much extra overhead, but data will be much more reliable.

No you don't. Each sector has CRC right?

So if the sector read fails CRC, simply calculate CRC replacing each layer in turn with the raid parity bit.

All of them will be off except for one with the faulty bit.

And these CRC's can all be calculated in parallel so there would be 0 overhead with regard to time.

Easy huh?

-

InvalidError Reply

If you know which drive/sector is bad thanks to a read error, your scheme is needlessly complicated: you can simply ignore ("erase") the known-bad data and calculate it by simply XORing all remaining volumes. But you needed the extra bits from the HDD's "CRC" to know that the sector was bad in the first place.15536005 said:No you don't. Each sector has CRC right?

So if the sector read fails CRC, simply calculate CRC replacing each layer in turn with the raid parity bit.

All of them will be off except for one with the faulty bit.

And these CRC's can all be calculated in parallel so there would be 0 overhead with regard to time.

Easy huh?

In the case of a silent error though, which is what you get if you have an even-count bit error when using parity alone, you have no idea where the error is or even that there ever was an error in the first place. That's why more complex error detection and correction block codes exist and are used wherever read/receive errors carry a high cost, such as performance, reliability, monetary cost or loss of data. -

Eggz I know this article was about the SM2256, but the graphs really made the SanDisk PRO shine bright! In the latency tests, which content creators care about, nothing seemed to phase it, doing better than even the 850 Pro - consistently!Reply

BUT, one significant critique I have was the density limitation. Everything here was based on the ~250 GB drives. Comparing a drive with the exact name, but in a different density, is akin to comparing two entirely different drives.

I realize producing the data can be time consuming, but having the same information at three density points would be extremely helpful for purchasing decisions - lowest, highest, and middle densities.