Alphawave develops 3nm UCIe chiplet IP for die-to-die connectivity

An industry first.

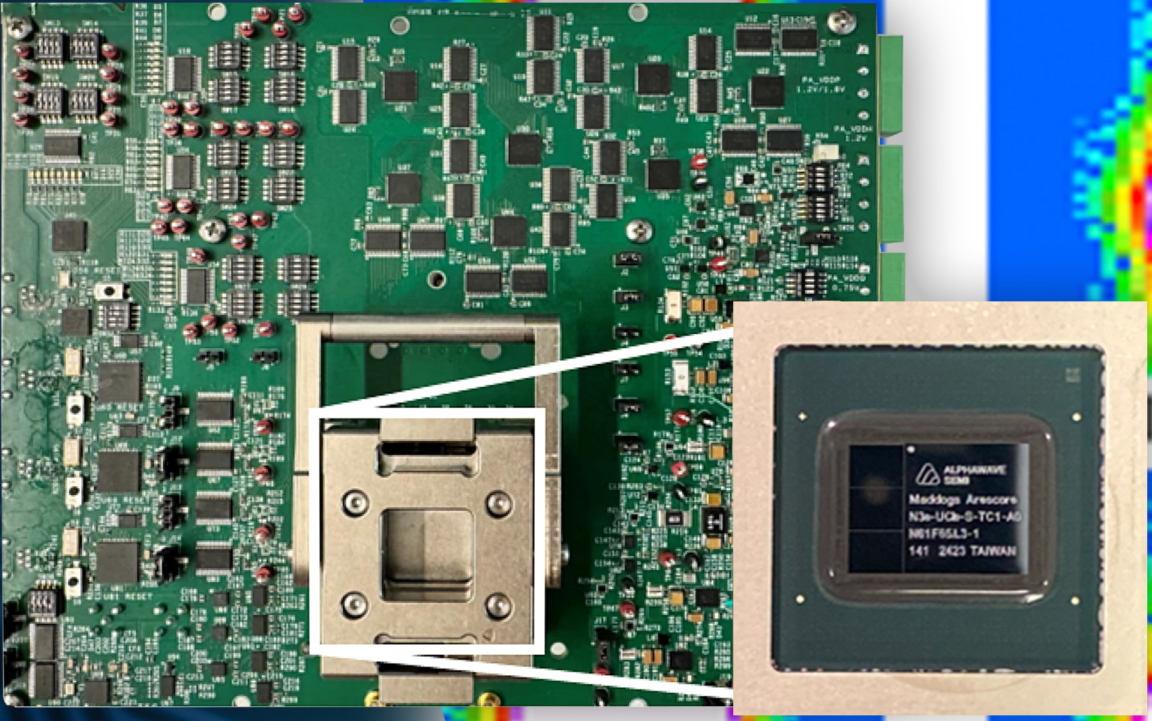

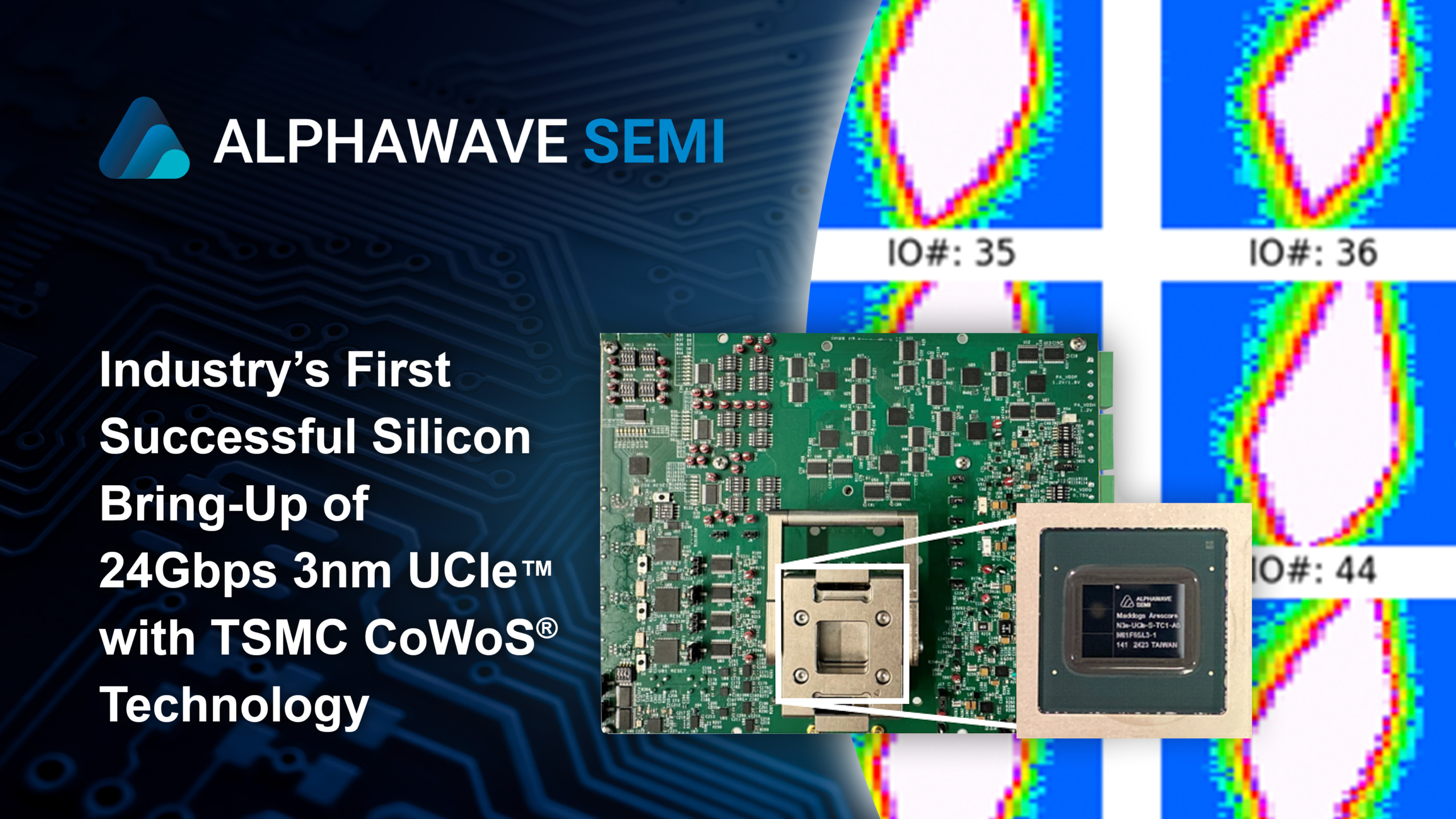

Alphawave Semi, an IP and contract chip designer, has developed the industry's first 3nm UCIe chiplet that enables die-to-die connectivity for system-in-packages made on TSMC's chip-on-wafer-on-substrate (CoWoS) packaging technology. The chiplet targets high-demand sectors such as hyperscalers, HPC, and AI, and allows users to build a wide range of system-in-packages (SiPs).

"Achieving successful silicon bring-up of 3nm 24 Gbps UCIe subsystem with TSMC's advanced packaging is a significant milestone for Alphawave Semi and underscores the company's expertise in utilizing the TSMC 3DFabric ecosystem to deliver top-tier connectivity solutions," said Mohit Gupta, Alphawave Semi’s SVP and GM of Custom Silicon and IP.

Although the 3nm chiplet can be used separately to connect UCIe 1.1-compliant chiplets, the main purpose of the IP is to be integrated into other chiplets to enable die-to-die connectivity by either Alphawave Semi (for its customers) or companies licensing the IP. The silicon-proven 3nm die-to-die interface IP is a big deal for the market as it allows for the building of multi-chiplet SiPs, implemented using TSMC's most advanced fabrication process to date.

Since TSMC's N3 production nodes are expensive to use, disaggregation of large monolithic designs is a good way to improve yields — and this is where Alphawave's silicon-proven 3nm die-to-die interface IP comes into play. Compatibility with TMSC's CoWoS is an important capability for the IP.

The 3nm chiplet supports a bandwidth density of 8 Tbps/mm and targets TSMC's CoWoS 2.5D silicon-interposer-based packaging — the same packaging that Nvidia uses for its Hopper H100 and next-generation Blackwell B100 and B200 GPUs for AI and HPC applications. Alphawave Semi's UCIe chiplet subsystem packs both PHY and controller IP, and supports a wide range of protocols — including streaming, PCIe, CXL, AXI-4, AXI-S, CXS, and CHI. The chiplet can connect a variety of 3nm components in a SiP.

Alphawave Semi's UCIe subsystem IP adheres to the most recent UCIe Specification Rev 1.1 and is equipped with extensive testing and debugging features, including JTAG, BIST, DFT, and Known Good Die (KGD) functionalities. Another standout feature of this IP is its ability to monitor lane health in real-time — which greatly enhances SiP's robustness.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.