TSMC won't adopt advanced High-NA EUV chipmaking tools until 2030 or later — Intel just received its first tool this week: Report

TSMC is in no rush to adopt ASML's High-NA EUV for mass production.

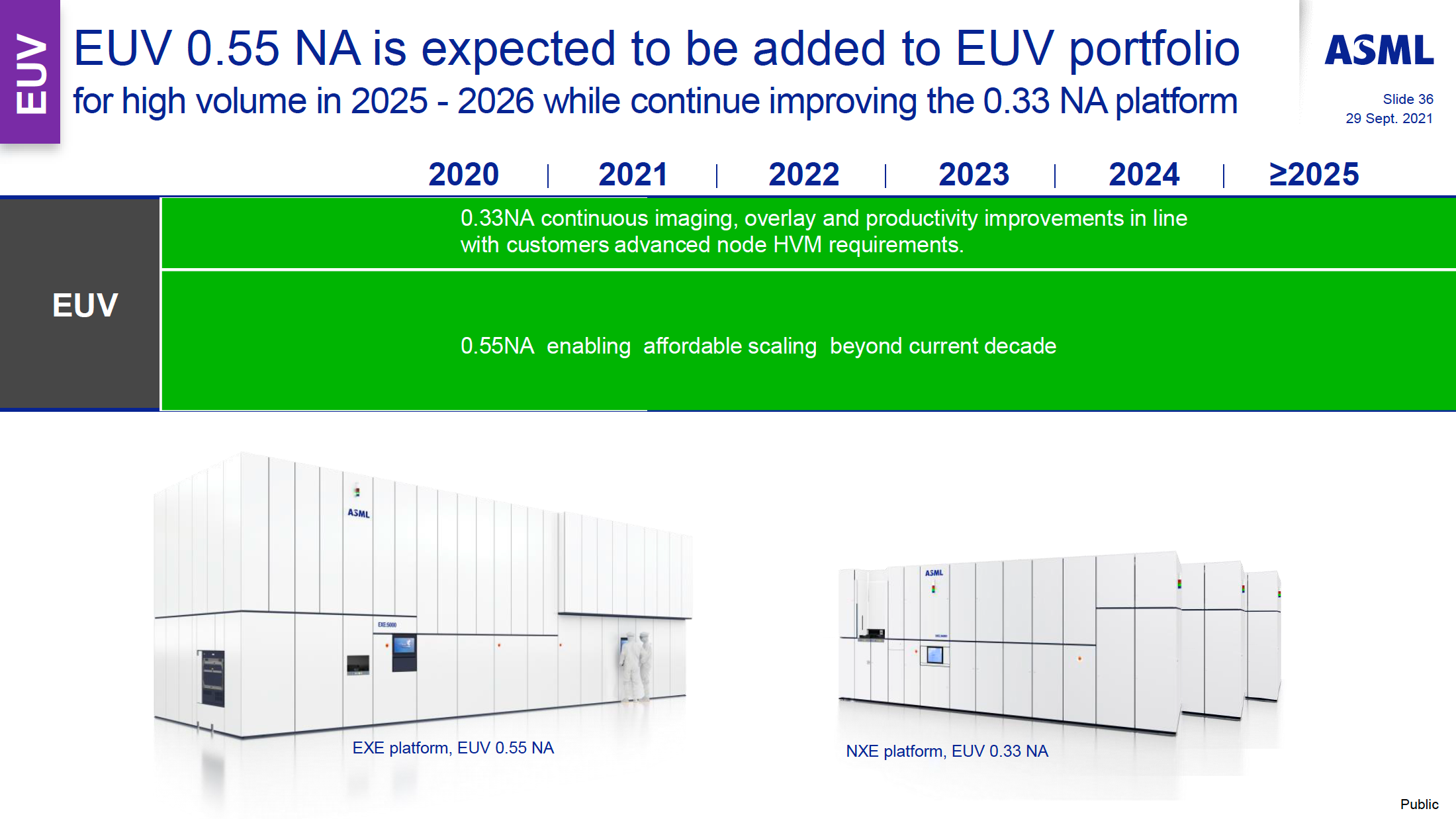

This week, Intel began to receive its first ASML's extreme ultraviolet (EUV) lithography tool with a 0.55 numerical aperture (High-NA), which it will use to learn how to use the technology before deploying the machines for a post-18A production node in the next couple of years or so. By contrast, TSMC is in no rush to adopt High-NA EUV any time soon, and it might be years before the company jumps on this bandwagon in 2030 or beyond, according to analysts from both China Renaissance and SemiAnalysis.

"In contrast to Intel's use of High-NA EUV soon after its shift to GAA (planned for [20A] insertion), we expect TSMC'sHigh-NA EUV insertion in the post N1.4 era (the inflection likely at N1, scheduled for post-2030 launch)," wrote Szeho Ng, an analyst with China Renaissance.

Intel's aggressive process technology roadmap includes the insertion of RibbonFET gate-all-around (GAA) transistors and PowerVia backside power delivery network (BSPDN) starting from 20A (20 angstroms, 2nm-class), then refining them with 18A, and then start using High-NA EUV tools for a post-18A node to offer the power, performance, and area characteristics and the lowest cycle time.

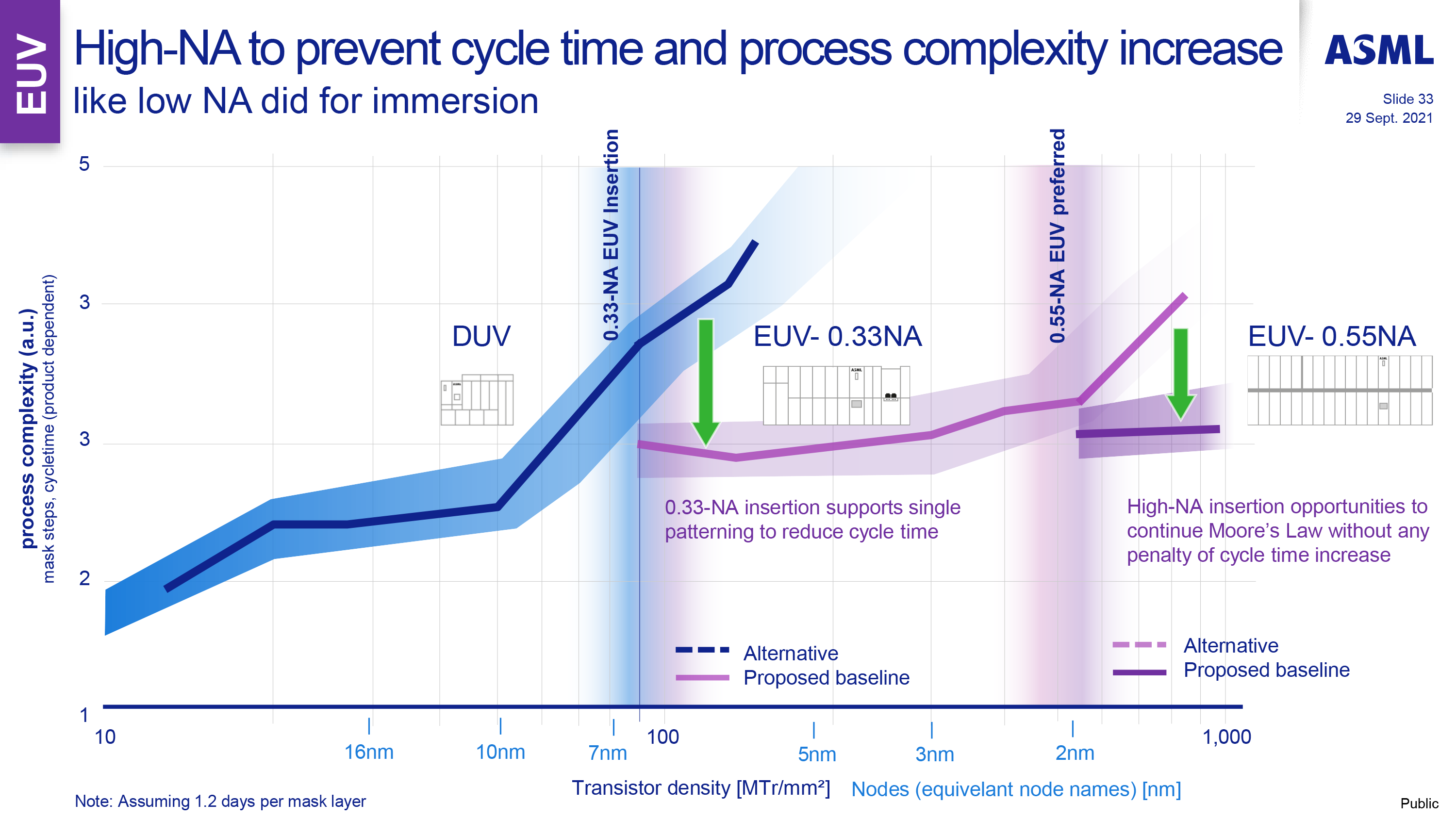

Modern EUV litho tools equipped with 0.33 numerical aperture lenses (Low-NA) provide an achievable critical dimension in the range of 13 to 16 nm for mass production, which is sufficient to produce a minimum metal pitch of 26 nm, and an estimated 25 to 30 nm tip-to-tip interconnect space pitch using single exposure patterning. This is sufficient for a 3nm-class process technology (with metal pitches between 21 and 24nm), but at 2nm and beyond, metal pitches will shrink to about 18–21nm (according to imec), which will call for the usage of EUV double patterning, pattern shaping equipment, or High-NA single patterning.

Intel plans to insert pattern shaping starting from 20A (which is about to enter HVM) and then High-NA EUV starting from a post-18A node, enabling the company to reduce the complexity of its process flow and avoid the usage of EUV double-patterning. However, High-NA EUV litho tools are significantly more expensive than Low-NA EUV scanners, but the High-NA EUV has many peculiarities, including a 2x reduced exposure field.

As a result, analysts from SemiAnalysis and China Renaissance believe that usage of High-NA EUV machines may be costlier than usage of Low-NA EUV double patterning, at least initially, which is why TSMC might not be inclined to use it for a while to ensure low costs albeit at the cost of production complexities and perhaps lower transistor density.

“Low-NA EUV multiple patterning, despite lower throughput on more exposure passes, may still cost less than high-NA EUV in the initial GAA foray; the higher source power of high-NA EUV to drive finer CD (critical dimension) speeds up wear on projection optics and photomasks, outweighing higher throughput benefits,” explained Szeho Ng. “This ties with TSMC’s practice to target the volume market with the most cost-competitive technologies.”

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

TSMC began to use extreme ultraviolet (EUV) lithography tools for high-volume production of chips in 2019, months after Samsung Foundry but years before Intel. Intel wants to be ahead of Samsung Foundry and TSMC with High-NA EUV, which could ensure some tactic and strategic benefits. The only question is, will TSMC be able to maintain its process technology leadership if it adopts High-NA litho only in 2030 or later (i.e., four to five years after Intel)?

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

thestryker If they're talking ready for production in 2030 I could almost buy into that, but if they're talking not acquiring until then that doesn't seem likely. I don't think relying on Apple to subsidize all of their new nodes is a viable strategy with Intel being as aggressive as they are. It's not unreasonable to believe that Intel could be competing 1:1 and be able to offer an equivalent node for less money by 2030.Reply -

Co BIY TSMC may also be looking at the availability of machines and wants to avoid a bidding war with Intel that would only benefit ASML.Reply

If they think they have a lot of mileage left in their current processes I can see this as a smart conservative strategy. -

hannibal Reply

Sounds sensible. New smaller nodes are nice, but not at any cost…Co BIY said:TSMC may also be looking at the availability of machines and wants to avoid a bidding war with Intel that would only benefit ASML.

If they think they have a lot of mileage left in their current processes I can see this as a smart conservative strategy. -

gg83 Has Intel always adopted the latest machines from asml first? Do we know who is likely to buy intels first gen of they're latest nodes? Is it government?Reply -

bit_user Reply

No. TSMC was first to adopt EUV.gg83 said:Has Intel always adopted the latest machines from asml first?

It was previously reported that Intel co-developed high-NA in partnership with ASML. I think this gave Intel a window of exclusivity.

Huh? Which nodes? They have made some announcements of different commercial customers lined up to use some of their nodes, but I haven't been keeping track. I don't recall hearing about any government (contractor) customers, but I'm not sure if those would be announced.gg83 said:Do we know who is likely to buy intels first gen of they're latest nodes? Is it government?

It does raise an interesting question of what chips & nodes might be getting eyed/used for things like autonomous weapons. They can't go with mil-spec parts, because those simply lack the compute density & power efficiency. So, they must be looking at/using fairly cutting-edge nodes. That brings us to the next question of what sort of architecture these chips have. Do they just license some DSP cores from Cadence, Synopsis, etc. and fab a big die with some HBM around it? Who even are the big chip contractors who might do it? -

phead128 Reply

Intel has access to the same EUV tools that TSMC has all this time. If they could match 1:1 to TSMC, they should prove it with existing nodes.thestryker said:It's not unreasonable to believe that Intel could be competing 1:1 and be able to offer an equivalent node for less money by 2030. -

thestryker Reply

Nothing you've said here makes any sense at all. Maybe you just don't know about how the fabrication industry has operated?phead128 said:Intel has access to the same EUV tools that TSMC has all this time. If they could match 1:1 to TSMC, they should prove it with existing nodes.

Intel opted to move forward with 10nm (which has similar density to TSMC N7, and originally. was supposed to be even more) on DUV which means they bought no EUV machines until years after TSMC did. Based on what public information is available Intel 7 costs more than Intel 4 due to a the hoops required to use DUV.

They've gotten EUV machines and are putting them to use with Intel 4 for MTL right now with Intel 3 and 20A later this year which should get them to parity with TSMC. They won't be any cheaper than TSMC and if using RibbonFET and PowerVia they will be more expensive since they're using the same equipment.

They're installing High-NA now to get a jump on learning to implement usage and should be aimed at post 18A nodes though High-NA machines should be able to process more wafers than existing EUV machines.

ASML has been backlogged on EUV machines since they were introduced and High-NA is even worse. Intel has chosen to move forward quickly to maximize their fabrication throughput while ensuring they can minimize costs. -

gg83 Replybit_user said:No. TSMC was first to adopt EUV.

It was previously reported that Intel co-developed high-NA in partnership with ASML. I think this gave Intel a window of exclusivity.

Huh? Which nodes? They have made some announcements of different commercial customers lined up to use some of their nodes, but I haven't been keeping track. I don't recall hearing about any government (contractor) customers, but I'm not sure if those would be announced.

It does raise an interesting question of what chips & nodes might be getting eyed/used for things like autonomous weapons. They can't go with mil-spec parts, because those simply lack the compute density & power efficiency. So, they must be looking at/using fairly cutting-edge nodes. That brings us to the next question of what sort of architecture these chips have. Do they just license some DSP cores from Cadence, Synopsis, etc. and fab a big die with some HBM around it? Who even are the big chip contractors who might

I found an article from 2022 stating all the latest AI- enabled chips are exclusively coming from TSMC plants in Taiwan. I'm interested now. I'll try do find out what happens after the wafer is made.bit_user said:No. TSMC was first to adopt EUV.

It was previously reported that Intel co-developed high-NA in partnership with ASML. I think this gave Intel a window of exclusivity.

Huh? Which nodes? They have made some announcements of different commercial customers lined up to use some of their nodes, but I haven't been keeping track. I don't recall hearing about any government (contractor) customers, but I'm not sure if those would be announced.

It does raise an interesting question of what chips & nodes might be getting eyed/used for things like autonomous weapons. They can't go with mil-spec parts, because those simply lack the compute density & power efficiency. So, they must be looking at/using fairly cutting-edge nodes. That brings us to the next question of what sort of architecture these chips have. Do they just license some DSP cores from Cadence, Synopsis, etc. and fab a big die with some HBM around it? Who even are the big chip contractors who might do it? -

ToBeGood Reply

Sound totally non-sense.hannibal said:Sounds sensible. New smaller nodes are nice, but not at any cost…

The real reason why TSMC fire its Chair is not because of US FAB, this delay is the No1 reason why he is sacked.

https://www.cnbc.com/2022/03/23/inside-asml-the-company-advanced-chipmakers-use-for-euv-lithography.html

If TSMC N3B can have good yield and not leading to N3E reduced double patterning and increase in size (i.e. N3B is better than N3E (going backward)).

A third grade can do the maths i.e. you +- double the amount of cost i.e. 2 Vs 1 exposure and the cost of the machine is 200M Vs 300M, so EUV high NA increase 50% but it reduced the exposure cost by 100% so that is a 50% cost gain by switching to the new machine, and on top of that EUV High NA reduced the risk of reducing yield cause by mis-algin double patterning.

You call this sensible please do your math because yada yeda yeda fanboy. -

cyrusfox Reply

Double patterning does not require double exposure... Only if you need to rework, and that is the same for any litho step whether pattern multiplication processes are used or not.ToBeGood said:If TSMC N3B can have good yield and not leading to N3E reduced double patterning and increase in size (i.e. N3B is better than N3E (going backward)).

A third grade can do the maths i.e. you +- double the amount of cost i.e. 2 Vs 1 exposure and the cost of the machine is 200M Vs 300M, so EUV high NA increase 50% but it reduced the exposure cost by 100% so that is a 50% cost gain by switching to the new machine, and on top of that EUV High NA reduced the risk of reducing yield cause by mis-algin double patterning.

You call this sensible please do your math because yada yeda yeda fanboy.

The higher cost comes from the subsequent processing needed to reduce the line feature size (Etch/trim, oxide dep, etch/resist clean, and final etch/dep)

The increased processing adds additional complexity (Defects and margin for error). But does not increase Litho tool utilization or need for additional exposure. The design is a bit trickier in terms of routing, but vias and inventive design can solve that.

As for TSMC strategy whether disputed now or not seems to be the course they are on. A supportive point to their strategy is everyone(Memory makers, Samsung, TSMC, Global, Intel, etc) was able to progress with DUV past 39nm(limit of DUV) with these tricks for nearly a decade, When TSMC is at the wall of what EUV can accomplish without patterning tricks, there should still be plenty of mileage to get them another 4-5 years, and it might be the cost optimized route with how out of hand Litho BOM has became in Semiconductor Fabrication. Although it may give Intel the lead again in node advancement(Intel should have an easier way of achieving smaller features and do so faster), but at what price?