UCIe 2.0 specifications standardize management architecture and 3D packaging across different chiplets

UCIe 2.0 is for multi-vendor 3D chiplet designs.

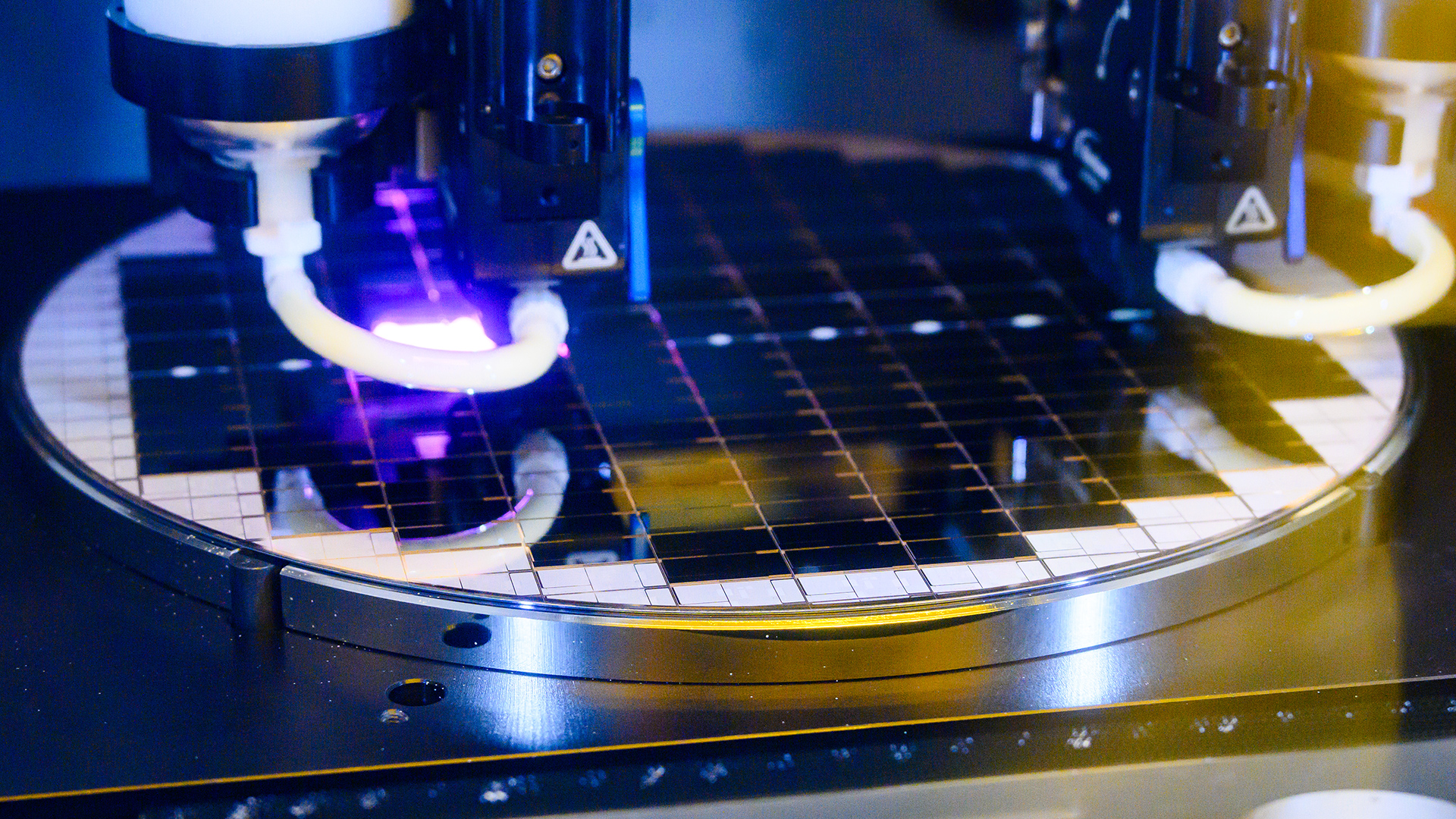

The UCIe Consortium on Wednesday released version 2.0 of the UCIe specification, which brings support for standardized management of system architecture across different chiplets and support for industry-standard 3D packaging of chiplets with hybrid bonding and bump pitches of variable sizes. The new specification makes it easier to develop, build, and manage system-in-packages (SiP) containing chiplets from different vendors.

For now, SiPs with UCIe chiplets have to use multiple management frameworks for each chiplet if they use chiplets from more than one vendor. The UCIe 2.0 specification introduces a standardized manageability system architecture that addresses manageability, testability, and debugging (Dfx) across multiple chiplets throughout the SiP lifecycle. In addition, the new spec defines optional UCIe DFx Architecture (UDA), which integrates vendor-agnostic testing, telemetry, and debug fabric within each chiplet to simplify development and bring-up of multi-chip system-on-packages.

Another key feature of UCIe 2.0 is 3D packaging support. UCIe-3D is optimized for hybrid bonding supporting bumps that can be 1 micron or smaller, of 10 – 25 microns, to provide flexibility and scalability. To put these numbers into context: Intel's Foveros 3D technology features 36-micron bump pitches, supporting up to 770 microbumps per square millimeter and 160 GB/s per mm bandwidth. Future advancements will include 25-micron and 18-micron micro bumps — significantly increasing interconnection densities. UCIe-3D will support densities well beyond those currently envisioned by chipmakers; the specification is meant for long-term use.

Article continues belowFinally, the UCIe 2.0 specification includes optimized package designs to ensure interoperability and effective compliance testing. The purpose of compliance testing is to verify the main-band supported features of a Device Under Test (DUT) against a known-good reference UCIe implementation. This specification sets up an initial framework for testing physical components, adapters, and protocols.

"UCIe Consortium is supporting a diverse range of chiplets to meet the needs of the rapidly changing semiconductor industry," said Cheolmin Park, UCIe Consortium President and Corporate VP of Samsung. "The UCIe 2.0 Specification builds on previous iterations by developing a comprehensive solution stack and encouraging interoperability between chiplet solutions. This is yet another example of the Consortium’s dedication to the flourishing open chiplet ecosystem."

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

bit_user Reply

Cool stuff, but I hope the design and implementations are very thoughtful about security. If not, I shudder to think what a wealth of new attack vectors this could potentially introduce.The article said:The UCIe 2.0 specification introduces a standardized manageability system architecture that addresses manageability, testability, and debugging (Dfx) across multiple chiplets throughout the SiP lifecycle. In addition, the new spec defines optional UCIe DFx Architecture (UDA), which integrates vendor-agnostic testing, telemetry, and debug fabric within each chiplet to simplify development and bring-up of multi-chip system-on-packages.