AMD Phoenix 2 CPU Die Shot Seemingly Shows Zen 4, Zen 4c Cores

AMD's hybrid Phoenix 2 APU shows its innards.

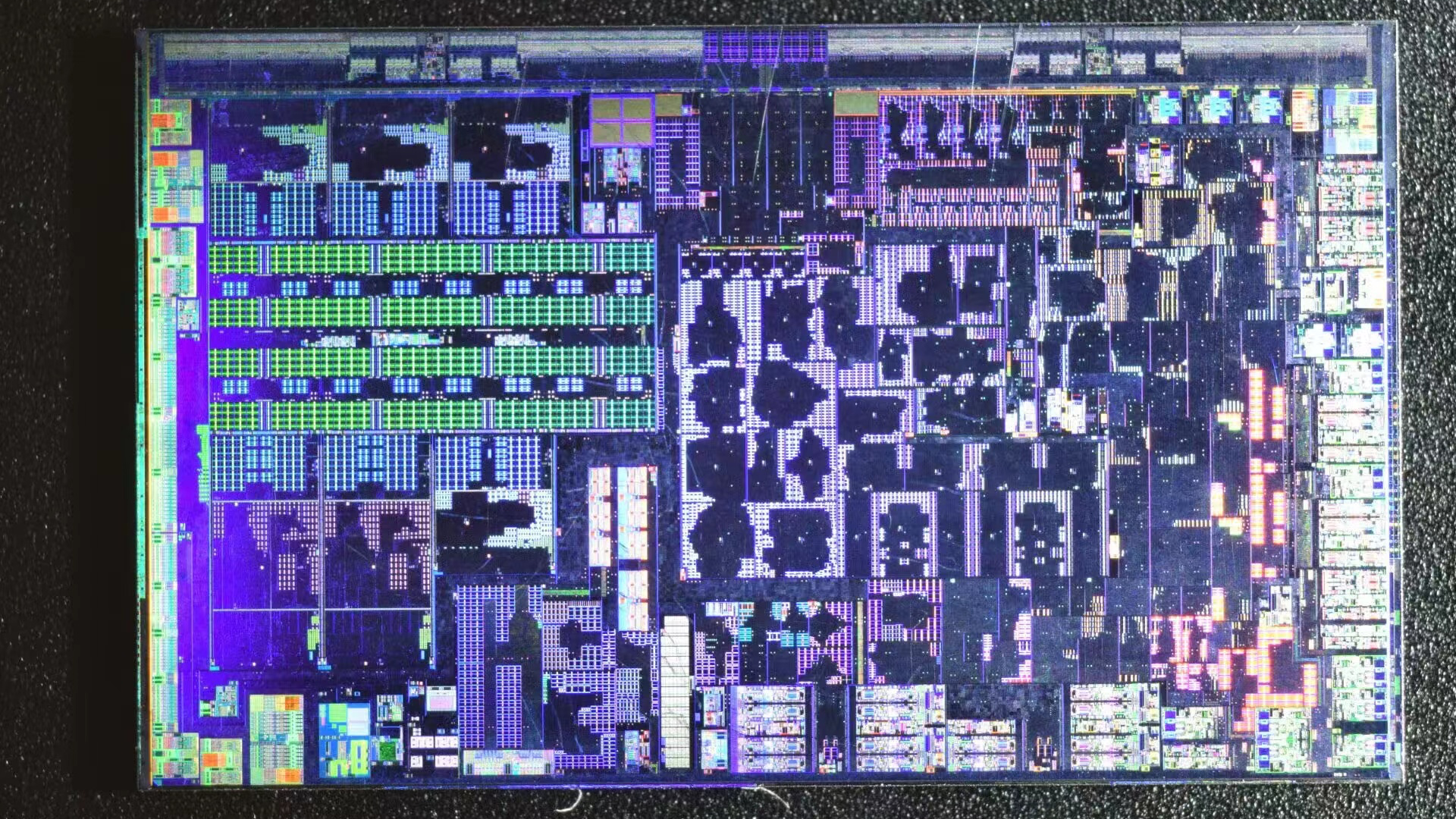

An alleged die shot of AMD’s upcoming hybrid accelerated processing unit with Zen 4 and Zen 4c general-purpose cores was published by hardware leaker HXL. The APU is expected to be the younger brother of AMD’s Phoenix and will sit below these parts in the Ryzen lineup.

The supposed Phoenix 2 processor die shot clearly shows a large L3 cache (in the middle of the left side, green structures), two high-performance Zen 4 cores (below the L3 cache), four smaller Zen 4c cores (three above L3, one to the right of Zen 2 cores), and a large built-in GPU (on the right side). In addition, there are several DDR5/LPDDR5 PHY interfaces on top of the die, as well as PCIe, USB, and other physical interfaces on the APU's bottom and left and right sides of the APU.

While AMD’s Ryzen 7040-series (Phoenix) APU carries eight high-performance Zen 4 cores, Phoenix 2 only features six cores, two high-performance Zen 4 cores, and four energy-efficient Zen 4c cores that are considerably smaller than their counterparts, which points to the fact that AMD positions Phoenix 2 as a lower-cost APU for cheaper laptops. What remains to be seen is what else AMD cut down from this chip to make it smaller and more affordable, but it looks like we will learn this when AMD officially launches these parts.

AMD's first hybrid CPU design will bolster its competitiveness against Intel's Alder Lake and Raptor Lake offerings in the laptop processor segment. By incorporating a mix of high-performance and high-efficiency cores, AMD can achieve performance metrics at power levels previously unattainable. Meanwhile, given the specifics of Zen 4c and Phoenix 2 design, it will be considerably cheaper than the original Phoenix, opening some new doors for Zen 4.

AMD's codenamed Phoenix 2 processors were expected to hit the market this year, but it is September, and we do not see this APU anywhere, so perhaps AMD decided to make it a part of its Ryzen 8000-series lineup set to arrive in 2024. Meanwhile, if AMD's Phoenix 2 comes to market in 2024, it will have to rival Intel's entry-level Meteor Lake, which is projected to be considerably more competitive than the current offerings.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

mitch074 Huh - I wasn't sure, but it does seem AMD managed to fit 2 Zen4c cores in the same area as it takes to run a single Zen4 core. With SMP support, it means they did manage to fit as many threads as Intel but without compromising instruction set support. AMD does what Intel don't.Reply -

AgentBirdnest Nice! I'm a sucker for die shots. : PReply

Is there any word on whether or not Zen4c will come to desktop? My biggest complaint about my current (and previous) AMD CPU is the idle and low-load power draw. If C-cores can improve that, while the regular cores keep their power efficiency with heavy loads, it would be an awesome hybrid. -

DaveLTX Reply

Yes. Look at EPYC Bergamo. 2 Zen 4c in nearly Zen 4 area.mitch074 said:Huh - I wasn't sure, but it does seem AMD managed to fit 2 Zen4c cores in the same area as it takes to run a single Zen4 core. With SMP support, it means they did manage to fit as many threads as Intel but without compromising instruction set support. AMD does what Intel don't. -

DaveLTX Reply

Actually it's a lot to do with optimization. The cpu cores reach deep sleep into basically 0-0.1W each. While the IOD is the one drawing over 10W. However not really much and the same design is now in laptops with lower idle power.AgentBirdnest said:Nice! I'm a sucker for die shots. : P

Is there any word on whether or not Zen4c will come to desktop? My biggest complaint about my current (and previous) AMD CPU is the idle and low-load power draw. If C-cores can improve that, while the regular cores keep their power efficiency with heavy loads, it would be an awesome hybrid.

Wouldn't work in laptops if the IOD drew 10W. And not to forget, IOD power is exponential with dram speed, try undervolting the IOD as far as you can, the new bioses allow for either higher speed 1:1 IF or lower voltage at iso frequency -

bit_user Reply

Does anyone know if a Phoenix-based APU is slated for AM5? That might be noticeably more efficient than other AM5 options.AgentBirdnest said:Is there any word on whether or not Zen4c will come to desktop? My biggest complaint about my current (and previous) AMD CPU is the idle and low-load power draw.

You can also go for one of the non-X (i.e. 65 W) AM5 CPUs, or just cap the TDP of one of the X-series CPUs in BIOS. -

usertests I heard that Phoenix 2 won't have the AI accelerator. That seems like a mistake. If it's trying to "rival entry-level Meteor Lake", I'm guessing the MTL 2+8 die will include the accelerator used in the bigger dies.Reply

Don't @ me with "but nobody uses it" or something. These are in every smartphone and will probably be in almost every new x86 chip within 2-3 years, including desktop.

If Agent wants low idle power, the hypothetical Phoenix APU is going to be loads better for that, since it's monolithic and optimized for battery power.bit_user said:Does anyone know if a Phoenix-based APU is slated for AM5? That might be noticeably more efficient than other AM5 options.

You can also go for one of the non-X (i.e. 65 W) AM5 CPUs, or just cap the TDP of one of the X-series CPUs in BIOS.

I don't think we have gotten great leaks on Phoenix desktop APUs, but I assume the matter will be resolved for anyone who can wait another 6 months. -

bit_user Reply

I agree with you - Ryzen AI is a forward-looking feature, assuming the implementation is as good as they claim. It's not there for what it accelerates today, so much as what it can enable tomorrow.usertests said:I heard that Phoenix 2 won't have the AI accelerator. That seems like a mistake. If it's trying to "rival entry-level Meteor Lake", I'm guessing the MTL 2+8 die will include the accelerator used in the bigger dies.

Don't @ me with "but nobody uses it" or something. These are in every smartphone and will probably be in almost every new x86 chip within 2-3 years, including desktop.

3D graphics didn't used to be an essential feature, but now it's become so ubiquitous that it's become mandatory. Video codec acceleration is pretty much like that, too - especially in phones & laptops. AI accelerators will likely tread the same path. -

Gillerer Reply

Much of the area savings on Bergamo are from not increasing the amount L3 cache per CCD (so halving it per core), while using a the HPC variant of TSMC N5 that allows for denser logic and cache (but limits speeds of each).DaveLTX said:Yes. Look at EPYC Bergamo. 2 Zen 4c in nearly Zen 4 area. -

bit_user Reply

No, the process node didn't change!Gillerer said:Much of the area savings on Bergamo are from not increasing the amount L3 cache per CCD (so halving it per core), while using a the HPC variant of TSMC N5 that allows for denser logic and cache (but limits speeds of each).

Semianalysis did a thorough breakdown of Zen 4c - they looked at the relative sizes between it and Zen 4 and what key changes enabled the area reductions.

"AMD created Zen 4c by taking the exact same Zen 4 Register-Transfer Level (RTL) description, which describes the logical design of the Zen 4 core IP, and implementing it with a far more compact physical design. The design rules are the same as both are on TSMC N5, yet the area difference is massive. We detail the three key techniques of device Physical Design that enables this."

"lowering the clock target of a design can lead to reduced area when the core is synthesized."

"flatter design hierarchy with fewer partitions."

"The final method of area reduction is by using denser memory. Zen 4c has a reduction in SRAM area within the core itself, as AMD has switched to using a new type of SRAM bitcell."

Source: https://www.semianalysis.com/p/zen-4c-amds-response-to-hyperscale?utm_source=%2Fsearch%2Fzen%25204c

They go into quite a bit more detail about each of those points, so do take a look, if you're so inclined.

-

annymmo Why not put all the L3 cache on the IOD and use the extra space on the core chiplets for lots of big cores with more L1 and L2 cache memory?Reply

(The larger L1 and especially L2 caches are to compensate for the higher latency of the L3 cache memory being on another chiplet.)

Why is AMD not taking such an approach?

Would love a processor with a single core-focused chiplet housing 16 big cores and an IO die chiplet with 64 or even 128 MB L3 planar/flat cache memory (and iGPU).